Projektanci mają wiele ścieżek różnicowania rozwiązań RISC-V. Jedna ścieżka prowadzi do różnych dostosowań i rozszerzeń rdzenia RISC-V zgodnie ze specyfikacją. Inny skupia się na wyborze i składaniu bloków IP w kompletny projekt typu system-on-chip (SoC) wokół jednego lub większej liczby rdzeni RISC-V. Pojawia się trzeci: łączenie rdzeni RISC-V i innych bloków IP za pomocą sieci na chipie (NoC) zamiast prostej struktury magistrali. I to nie tylko z najwyższej półki – połączenie rdzeni RISC-V z NoC odpowiada na wiele wyzwań projektowych SoC, w których dane muszą przepływać efektywnie przy dowolnym obciążeniu przy użyciu dowolnego protokołu na chipie.

Poziomy wydajności zmieniają się wraz z zaawansowanymi schematami połączeń wzajemnych

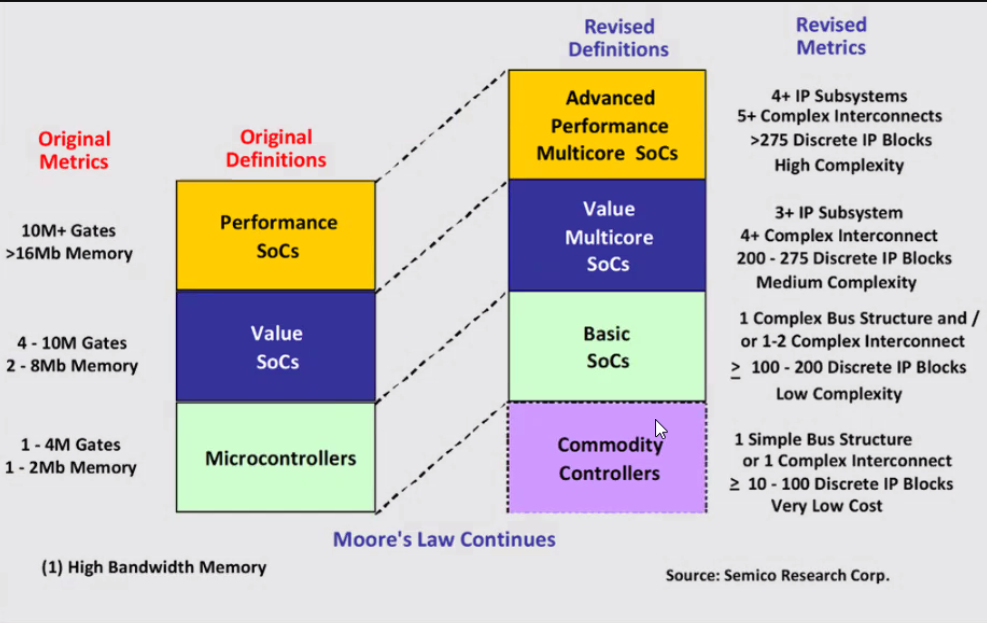

Samo liczenie bramek, rdzeni i bloków peryferyjnych nie opisuje już potencjału wydajnościowego projektu SoC. Według Semico Research schematy połączeń wzajemnych definiują obecnie granice między poziomami wydajności SoC, a także otworzył się nowy poziom, w którym połączenia wzajemne zmieniają się z prostych struktur magistrali na bardziej wyrafinowane schematy.

Zaktualizowana definicja Semico uwzględnia trzy czynniki: wszechobecność projektów wielordzeniowych, wyższą poprzeczkę dla tego, co jest uważane za złożony projekt, oraz wynikającą z tego zacierającą się granicę między „mikrokontrolerem” a „SoC”. Według najnowszego poglądu Semico pojęcie liczby bramek jako metryki zanika, ponieważ jeden nowoczesny rdzeń procesora może ciągnąć ze sobą wiele bramek. Złożoność staje się funkcją połączeń wzajemnych, różniącą się w zależności od podsystemów i różnych bloków IP.

Poziomy wydajności SoC, zdjęcie dzięki uprzejmości Semico Research Corp.

Tam, gdzie wystarczy prosta magistrala, prawdopodobnie część z jednym rdzeniem procesora i urządzeniami peryferyjnymi o niskim cyklu pracy, które nie rywalizują w sposób ciągły o magistralę, Semico widzi poziom kontrolera towarowego. Wszystko powyżej staje się SoC, prawdopodobnie z przynajmniej niektórymi urządzeniami peryferyjnymi walczącymi o przepustowość chipa i uwagę rdzenia procesora. Wyższe poziomy SoC mają wiele rdzeni i wiele podsystemów IP, każdy z dostosowaną technologią połączeń wzajemnych.

NoC korzystają z większej liczby protokołów i podsystemów

RISC-V szybko przesunął się w górę tych poziomów wydajności, gdy pojawiły się mocniejsze rdzenie, z nie mniejszym zakresem zastosowania w dolnym końcu skali Semico. Jednakże projektanci RISC-V mogą mieć mniejsze doświadczenie w złożonych schematach połączeń wzajemnych spotykanych na wyższych poziomach. „TileLink może być pierwszą myślą w przypadku interkonektu RISC-V, ale jego użycie w bardziej złożonych scenariuszach może być trudne” – mówi Frank Schirrmeister, wiceprezes ds. rozwiązań i rozwoju biznesu w firmie Arteris.

Supermocą NoC jest jego zdolność do łączenia podsystemów przy użyciu różnych protokołów, a projektanci SoC prawdopodobnie natkną się na kilka protokołów nawet o umiarkowanej złożoności. AXI wyrównało szanse dla prostych połączeń blokowych IP. Rozwiązania wielordzeniowe z blokami współprzetwarzania wymagają spójności pamięci podręcznej, co daje początek protokołowi CHI. Współdzielenie pamięci we/wy pomogło w ukształtowaniu szybszego połączenia międzysieciowego CXL. „Kiedy nadchodzi czas wspólnej optymalizacji obliczeń i transportu przy użyciu różnych podsystemów i protokołów, lepszym rozwiązaniem jest NoC” – kontynuuje Schirrmeister.

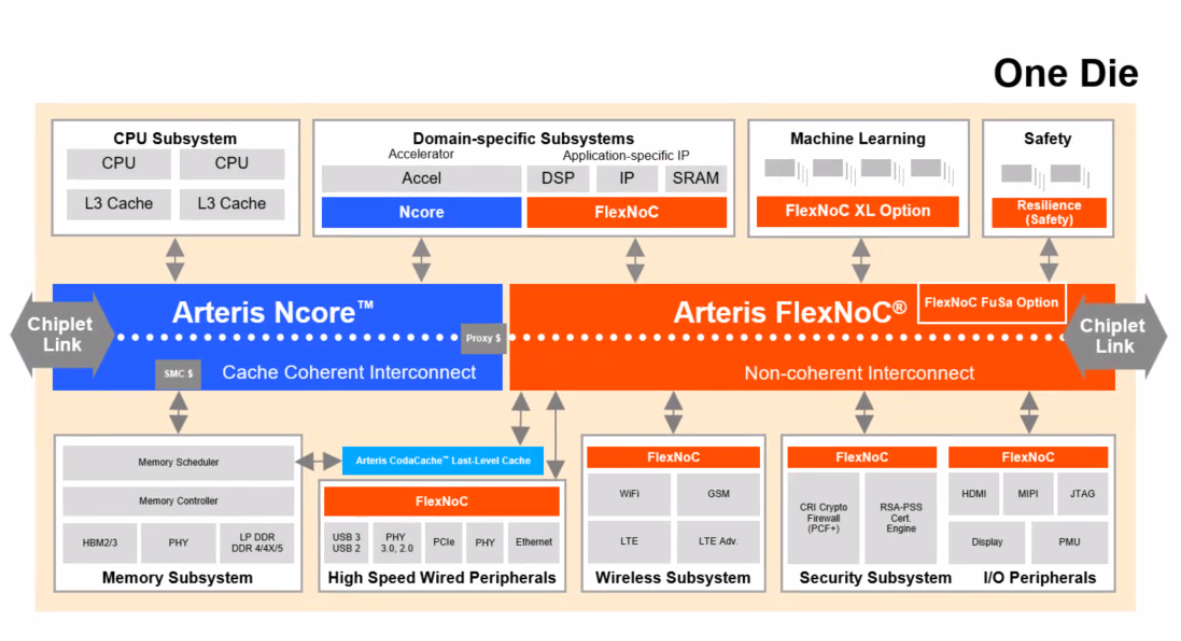

Jak może wyglądać parowanie rdzeni RISC-V z NoC? Klient Arteris, Tenstorrent, zapewnia wgląd w możliwości. Ostatnio skupili się na stworzeniu chipletu wielokrotnego użytku łączącego rdzenie RISC-V, protokół IP przyspieszający uczenie maszynowe i standardowe urządzenia peryferyjne stosowane w wielu aplikacjach sztucznej inteligencji na krawędzi. W skali implementacja z jednym układem mogłaby wyglądać jak na poniższym schemacie, z wykorzystaniem spójnego połączenia międzysystemowego Arteris Ncore i kilku segmentów niespójnego połączenia międzysieciowego Arteris FlexNoC.

zdjęcie dzięki uprzejmości Arteris

Inteligentny kontroler pamięci (SMC) zapewnia wysokowydajne połączenie pamięci klasy serwerowej w aplikacjach intensywnie korzystających z pamięci. Nienazwanym „łączem chipsetów” może być UCIe, stosunkowo nowa specyfikacja zoptymalizowana pod kątem ściślejszej integracji chipletów. Kiedy pojawiają się nowe połączenia międzypodsystemowe, dostosowanie części NoC jest łatwiejsze w zarządzaniu niż rozrywanie całej struktury obejmującej cały chip.

Łączenie rdzeni RISC-V z NoC zmniejsza ryzyko i skraca czas wprowadzenia produktu na rynek

Jeśli ten diagram wygląda na skomplikowany i to prawda, być może większość aplikacji RISC-V nie jest obecnie aż tak skomplikowana, rozważ to: chiplety już znacznie zwiększają integrację. Dzisiejsza zaawansowana wielordzeniowa część RISC-V będzie wartościowym SoC w przyszłym roku, ponieważ innowacje nabierają tempa.

Narzędzia programistyczne Arteris Ncore i Arteris FlexNoC wyprowadzają RTL do wdrożenia, zapewniając kilka korzyści. Oszacowanie fizycznej wartości NoC jest proste w przepływie pracy EDA. Dostosowanie parametrów NoC, takich jak liczba etapów rurociągu, jest również możliwe za pomocą kilku kliknięć w narzędziach EDA. Wspomniane powyżej modyfikacje dotyczące dodania protokołu podsystemu są również łatwe do wykonania. „Najwyżsi użytkownicy uzyskują natychmiastowy dostęp do naszej specjalistycznej wiedzy dotyczącej NoC” – mówi Schirrmeister. „W ostatecznym rozrachunku nasze narzędzia są łatwe w użyciu, co gwarantuje sukces już przy pierwszym przejściu i zapewniają ścieżkę rozwoju dla bardziej ambitnych przyszłych projektów ze złożonymi połączeniami wzajemnymi”.

Łączenie rdzeni RISC-V z NoC zmniejsza ryzyko wprowadzenia do projektu jeszcze jednego bloku IP i wywołania fali przeprojektowania połączeń wzajemnych w całym chipie. Skraca także czas wprowadzenia na rynek złożonych projektów SoC w porównaniu do struktur połączeń wzajemnych typu „zrób to sam”. Nie omawialiśmy tutaj innych zalet NoC, takich jak zarządzanie przepustowością i energią, ale argumenty przemawiające za NoC w projektach RISC-V są mocne, biorąc pod uwagę różnorodną mieszankę protokołów.

Odwiedź stronę Arteris aby uzyskać więcej informacji na temat NoC i inne produkty.

Udostępnij ten post przez:

- Dystrybucja treści i PR oparta na SEO. Uzyskaj wzmocnienie już dziś.

- PlatoData.Network Pionowe generatywne AI. Wzmocnij się. Dostęp tutaj.

- PlatoAiStream. Inteligencja Web3. Wiedza wzmocniona. Dostęp tutaj.

- PlatonESG. Węgiel Czysta technologia, Energia, Środowisko, Słoneczny, Gospodarowanie odpadami. Dostęp tutaj.

- Platon Zdrowie. Inteligencja w zakresie biotechnologii i badań klinicznych. Dostęp tutaj.

- Źródło: https://semiwiki.com/ip/arteris/336086-pairing-risc-v-cores-with-nocs-ties-soc-protocols-together/

- :ma

- :Jest

- :nie

- :Gdzie

- $W GÓRĘ

- a

- zdolność

- powyżej

- przyśpieszenie

- dostęp

- realizowane

- Stosownie

- w poprzek

- dodanie

- Korekty

- zaawansowany

- Zalety

- AI

- już

- również

- ambitny

- an

- i

- Inne

- odpowiedzi

- każdy

- wszystko

- zjawić się

- aplikacje

- SĄ

- na około

- AS

- At

- Uwaga

- z dala

- przepustowość

- bar

- BE

- staje się

- Korzyści

- Ulepsz Swój

- pomiędzy

- Blokować

- Bloki

- autobus

- biznes

- rozwój biznesu

- ale

- CAN

- walizka

- wyzwania

- zmiana

- wymiana pieniędzy

- żeton

- łączenie

- towar

- w porównaniu

- kompletny

- kompleks

- kompleksowość

- obliczać

- Skontaktuj się

- połączenie

- połączenia

- Rozważać

- za

- wobec

- ciągły

- bez przerwy

- kontroler

- rdzeń

- Corp

- mógłby

- rachunkowość

- Tworzenie

- klient

- dane

- określić

- definicja

- Kreowanie

- Wnętrze

- projektanci

- projekty

- oprogramowania

- narzędzia programistyczne

- różne

- trudny

- omówione

- inny

- do

- jazdy

- każdy

- łatwo

- krawędź

- skutecznie

- wyłaniać się

- wschodzących

- zakończenia

- wprowadzenie

- Cały

- Parzyste

- doświadczenie

- ekspertyza

- rozszerzenia

- szybciej

- kilka

- pole

- walczący

- i terminów, a

- pływ

- Skupiać

- koncentruje

- następujący

- W razie zamówieenia projektu

- Siły

- znaleziono

- szczery

- od

- funkcjonować

- przyszłość

- Wzrost

- Bramy

- Dający

- Dojrzeć

- udzielony

- Wzrost

- Have

- pomógł

- tutaj

- Wysoki

- wysoka wydajność

- wyższy

- Jednak

- HTTPS

- obraz

- Natychmiastowy

- realizacja

- in

- Informacja

- Innowacja

- zamiast

- integracja

- łączenie

- interkonekty

- najnowszych

- IP

- IT

- JEGO

- właśnie

- firmy

- uruchamia

- najmniej

- mniej

- lubić

- Prawdopodobnie

- Linia

- linie

- dłużej

- Popatrz

- wygląda jak

- WYGLĄD

- niski

- niższy

- i konserwacjami

- wiele

- Maksymalna szerokość

- Może..

- może

- Pamięć

- wzmiankowany

- metryczny

- mieszać

- umiarkowanego

- Nowoczesne technologie

- Modyfikacje

- jeszcze

- większość

- przeniósł

- dużo

- wielokrotność

- musi

- Nowości

- Następny

- Nie

- Pojęcie

- już dziś

- numer

- of

- on

- ONE

- otwierany

- zoptymalizowane

- or

- Inne

- ludzkiej,

- wydajność

- Pokój

- łączenie w pary

- parametr

- część

- ścieżka

- dla

- jest gwarancją najlepszej jakości, które mogą dostarczyć Ci Twoje monitory,

- obwodowy

- peryferia

- fizyczny

- wybierać

- Wybiera

- rurociąg

- plato

- Analiza danych Platona

- PlatoDane

- Grać

- gra

- możliwości

- Post

- potencjał

- power

- mocny

- Procesor

- Produkty

- projektowanie

- protokół

- protokoły

- zapewniać

- zapewnia

- że

- szybko

- łatwo

- niedawny

- rozpoznaje

- renowacje

- zmniejsza

- stosunkowo

- Badania naukowe

- wielokrotnego użytku

- prawo

- Marszczyć

- Rosnąć

- Ryzyko

- run

- s

- mówią

- Skala

- scenariusze

- systemy

- Sekcja

- widziany

- widzi

- Segmenty

- wybierając

- kilka

- Shape

- dzielenie

- Prosty

- ponieważ

- pojedynczy

- mądry

- rozwiązanie

- Rozwiązania

- kilka

- wyrafinowany

- specyfikacja

- etapy

- standard

- bezpośredni

- silny

- Struktura

- Struktury

- kolejny

- sukces

- taki

- supermocarstwem

- Technologia

- niż

- że

- Połączenia

- ich

- Te

- Trzeci

- to

- myśl

- trzy

- poziom

- Krawaty

- mocniej

- czas

- do

- dzisiaj

- razem

- narzędzia

- transportu

- wyzwalanie

- ANONIMOWY

- zaktualizowane

- posługiwać się

- Użytkownicy

- za pomocą

- wartość

- różnorodny

- zmienne

- przez

- Zobacz i wysłuchaj

- vp

- we

- Strona internetowa

- Co

- Co to jest

- jeśli chodzi o komunikację i motywację

- będzie

- w

- Praca

- workflow

- zefirnet