Modelowanie sygnałów mieszanych staje się coraz ważniejsze, ponieważ interakcja między obwodami cyfrowymi i analogowymi staje się coraz ściślej powiązana. Ten poziom modelowania zależy w dużym stopniu od wystarczająco dokładnych, ale szybkich modeli behawioralnych dla komponentów analogowych. Paul Cunningham (starszy wiceprezes/GM, weryfikacja w Cadence), Raúl Camposano (Silicon Catalyst, przedsiębiorca, były dyrektor ds. technologii Synopsys, a obecnie dyrektor ds. technicznych Silvaco) i ja kontynuujemy naszą serię dotyczącą pomysłów badawczych. Jak zawsze, opinie mile widziane.

Innowacja

Wybór w tym miesiącu to Szybka walidacja układów SoC o sygnałach mieszanych. Artykuł został zaprezentowany w czasopiśmie Journal of the Solid-State Circuits Society z 2021 r. Autorzy pochodzą ze Stanford, Seoul National University i Scientific Analog.

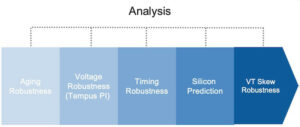

Niedawny blog SemiWiki poświęcony sygnałom mieszanym wzbudził ogromne zainteresowanie, co sugeruje, że jest to obszar wart dalszych badań. Krytycznym krokiem w celu skutecznej weryfikacji sygnału mieszanego jest opracowanie dokładnych modeli behawioralnych na poziomie mieszanym dla funkcji analogowych, które nadają się do symulacji sterowanej zdarzeniami, a nawet modeli możliwych do syntezy do wdrożenia w emulacji sprzętowej. W artykule opisano podejście do generowania modeli oparte na szablonach oraz dwie metody interpolacji zachowań analogowych do połączeń opartych na zdarzeniach: nadpróbkowanie i modelowanie sterowane zdarzeniami z wektorami cech (modele liczb rzeczywistych).

Autorzy demonstrują zastosowanie symulacji i emulacji szybkiego łącza z imponującymi wynikami. Porównanie symulacji Spice i Verilog na ADC pokazuje bliską zgodność wyników, przebiegającą o rząd wielkości szybciej. Modelowanie oparte na emulacji dodaje jeszcze więcej rzędów wielkości do tej prędkości.

Pogląd Pawła

W tym miesiącu duża zmiana kontekstu w świat weryfikacji analogowej i jej skrzyżowania „sygnałów mieszanych” z weryfikacją cyfrową. Artykuł ten jest artykułem zaproszonym do prestiżowego czasopisma, które pięknie podsumowuje najnowocześniejszy sposób budowania abstrakcyjnych modeli obwodów analogowych, które mogą nadążać za symulacją cyfrową, nawet na emulatorze, i robią to z zadziwiająco dobrą dokładnością.

W świecie analogowym wszystko jest gładkie i zwykle oscylacyjne, a zamierzone zachowanie wejścia-wyjścia często opisywane jest poprzez najpierw przekształcenie przebiegów wejścia/wyjścia do dziedziny częstotliwości. Złotym standardem symulacji analogowej jest Spice, iteracyjnie rozwiązujący równania różniczkowe na poziomie urządzenia dla napięć we wszystkich punktach obwodu w ramach gwarantowanych tolerancji błędu. W porównaniu do symulacji cyfrowej, Spice działa tysiące razy wolniej.

Typowe podejście do tworzenia szybkich abstrakcyjnych modeli analogowych polega na próbkowaniu kształtu fali wejściowej w czasie dyskretnym, a następnie generowaniu odpowiedniego przebiegu wyjściowego próbkowanego w czasie dyskretnym przy użyciu logiki podobnej do DSP (np. filtrów czasu dyskretnego). W razie potrzeby można wygenerować wartości sygnałów pomiędzy tymi dyskretnymi punktami czasowymi przy użyciu interpolacji liniowej lub splajnowej.

Autorzy przedstawiają kompletną platformę open source z eleganckim językiem generowania modeli i kompilatorem do generowania zarówno modeli symulacyjnych, jak i emulowalnych z tego języka. Wykorzystują adaptacyjną metodę próbkowania w krokach czasowych z interpolacją opartą na splajnach i opracowują wiarygodne studium przypadku, wykorzystując swoje ramy na 16-nanometrowym, szybkim łączu SERDES PHY. Przejście ze Spice na cyfrową symulację opartą na procesorze z abstrakcyjnymi modelami pozwala osiągnąć 13,000 300-krotne przyspieszenie. Umieszczenie modeli na FPGA dało kolejne XNUMX-krotne przyspieszenie. Ładny.

Pogląd Raula

Walidacja układów SoC o sygnałach mieszanych stanowi wyzwanie między innymi dlatego, że uruchomienie wystarczającej liczby wektorów testowych do sprawdzenia poprawności części cyfrowych – zazwyczaj za pomocą symulatora sterowanego zdarzeniami lub emulatora – skutkuje zbyt krótkim czasem potrzebnym na symulację części analogowej za pomocą symulatora obwodów. Rozwiązaniem jest stworzenie analogowych modeli behawioralnych. W artykule z tego miesiąca dokonano przeglądu kilku podejść do tworzenia tych modeli i przedstawiono, zdaniem autorów, pierwszą kompletną platformę open source do emulacji AMS. Jest to artykuł zaproszony do otwartego czasopisma IEEE stowarzyszenia Solid-State Circuits Society i dlatego duże fragmenty czyta się jak poradnik na temat projektowania i walidacji układów analogowych. Jest to zupełnie inne rozwiązanie niż to, co robiliśmy wcześniej na tym blogu; czytelnik potrzebuje pewnej wiedzy o analogach, aby móc w pełni skorzystać (np. domena Laplace'a, transformacja Z, PLL, interpolator fazowy, współczynniki Nyquista, jitter itp.).

Modele funkcjonalne obwodów analogowych odbierają dane wejściowe i generują wyjścia w dyskretnych czasach. Przebiegi można modelować za pomocą funkcji odcinkowo stałych lub odcinkowo liniowych, wykorzystując punkty sklejane (podejście zastosowane w tym artykule) lub sumy złożonych funkcji wykładniczych. Czas jest modelowany jako czas dyskretny (próbkowany lub nadpróbkowany) lub jako modelowanie liniowe odcinkowe (tutaj stosowane). Rzeczywiste modele obwodów są składane z biblioteki szablonów. Autorzy zebrali to wszystko w system składający się z: 1) narzędzia Pythona do generowania syntezowalnych modeli AMS dostarczającego zestaw funkcji, które pozwalają użytkownikom opisywać bloki AMS jako równania różniczkowe, listy sieci, funkcje transferu lub systemy przełączane… w dowolnym stały lub zmiennoprzecinkowy oraz 2) przypominająca symulator abstrakcja płytek FPGA, która zapewnia infrastrukturę emulacji zarządzającą krokiem czasowym emulacji, szybkością zegara emulacji i interfejsami testowymi oraz generuje strumień bitów emulacji FPGA za pomocą narzędzi EDA.

Sztuką nie jest stosowanie symulacji obwodów, ale raczej zastąpienie modeli obwodów modelami funkcjonalnymi. W przypadku odbiornika szybkiego łącza o nazwie DragonPHY przyspieszenie symulacji Verilog w porównaniu z symulacją Spice wynosi 12,800 100,000x, co zapewnia wystarczającą dokładność. Ale nawet to przyspieszenie nie wystarczy do symulacji pętli przywracania zegara i wyrównywania kanałów, aby przetestować współczynniki błędów bitowych (BER) z pętlami sprzężenia zwrotnego, których ustabilizowanie może zająć 5000 7.5 cykli. Modyfikowanie modeli w taki sposób, aby można je było syntetyzować i włączyć do emulacji, zapewnia dalsze XNUMX-krotne przyspieszenie, wystarczające do obliczenia BER w granicach XNUMX%. Imponujący!

Przeczytaj także:

Synteza asercji poprzez LLM. Innowacja w weryfikacji

Cadence Tensilica wprowadza kolejną aktualizację do architektury LX

Efektywność wnioskowania w zakresie wydajności, mocy, obszaru i skalowalności

Udostępnij ten post przez:

- Dystrybucja treści i PR oparta na SEO. Uzyskaj wzmocnienie już dziś.

- PlatoData.Network Pionowe generatywne AI. Wzmocnij się. Dostęp tutaj.

- PlatoAiStream. Inteligencja Web3. Wiedza wzmocniona. Dostęp tutaj.

- PlatonESG. Węgiel Czysta technologia, Energia, Środowisko, Słoneczny, Gospodarowanie odpadami. Dostęp tutaj.

- Platon Zdrowie. Inteligencja w zakresie biotechnologii i badań klinicznych. Dostęp tutaj.

- Źródło: https://semiwiki.com/eda/336610-developing-effective-mixed-signal-models-innovation-in-verification/

- :Jest

- :nie

- $W GÓRĘ

- 1

- 100

- 12

- 13

- 2021

- 300

- 7

- a

- Zdolny

- ABSTRACT

- abstrakcja

- precyzja

- dokładny

- Osiąga

- rzeczywisty

- adaptive

- Dodaje

- Wszystkie kategorie

- pozwala

- zawsze

- wśród

- an

- i

- Inne

- Zastosowanie

- podejście

- awanse

- właściwy

- SĄ

- POWIERZCHNIA

- AS

- zmontowane

- At

- Autorzy

- BE

- estetycznie

- bo

- stają się

- staje

- zanim

- zachowanie

- uwierzyć

- korzyści

- pomiędzy

- Bit

- Bloki

- Blog

- obie

- budować

- ale

- by

- Kadencja

- nazywa

- CAN

- Zajęte

- walizka

- studium przypadku

- Katalizator

- wyzwanie

- Kanał

- zegar

- Zamknij

- dokładnie

- w porównaniu

- porównanie

- kompletny

- kompleks

- składniki

- obliczać

- połączenia

- Składający się

- stały

- kontynuować

- Stwórz

- Tworzenie

- tworzenie

- wiarygodny

- krytyczny

- CTO

- Cykle

- wykazać

- zależy

- Wdrożenie

- opisać

- opisane

- Wnętrze

- rozwijać

- rozwijanie

- różne

- cyfrowy

- do

- domena

- zrobić

- napędzany

- e

- Efektywne

- efektywność

- bądź

- ogromny

- dość

- Przedsiębiorca

- równania

- błąd

- itp

- Parzyste

- wydarzenie

- wszystko

- wykładniczy

- FAST

- szybciej

- Cecha

- informacja zwrotna

- filtry

- i terminów, a

- ustalony

- unoszący się

- W razie zamówieenia projektu

- Dawny

- FPGA

- Framework

- Częstotliwość

- od

- w pełni

- funkcjonalny

- Funkcje

- dalej

- dał

- Generować

- wygenerowane

- generuje

- generujący

- generacja

- będzie

- Złoto

- gold standard

- dobry

- gwarantowane

- sprzęt komputerowy

- Have

- pomoc

- tutaj

- Wysoki

- HTTPS

- i

- pomysły

- IEEE

- if

- ważny

- imponujący

- in

- Rejestrowy

- Infrastruktura

- Innowacja

- wkład

- Wejścia

- zamierzony

- wzajemne oddziaływanie

- odsetki

- interfejsy

- skrzyżowanie

- splecione

- najnowszych

- zaproszony

- IT

- JEGO

- dziennik

- Trzymać

- język

- duży

- poziom

- Biblioteka

- lubić

- LINK

- logika

- zarządza

- Maksymalna szerokość

- Może..

- metoda

- metody

- mieszany

- model

- modelowanie

- modele

- Miesiąc

- jeszcze

- narodowy

- potrzebne

- wymagania

- Nowości

- Następny

- miło

- już dziś

- numer

- of

- często

- on

- koncepcja

- open source

- or

- Zlecenia

- Inne

- ludzkiej,

- wydajność

- Wyjścia

- Papier

- część

- strony

- Paweł

- jest gwarancją najlepszej jakości, które mogą dostarczyć Ci Twoje monitory,

- faza

- wybierać

- plato

- Analiza danych Platona

- PlatoDane

- punkt

- zwrotnica

- Post

- power

- teraźniejszość

- przedstawione

- prezenty

- prestiżowy

- zapewnia

- że

- położyć

- Putting

- Python

- całkiem

- ceny

- raczej

- Czytaj

- Czytelnik

- real

- zrealizować

- otrzymać

- niedawny

- regeneracja

- Badania naukowe

- Efekt

- Recenzje

- bieganie

- naukowy

- senior

- Seul

- Serie

- zestaw

- rozstrzygać

- kilka

- Targi

- Signal

- Krzem

- symulacja

- symulator

- gładki

- So

- Społeczeństwo

- rozwiązanie

- Rozwiązywanie

- kilka

- prędkość

- przyprawa

- spiny

- standard

- Stanford

- state-of-the-art

- Ewolucja krok po kroku

- Badanie

- taki

- wystarczający

- odpowiedni

- sumy

- przełączane

- synteza

- system

- systemy

- Brać

- Szablony

- test

- że

- Połączenia

- świat

- ich

- następnie

- Te

- one

- rzeczy

- to

- tysiące

- Przez

- czas

- czasy

- do

- razem

- narzędzie

- narzędzia

- przenieść

- transformatorowy

- Tutorial

- drugiej

- typowy

- zazwyczaj

- uniwersytet

- uaktualnienie

- posługiwać się

- używany

- Użytkownicy

- za pomocą

- zazwyczaj

- UPRAWOMOCNIĆ

- uprawomocnienie

- Wartości

- Weryfikacja

- Przeciw

- przez

- była

- we

- powitanie

- Co

- który

- w

- w ciągu

- Praca

- świat

- wartość

- jeszcze

- zefirnet