Jednym z celów niedawnego szczytu RISC-V było wykazanie, że ruch RISC-V jest prawdziwy – główne programy dużych organizacji zobowiązujących się do rozwoju wokół RISC-V ISA. Powiedziałbym, że cel ten został osiągnięty. Zaprezentowano wiele głośnych ogłoszeń i agresywnych, nowych architektur opartych na RISC-V. Pierwszego dnia w porządku obrad znalazły się fascynujące wystąpienia takich firm jak Ventana Micro Systems, Meta, Microchip, Qualcomm i Synopsys. Ale co z mniejszymi firmami? Pod koniec pierwszego dnia grupa tych firm miała okazję opowiedzieć uczestnikom konferencji o wspaniałej pracy, którą wykonali. Czytaj dalej, aby poczuć skalę ruchu RISC-V, podczas gdy Launchpad Showcase podkreśla innowacje mniejszych firm.

Trzy minuty sławy

Słynny cytat, „W przyszłości każdy będzie sławny na całym świecie przez 15 minut” przypisuje się Andy’emu Warholowi od lat 1960. XX wieku. Kto właściwie powiedział to pierwszy, jest przedmiotem pewnej debaty. Niezależnie od tego koncepcja ta jest dziś dość aktualna dzięki wszechobecnym platformom mediów społecznościowych. Pod koniec pierwszego dnia szczytu RISC-V Tiffany Sparks, dyrektor ds. marketingu w RISC-V International, rozpoczęła sesję, której celem było podkreślenie szerokiego zakresu innowacji prezentowanych na konferencji. Wybrano osiem firm, a 15 minut sławy skrócono do trzech, aby zarządzać długością sesji. Czy osiem osób jest w stanie pod koniec długiego dnia wypełnionego prezentacjami przekazać szerokiemu gronu odbiorców przekonujący i zapadający w pamięć komunikat? Dowiedzmy Się…

Andes D25F-SE: Superbohater procesorów RISC-V

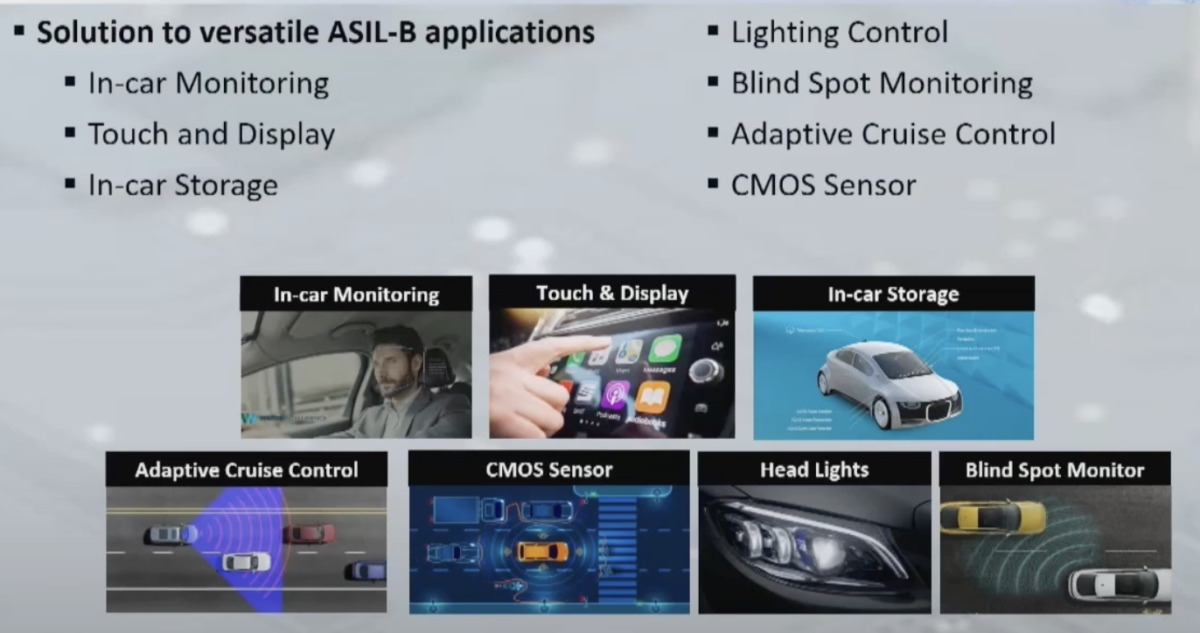

Marvin Chao, dyrektor architekta rozwiązań prezentowany dla Andes Technology. Marvin wyjaśnił, że rdzeń D25F-SE jest w pełni zgodny z ASIL-B i zawiera kilka rozszerzeń, dzięki czemu jest przydatny w wielu zastosowaniach motoryzacyjnych, jak pokazano na poniższym rysunku.

Rdzeń ma pięciostopniową, uporządkowaną architekturę pojedynczego wydania. Oparty na 5-bitowej architekturze AndesStar V32, posiada RV32 GCBP ISA z rozszerzeniami Andes. Podsystem pamięci obsługuje instrukcje i pamięci podręczne danych o pojemności do 32 KB każda oraz lokalne pamięci instrukcji i danych o pojemności do 16 MB każda. Część posiada porty AXI lub AHB oraz port bezpośredniego dostępu do pamięci lokalnej. W celu zapewnienia bezpieczeństwa funkcjonalnego dostępna jest obsługa takich elementów, jak interfejs magistrali stanu pułapki rdzeniowej, ochrona ECC, StackSafe i PMP. Część uzyska certyfikat ASIL-B w czwartym kwartale 4 r.

Marvin wyjaśnił, że można osiągnąć przyspieszenia w zakresie 3X lub większym. Według mnie wydajność i elastyczność tego projektu plasuje go w kategorii superbohaterów.

Beagleboard.org: Dostęp do technologii bez barier

Jason Kridner, współzałożyciel beagleboard.org, zaprezentował kilka nowych produktów tej organizacji non-profit. Jej misją jest zapewnienie edukacji i współpracy w zakresie projektowania i wykorzystania oprogramowania i sprzętu typu open source w systemach wbudowanych. Jason zaprezentował dwie nowe tablice.

BeagleV-Ahead jest przeznaczony do zastosowań mobilnych i brzegowych o wysokiej wydajności. Zawiera czterordzeniowy C910 2GHZ ze zoptymalizowanymi procesorami wideo, graficznymi, neuronowymi i audio. Obsługuje wykonywanie poza kolejnością i obsługuje H.264 i H.265. Następnie Jason opisał znacznie więcej możliwości produktu, dzięki czemu ma on szerokie zastosowanie. Najlepsze jest to, że jest dostępny na całym świecie w cenie 149 dolarów.

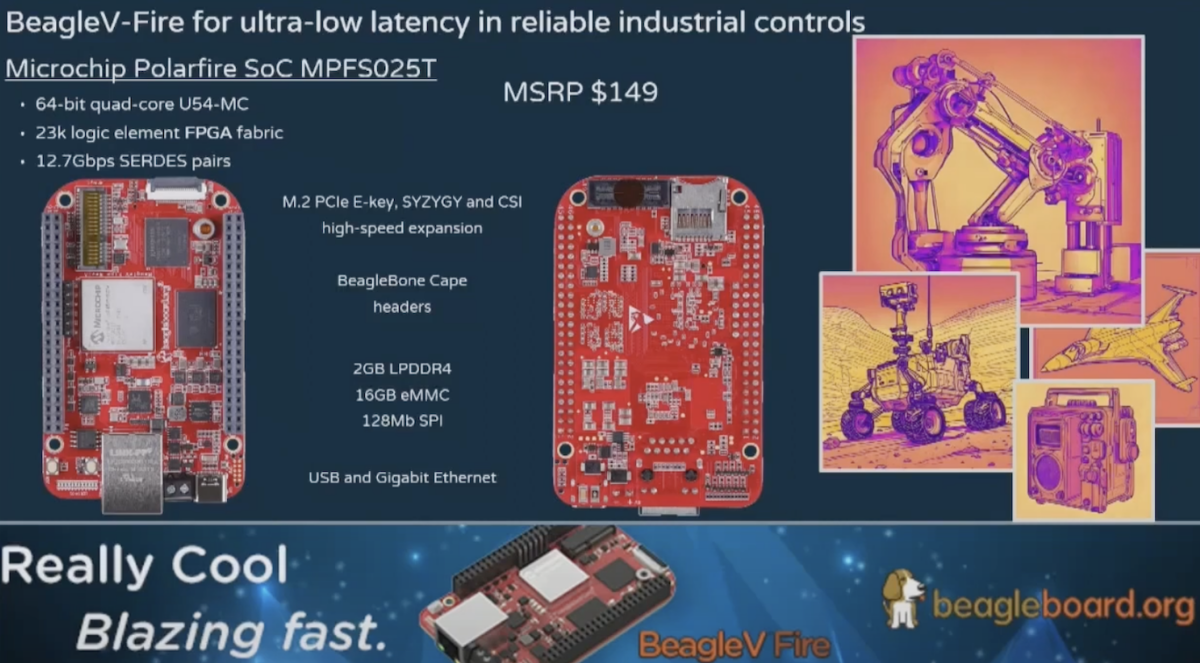

Zaprezentował także właśnie zapowiedziany produkt – BeagleV-Fire. W tej części zastosowano układ SoC Microchip PolarFire z układem FPGA, co ułatwia eksperymentowanie. Ten obejmuje również dużo miejsca na aplikacje i jest również dostępny za 149 USD. Poniżej znajduje się więcej szczegółów na ten temat.

Jason zakończył swoją prezentację propozycją umówienia się z nim na spotkanie za pośrednictwem strony beagleboard.org. Jest po to, aby pomóc społeczności odnieść sukces, dlatego osobiście angażuje się w misję dostęp do technologii bez barier.

Codasip: Poznaj pana Custom Compute

Mike Eftimakis jest wiceprezesem ds. strategii i ekosystemu w Codasip. Jest znany w całej firmie ze swojej pasji związanej z niestandardowymi obliczeniami. Mike zwrócił uwagę, że niestandardowe obliczenia są wyróżnikiem Codasip, więc jego pasja dobrze pokrywa się z celami firmy. Wyjaśnił, że Codasip od początku zdecydował się przyjąć inne podejście, które zapewniłoby elastyczność niezbędną do urzeczywistnienia niestandardowych obliczeń.

Mike wyjaśnił, że możliwa jest poprawa wydajności na poziomie 1,000–10,000 700 procent, jeśli przyjmie się koncepcję dostrajania i dostosowywania procesora do aplikacji. Następnie wyjaśnił, że ręczne wykonanie tej czynności jest bardzo trudne i dlatego Codasip zainwestował w trzy obszary: narzędzia, metodologię i gamę rdzeni IP gotowych do dostosowania. W tej ostatniej kwestii Mike opowiedział o nowej rodzinie XNUMX, która została ogłoszona podczas pokazu. Zapewnia to dużą elastyczność w wielu zastosowaniach, a nawet ma  technologię, która udaremni aż do 70 procent możliwych cyberataków. Na koniec powiedział wszystkim, aby przestali marnować czas na próby optymalizacji projektu za pomocą architektury, która nie jest przeznaczona do modyfikacji. Zadzwoń do Codasipa.

technologię, która udaremni aż do 70 procent możliwych cyberataków. Na koniec powiedział wszystkim, aby przestali marnować czas na próby optymalizacji projektu za pomocą architektury, która nie jest przeznaczona do modyfikacji. Zadzwoń do Codasipa.

Pasja i zaangażowanie Mike'a były całkiem jasne. Zrobił to wszystko za pomocą jednego slajdu, który miał, cóż, bardzo mało treści.

Deep Computing: pierwsza rozmowa telefoniczna z pada RISC-V

Yuning Liang, dyrektor generalny Deep Computing, wyjaśnił, że jego firma opracowuje aplikacje na wiele rynków, w tym komputery osobiste, laptopy, stacje robocze i produkty elektroniki użytkowej, a niektóre z nich można było zobaczyć na wystawie. Poniższy rysunek podsumowuje szeroką gamę produktów firmy.

Z pomocą Tiffany, Yuning po raz pierwszy na żywo na scenie przeprowadził rozmowę telefoniczną z padu RISC-V. Wykonanie tego przed dużą publicznością na żywo zdecydowanie pokazuje poziom zaufania Yuninga do swojej firmy i jej produktów.

Technologie esperanto: generatywna sztuczna inteligencja spełnia RISC-V

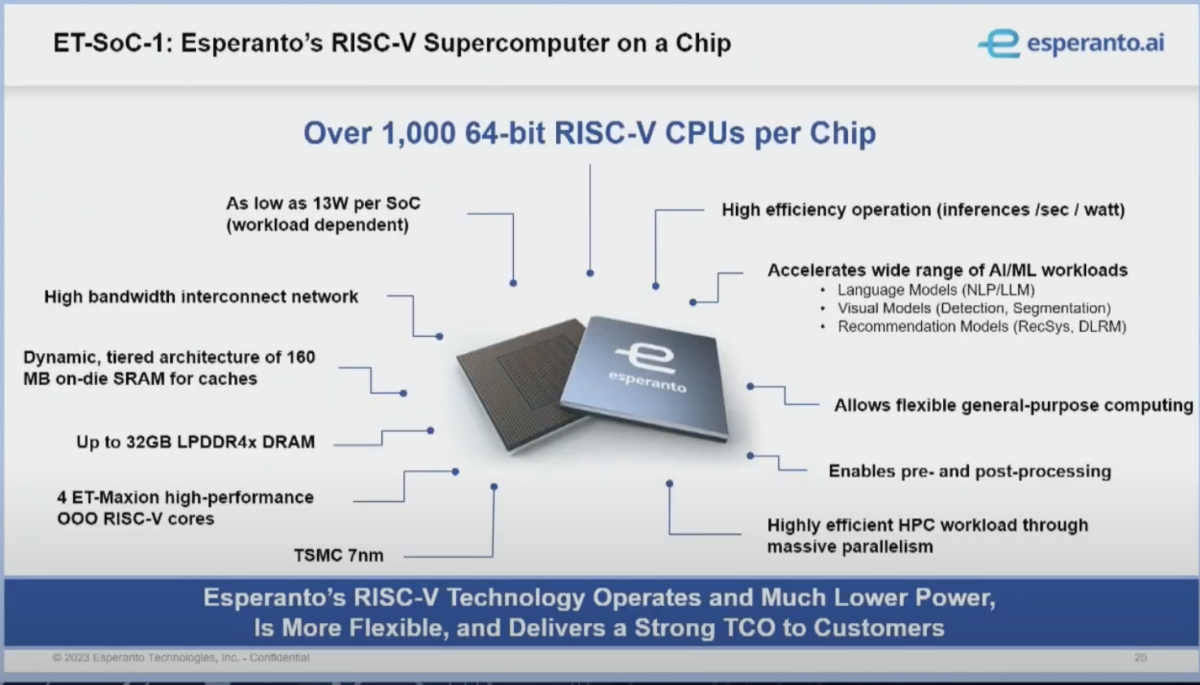

Craig Cochran jest wiceprezesem ds. marketingu i rozwoju biznesu w Esperanto Technologies. Wyjaśnił, że potrzeby w zakresie obliczeń o wysokiej wydajności i uczenia maszynowego w rzeczywistości są zbieżne. Następnie powiedział, że RISC-V ma wyjątkową możliwość zbudowania najlepszych konwergentnych systemów HPC i ML.

Craig przedstawił nowy superkomputer RISC-V firmy Esperanto na chipie, ET-SoC-1. Urządzenie zawiera ponad 1,000 64-bitowych procesorów RISC-V na chip. Układ jest bardzo energooszczędny i można go łączyć w duże systemy. Poniżej przedstawiono przegląd architektoniczny.

Craig zakończył ważną wiadomością dotyczącą nowej aplikacji dla tej architektury. Esperanto stosuje to w nowym generatywnym urządzeniu AI do wnioskowania AI. Wydajność i energooszczędność są znaczne, a przestrzeń zastosowań wydaje się szeroka. To zdecydowanie coś, co warto obejrzeć.

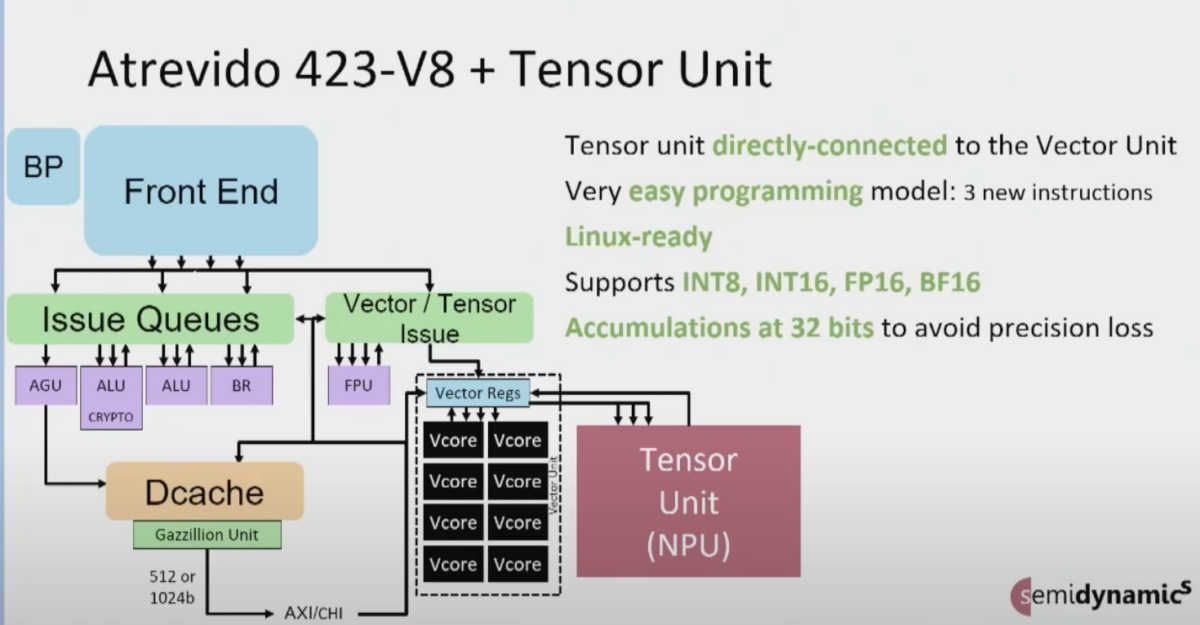

Półdynamika: zapewnianie nieuczciwych korzyści dzięki integracji tensorów i jednostek wektorowych

Roger Espasa, dyrektor generalny i założyciel firmy Semidynamics, wyjaśnił szczegóły nowego projektu firmy, który bezpośrednio łączy jednostkę tensorową z istniejącą jednostką wektorową. Roger wygłosił jedną z bardziej szczegółowych i technicznych prezentacji. Puentą jest tak naprawdę wydajność i kompatybilność oprogramowania.

Procesy AI będą zazwyczaj mnożyć macierze danych i wykonywać operacje na podstawie wyników. Chociaż Linux bezpośrednio obsługuje te koncepcje, typowa implementacja sprzętowa wymaga wielu operacji i przenoszenia danych, aby to osiągnąć. Daleko mu do elegancji. Teraz, dzięki zintegrowanej architekturze dostarczanej przez Semidynamics, operacje wektorowe są wykonywane w jednostce tensorowej, a wyniki są natychmiast dostępne w jednostce wektorowej w celu wsparcia kolejnych działań. To dość eleganckie rozwiązanie. Poniższy diagram przedstawia niektóre szczegóły architektury.

Takie podejście obiecuje ogromny wpływ. Kolejny do obejrzenia.

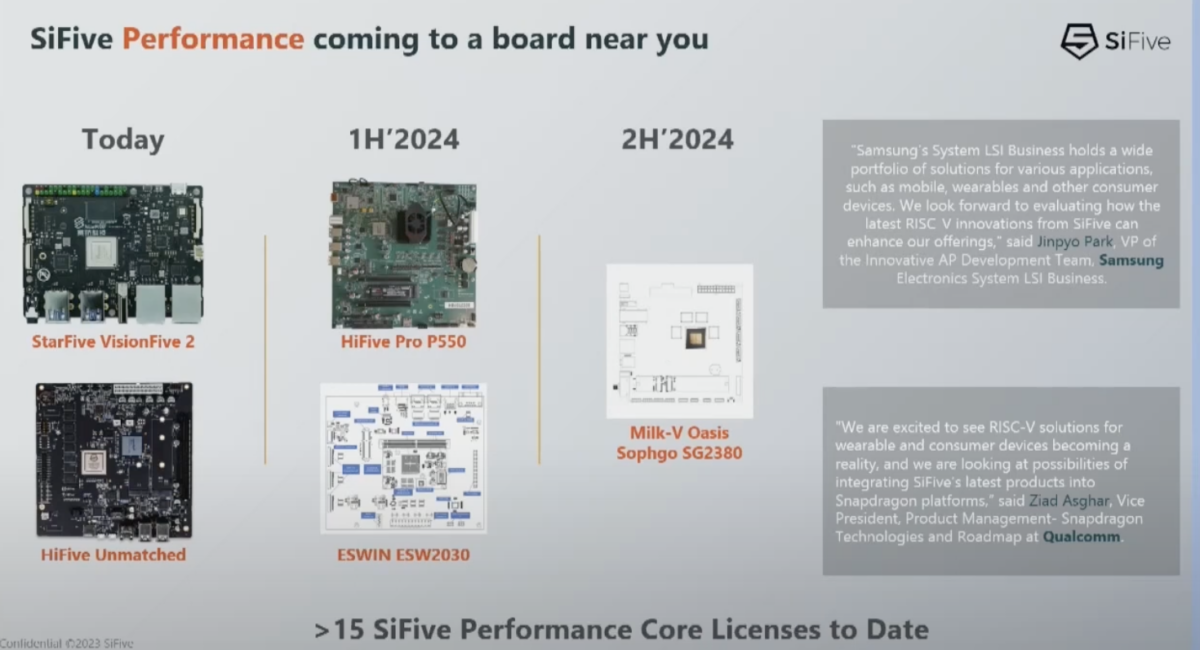

SiFive: Rdzenie i płytki rozwojowe dla wszystkich

Drew Barbier jest starszym dyrektorem ds. zarządzania produktami w SiFive. Pracuje w firmie już dłuższy czas. Drew mówił o potrzebie kompletnego rozwiązania, a nie tylko rdzenia RISC-V. Wyjaśnił, że SiFive rozumie tę potrzebę i ciężko pracuje, dostarczając kompletne rozwiązania. Niektóre z omawianych przez niego kwestii to m.in.:

- Spójna, heterogeniczna architektura systemu

- Rozszerzenia kryptograficzne wektora RISC-V

- Hypervisor i IOMMU

- Zaawansowane zarządzanie energią

- bezpieczeństwo systemu

Rzeczywista lista jest dość długa, jest tu co dostarczać. Następnie Drew omówił szeroko zakrojony program rozwoju zespołu SiFive. Firma współpracuje ze swoimi partnerami, aby dostarczać szeroką gamę płytek deweloperskich przeznaczonych na wiele rynków. Poniżej znajduje się podsumowanie programu.

SiFive wyraźnie słuchało swoich klientów. Wsparcie produktu jest dość obszerne.

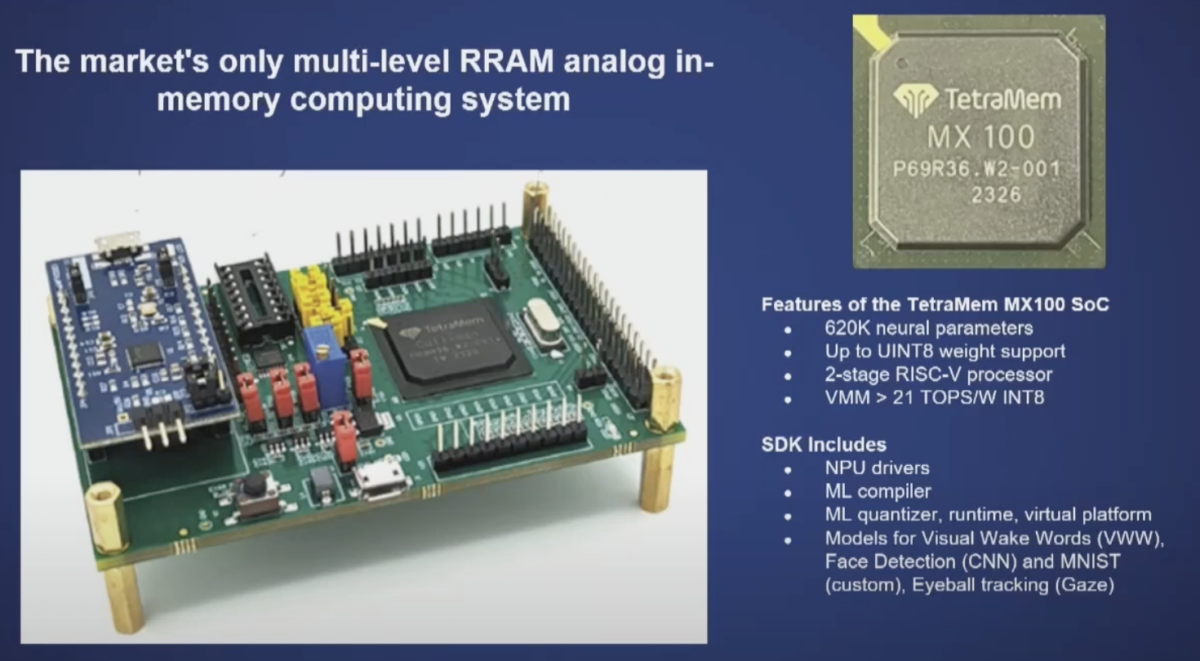

TetraMem: Witamy w rewolucji w fizyce informatyki

David George jest szefem operacji globalnych w TetraMem Inc. David mówił o nowym elemencie obwodu wykraczającym poza tradycyjny kondensator, rezystor i cewkę indukcyjną. Memrystor to nowatorski element obwodu będący podstawą nowego produktu TetraMem, MX 100, który jest pierwszą komercyjną implementacją memrystora. Poniższy rysunek podsumowuje niektóre jego możliwości.

To urządzenie wykonuje analogowe obliczenia w pamięci na procesorze RISC-V SoC. David wyjaśnił, że urządzenia analogowe są zorganizowane w jednostki przetwarzania neuronowego i wykorzystują moc memrystora w unikalny sposób, eliminując potrzebę tysięcy cykli zegara. Rezultatem jest ogromna poprawa opóźnień, mocy i przepustowości. Następnie David wskazał, że ta innowacja wymagała zastosowania umiejętności z zakresu materiałoznawstwa, procesów i urządzeń półprzewodnikowych, architektury obwodów, algorytmów i aplikacji. To wirtuoz technologii, zapewniający kompletne rozwiązanie sprzętowe i programowe do wnioskowania o sieciach neuronowych na potrzeby sztucznej inteligencji na krawędzi.

TetraMem rzeczywiście organizuje rewolucję w fizyce obliczeń. Wpływ rośnie dzięki ogłoszonym partnerstwom z firmami Andes i Synopsys. Ekscytujące rzeczy.

Aby bardziej się pochylić

Podczas stosunkowo krótkiej sesji ośmiu innowatorów zaprezentowało technologię, która może zmienić reguły gry. Na takiej konferencji ten dorobek mógłby zająć cały utwór. W tym przypadku wszystko zostało omówione podczas jednej krótkiej sesji. Jeśli chcesz zobaczyć wydarzenie, tutaj możesz uzyskać dostęp do jego powtórki. Możesz również dowiedzieć się więcej o RISC-V na SemiWiki tutaj. Launchpad Showcase podkreśla innowacje mniejszych firm – wspaniały wynik rosnącej społeczności RISC-V.

Udostępnij ten post przez:

- Dystrybucja treści i PR oparta na SEO. Uzyskaj wzmocnienie już dziś.

- PlatoData.Network Pionowe generatywne AI. Wzmocnij się. Dostęp tutaj.

- PlatoAiStream. Inteligencja Web3. Wiedza wzmocniona. Dostęp tutaj.

- PlatonESG. Węgiel Czysta technologia, Energia, Środowisko, Słoneczny, Gospodarowanie odpadami. Dostęp tutaj.

- Platon Zdrowie. Inteligencja w zakresie biotechnologii i badań klinicznych. Dostęp tutaj.

- Źródło: https://semiwiki.com/events/339138-risc-v-summit-buzz-launchpad-showcase-highlights-smaller-company-innovation/

- :ma

- :Jest

- :nie

- $W GÓRĘ

- 000

- 1

- 10

- 100

- 15%

- 2023

- 264

- 300

- 70

- 700

- a

- O nas

- dostęp

- osiągnięty

- w poprzek

- działania

- rzeczywisty

- faktycznie

- Zalety

- agenda

- agresywny

- AI

- wymierzony

- Algorytmy

- Wyrównuje

- Wszystkie kategorie

- dopuszczać

- również

- an

- i

- ogłosił

- Ogłoszenia

- Inne

- pojawia się

- odpowiedni

- Zastosowanie

- aplikacje

- Stosowanie

- podejście

- architektoniczny

- architektura

- SĄ

- obszary

- na około

- AS

- At

- uczestnicy

- publiczność

- audio

- motoryzacyjny

- dostępny

- b

- bariery

- na podstawie

- BE

- być

- Początek

- jest

- uwierzyć

- poniżej

- BEST

- Poza

- Duży

- deska

- ciało

- szerokość

- Przynosi

- szeroki

- budować

- autobus

- biznes

- rozwój biznesu

- ale

- by

- wezwanie

- CAN

- możliwości

- walizka

- Kategoria

- ceo

- CEO i założyciel

- Dyplomowani

- szansa

- żeton

- wybrany

- jasny

- wyraźnie

- zegar

- Współzałożyciel

- współpraca

- połączony

- handlowy

- zobowiązanie

- zobowiązany

- zobowiązanie się

- społeczność

- Firmy

- sukcesy firma

- Firma

- zgodność

- zniewalający

- kompletny

- zgodny

- obliczać

- computing

- pojęcie

- Koncepcje

- Konferencja

- pewność siebie

- łączy

- konsument

- Elektroniki użytkowej

- zawiera

- zawartość

- zbieżny

- rdzeń

- mógłby

- Para

- pokrywa

- pokryty

- obejmuje

- Crypto

- zwyczaj

- Klientów

- dostosowywanie

- Cykle

- dane

- David

- dzień

- debata

- postanowiła

- głęboko

- Zdecydowanie

- dostarczyć

- dostarczona

- dostarczanie

- wykazać

- opisać

- Wnętrze

- detal

- szczegółowe

- detale

- oprogramowania

- rozwija się

- urządzenie

- urządzenia

- ZROBIŁ

- różne

- różnicujący

- trudny

- kierować

- Dostęp bezpośredni

- bezpośrednio

- Dyrektor

- omówione

- robi

- robi

- zrobić

- E i T

- każdy

- łatwo

- Ekosystem

- krawędź

- Edukacja

- efektywność

- wydajny

- Elektronika

- element

- eliminując

- osadzone

- Objęcia

- zakończenia

- zakończony

- energia

- Parzyste

- wydarzenie

- wszyscy

- ekscytujący

- egzekucja

- Przede wszystkim system został opracowany

- Wyjaśniać

- wyjaśnione

- rozszerzenia

- rozległy

- tkanina

- SŁAWA

- członków Twojej rodziny

- sławny

- daleko

- uczucie

- Postać

- Znajdź

- natura

- i terminów, a

- Elastyczność

- piętro

- W razie zamówieenia projektu

- założyciel

- FPGA

- od

- z przodu

- w pełni

- funkcjonalny

- przyszłość

- dał

- generatywny

- generatywna sztuczna inteligencja

- George

- otrzymać

- Globalne

- cel

- Gole

- got

- grafika

- wspaniały

- Zarządzanie

- Rozwój

- miał

- ręka

- Ciężko

- sprzęt komputerowy

- he

- głowa

- pomoc

- tutaj

- wysoka wydajność

- wysoki profil

- Atrakcja

- pasemka

- go

- jego

- posiada

- HPC

- HTTPS

- olbrzymi

- i

- if

- natychmiast

- Rezultat

- realizacja

- poprawa

- ulepszenia

- in

- Inc

- zawierać

- Włącznie z

- osób

- Innowacja

- innowacje

- innowatorzy

- instrukcje

- zintegrowany

- integracja

- Interfejs

- na świecie

- najnowszych

- wprowadzono

- zainwestowany

- IP

- IT

- szt

- JEGO

- właśnie

- Keynotes

- znany

- laptopy

- duży

- Nazwisko

- Utajenie

- Launchpad

- UCZYĆ SIĘ

- nauka

- Długość

- poziom

- lubić

- Linia

- linux

- Lista

- słuchałem

- mało

- relacja na żywo

- miejscowy

- długo

- Partia

- maszyna

- uczenie maszynowe

- poważny

- robić

- Dokonywanie

- zarządzanie

- i konserwacjami

- wiele

- Marketing

- rynki

- materiały

- Maksymalna szerokość

- Oznaczało

- Media

- Poznaj nasz

- Spotkanie

- Spełnia

- niezapomniany

- wspomnienia

- Pamięć

- wiadomość

- Meta

- Metodologia

- mikro

- mikrofon

- minuty

- Misja

- ML

- Aplikacje mobilne

- zmodyfikowano

- jeszcze

- ruch

- mr

- wielokrotność

- MX

- Potrzebować

- potrzebne

- wymagania

- sieć

- Nerwowy

- sieci neuronowe

- Nowości

- nowy produkt

- Nowe produkty

- aktualności

- niedochodowy

- organizacja non-profit

- Pojęcie

- powieść

- już dziś

- of

- oferta

- on

- ONE

- open source

- Oprogramowanie typu open source

- operacje

- Optymalizacja

- zoptymalizowane

- or

- orkiestracja

- zamówienie

- Realizacja zamówienia

- organizacja

- organizacji

- Zorganizowany

- na zewnątrz

- koniec

- przegląd

- ścieżka

- część

- wzmacniacz

- partnerstwa

- pasja

- dla

- procent

- wykonać

- jest gwarancją najlepszej jakości, które mogą dostarczyć Ci Twoje monitory,

- wykonuje

- osobisty

- Osobiście

- telefon

- Rozmowa telefoniczna

- Fizyka

- umieszczony

- Platformy

- plato

- Analiza danych Platona

- PlatoDane

- punkt

- porty

- position

- możliwy

- Post

- potencjalnie

- power

- presentation

- Presentations

- przedstawione

- prezydent

- procesów

- przetwarzanie

- Procesor

- Procesory

- Produkt

- zarządzanie produktem

- Produkty

- Program

- Programy

- obietnica

- ochrona

- zapewniać

- dziurkacz

- położyć

- Qualcomm

- ilość

- całkiem

- zacytować

- zasięg

- Czytaj

- gotowy

- real

- Rzeczywistość

- naprawdę

- niedawny

- Zredukowany

- w sprawie

- Bez względu

- stosunkowo

- wymagany

- Wymaga

- dalsze

- Efekt

- Rewolucja

- Bezpieczeństwo

- Powiedział

- powiedzieć

- nauka

- widzieć

- widziany

- Semiconductor

- senior

- Sesja

- zestaw

- kilka

- Short

- pokazać

- Pokaż piętro

- prezentacja

- pokazane

- Targi

- umiejętności

- suwak

- mniejszy

- So

- Obserwuj Nas

- Media społecznościowe

- platform społecznych mediów

- Tworzenie

- Oprogramowanie

- rozwiązanie

- Rozwiązania

- kilka

- Typ przestrzeni

- Sparks

- STAGE

- Rynek

- Stop

- Strategia

- przedmiot

- kolejny

- znaczny

- osiągnąć sukces

- taki

- PODSUMOWANIE

- Szczyt

- Superkomputer

- superhero

- wsparcie

- podpory

- pewnie

- system

- systemy

- Brać

- Techniczny

- techniczny

- Technologies

- Technologia

- powiedzieć

- mówi

- dzięki

- że

- Połączenia

- Przyszłość

- następnie

- Tam.

- Te

- one

- rzeczy

- to

- tysiące

- trzy

- wydajność

- Muślin

- czas

- do

- już dziś

- narzędzia

- śledzić

- tradycyjny

- stara

- drugiej

- typowy

- zazwyczaj

- wszechobecny

- rozumie

- W toku

- niesprawiedliwy

- wyjątkowy

- jednostka

- jednostek

- posługiwać się

- zastosowania

- różnorodność

- początku.

- przez

- wice

- Wiceprezes

- Wideo

- vp

- była

- Oglądaj

- Droga..

- Strona internetowa

- powitanie

- DOBRZE

- poszedł

- były

- Co

- który

- Podczas

- KIM

- cały

- dlaczego

- szeroki

- Szeroki zasięg

- będzie

- w

- bez

- Praca

- pracujący

- na calym swiecie

- by

- ty

- Twój

- youtube

- zefirnet