I det raskt utviklende landskapet med kunstig intelligens (AI) og dataintensive applikasjoner, har etterspørselen etter høyytelses sammenkoblingsteknologier aldri vært mer kritisk. Selv 100G Interconnect er allerede ikke rask nok for infrastrukturapplikasjoner. AI-applikasjoner, med sine enorme datasett og komplekse algoritmer, driver behovet for enestående dataoverføringshastigheter. 224G Serializer/Deserializer (SerDes) står i forkant av høyhastighets datakommunikasjonsrevolusjonen, og innleder en ny æra med enestående ytelse og tilpasningsevne.

Alphawave anerkjenner dette markedsbehovet og adresserer det på en front med sine banebrytende 200G-sammenkoblingsteknologier. Det er et vitnesbyrd om selskapets forpliktelse til å ligge i forkant av datakurven, og gi industrien den hastigheten og effektiviteten som trengs for å drive AI og høyytelses databehandling inn i fremtiden.

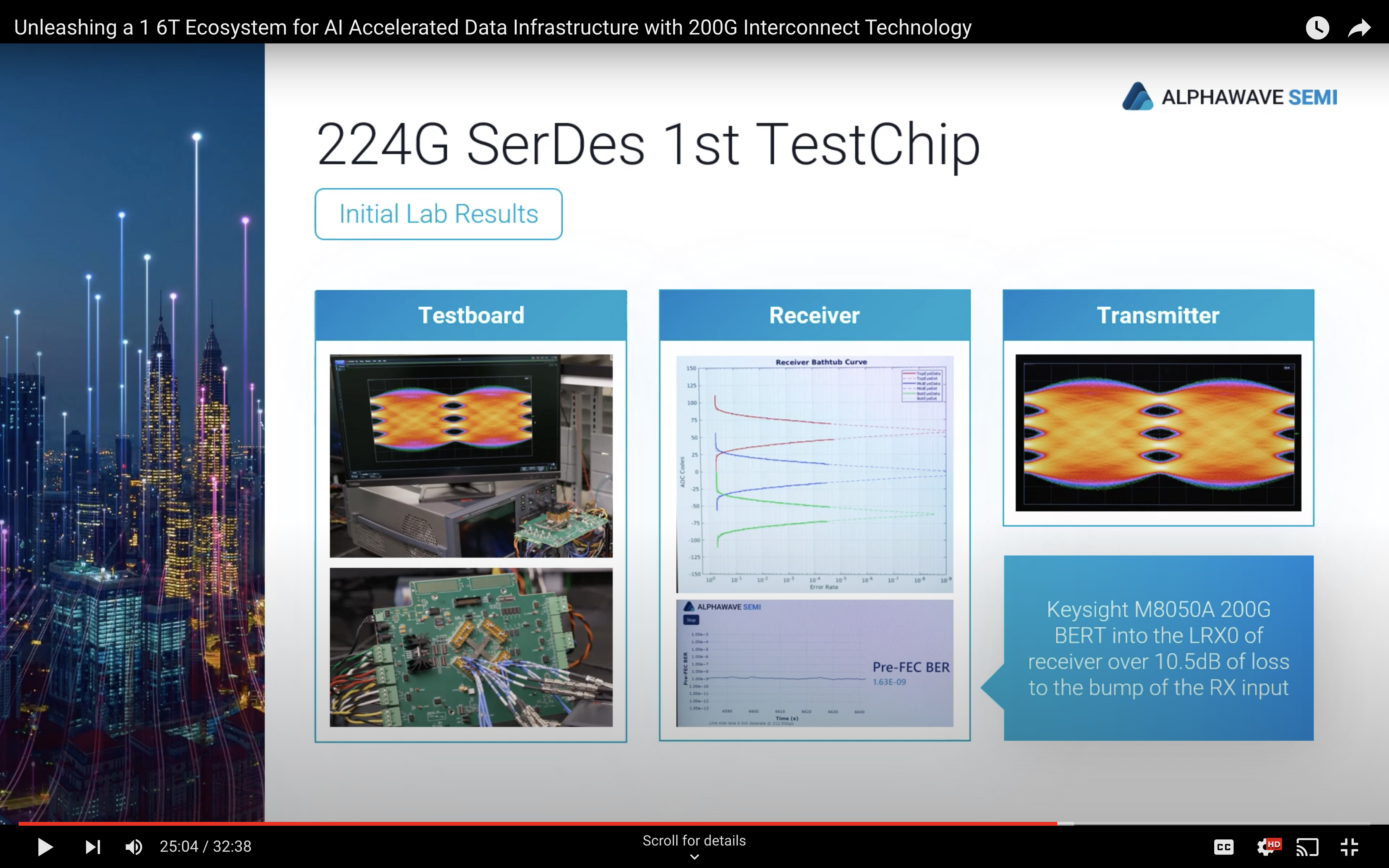

Nylig arrangerte selskapet et webinar om dette emnet og delte resultater fra deres AthenaCORE 224G SerDes TestChip. Dette innlegget tar en titt på Alphawaves innsats for å frigjøre 1.6T-økosystemet med dets omfattende tilbud, inkludert 200G-sammenkoblingsteknologien.

Utnytte Alphawaves 112G SerDes-suksess for å levere robuste 224G SerDes

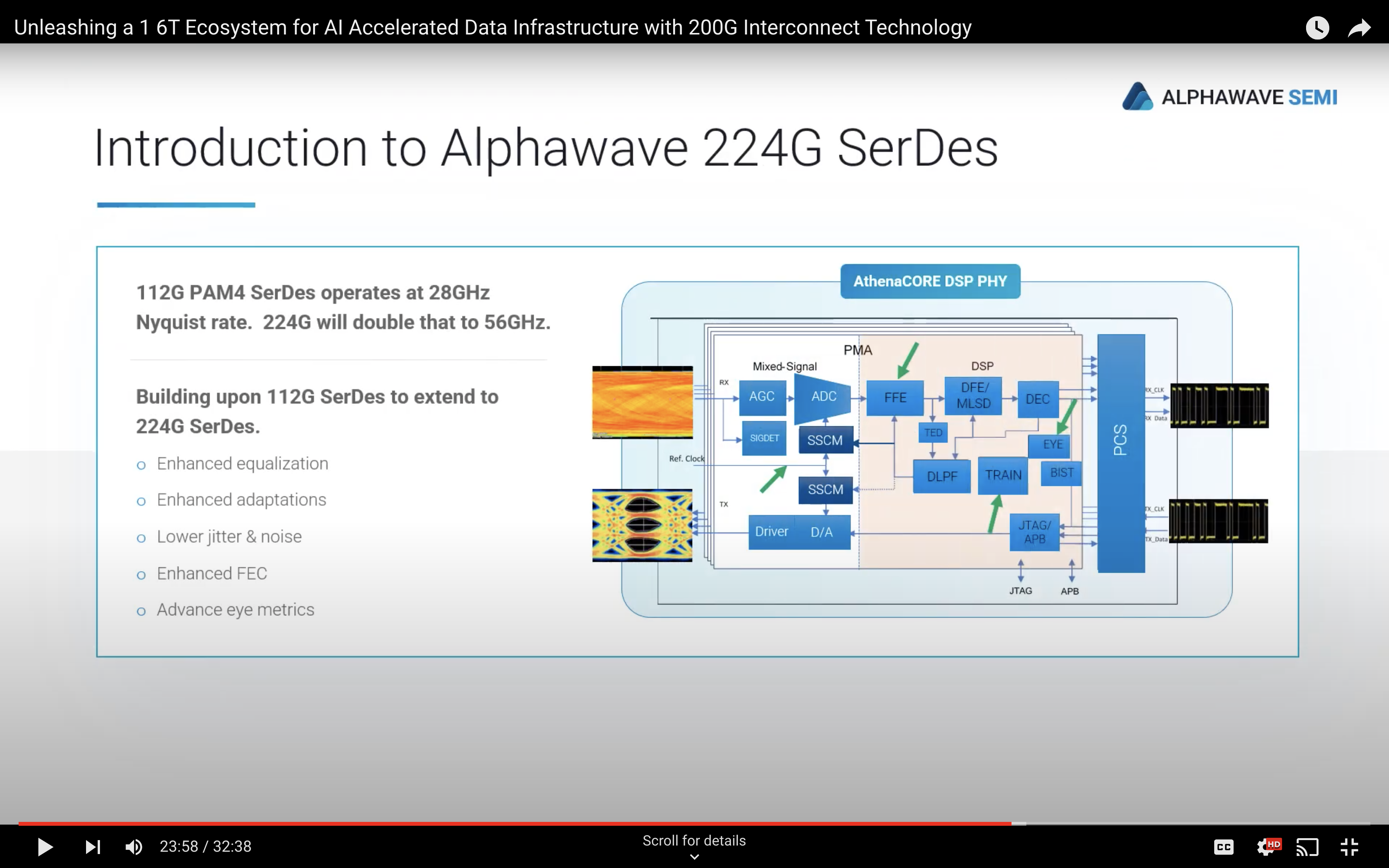

Ved å utvide sine velprøvde 112G SerDes til å støtte bemerkelsesverdige 224Gbps, har Alphawave ikke bare doblet datahastigheten, men har også låst opp nye muligheter for dataintensive applikasjoner, spesielt innen kunstig intelligens (AI) og avansert databehandling. Å overvinne de tilhørende utfordringene og kompleksiteten til 200G Interconnect krevde en kombinasjon av avanserte teknologier, innovative designtilnærminger og samarbeidsinnsats innen industrien. Alphawave har bygget på denne 112G SerDes-suksessen for å levere de enda strengere kravene til en 224G SerDes.

Den AlphaCORE DSP-baserte Serializer/Deserializer (SerDes)-arkitekturen er konstruert for å levere allsidige høyhastighets datakommunikasjonsløsninger, med en konfigurerbar 112G Digital Signal Processor (DSP). Konfigurerbarheten til DSP-arkitekturen muliggjør tilpasning for ulike applikasjoner og ytelseskrav, og gir en plug-and-play modulær design for utskiftbarhet og enkel integrasjon. Med en datahastighet på 112 gigabit per sekund (112G), samsvarer arkitekturen med kravene til moderne datakommunikasjon innen felt som datasentre, nettverk og høyytelses databehandling. Med vekt på applikasjonstilpassede løsninger, fleksibilitet og tilpasningsevne, kan SerDes skreddersys til spesifikke brukstilfeller, og viser dens evne til å optimalisere ytelsen for ulike applikasjoner og miljøer. Inkluderingen av en DSP understreker dens betydning i oppgaver som utjevning, feilkorrigering og signalkondisjonering. Designet for enkel integrering og tilpasning til ulike Plug and Play-moduler, sikrer arkitekturen sømløs kompatibilitet med forskjellige komponenter og funksjoner. Som en høyhastighets kommunikasjonsløsning oppfyller arkitekturen de skiftende kravene til datahastigheter og er på linje med fremskritt innen kommunikasjonsstandarder, noe som gjør den godt egnet for dynamiske og fremtidsorienterte kommunikasjonsmiljøer.

AthenaCORE 224G SerDes TestChip-resultater

Alphawaves innovative utviklingsarbeid

Alphawaves 200G-sammenkoblingsteknologier handler ikke bare om hastighet, men også om effektivitet og pålitelighet. 200G-sammenkoblingsutfordringene inkluderer signalintegritetsproblemer, krysstale og spredning. Selskapet investerer i avanserte modulasjonsordninger, som PAM4 (Pulse Amplitude Modulation 4) som lar flere biter kodes i et enkelt symbol, noe som effektivt øker datahastigheten. Alphawave distribuerer også avanserte DSP-teknikker og adaptive feilrettingsskjemaer for å forbedre påliteligheten og ytelsen til dataoverføring ved 200G-hastigheter.

Avanserte DSP-teknikker

Maximum Likelihood Sequence Detectors (MLSD) representerer en sofistikert digital signalbehandling (DSP)-teknikk som brukes i kommunikasjonssystemer, spesielt effektiv i scenarier med intersymbolinterferens (ISI). I motsetning til konvensjonelle metoder som tar sikte på å eliminere ISI, utnytter MLSD på en unik måte energien i interferens for å øke signalstyrken, og optimalisere symbolsekvensdeteksjon. Dens matematisk optimale tilnærming innebærer et uttømmende søk over alle mulige symbolsekvenser, og minimerer gjennomsnittlig kvadratfeil for å identifisere den overførte sekvensen. Anerkjent for sin kapasitet til å forbedre systemytelsen betydelig, brukes MLSD spesielt i høyhastighets datakommunikasjon og optisk kommunikasjon, og adresserer bekymringer knyttet til signalforvrengning på grunn av ISI. Mens MLSDs beregningskrav reiser kompleksitetshensyn, understreker teknikkens tilpasningsevne til varierende kanalforhold dens effektivitet i dynamiske kommunikasjonsmiljøer.

Forward Error Correction (FEC)-strategier

Alphawave omfavner adaptive Forward Error Correction (FEC)-strategier, som tillater dynamiske justeringer basert på sanntidskanalforhold. Denne fleksibiliteten sikrer optimal ytelse uten at det går på bekostning av båndbreddeeffektiviteten. FEC gir systemer mulighet til å etablere høyere Bit Error Rate (BER)-mål på elektriske koblinger, og gir en terskel for å tolerere og korrigere feil. Adaptiv FEC justerer dynamisk feilkorreksjonsstyrke, balanseringskorreksjon og båndbreddeeffektivitet basert på sanntids kanalforhold. Oppstigningen av adaptive og dynamiske FEC-strategier forbedrer systemets tilpasningsevne, mens integrasjon med avanserte modulasjonsskjemaer optimerer ytelsen, spesielt i høyhastighets og optiske kommunikasjonssystemer.

Allsidige alternativer for å støtte 1.6T-økosystemet

Alphawave gir allsidige alternativer for switch-ASIC-er (Application-Specific Integrated Circuits) i 1.6T-økosystemet. Dette inkluderer muligheten til å holde seg til 512 × 100G-koblinger eller utnytte 256 x 200G-koblinger i en 1RU – 32 Port Switch-konfigurasjon, som tilbyr skalerbarhet og fleksibilitet for forskjellige distribusjonsscenarier. Selskapets UCle-aktiverte brikker åpner for nye muligheter for modularitet og skalerbarhet på brikkenivå for å møte høyhastighetsminne og datakrav for infrastrukturapplikasjoner. Med sin 2.5D/3D-emballasje og applikasjonsoptimerte IP, navigerer selskapet i den delikate balansen mellom kompleksitet og ytelse for å levere avanserte løsninger.

Interoperabilitet med flere leverandører

Interoperabiliteten oppmuntrer til innovasjon og spenner over ulike dimensjoner, inkludert formfaktorer, SerDes-grensesnitt og administrasjonsprogramvare, med det endelige målet om å oppnå systemkompatibilitet. Interoperabilitet med flere leverandører er en kritisk faktor for å ta i bruk og lykkes med ny teknologi. Tidlige brukere drar nytte av et bredere utvalg av kompatible produkter, mens nedstrømsimplementere utnytter interoperabilitet for å strømlinjeforme utviklingen, redusere tid og kostnader. Ved å sette ytelsesstandarder, sikrer interoperabilitet at brukere kan forutse hvordan ulike komponenter vil fungere sammen i et system. Dette fremmer raskere tilgang til billigere teknologi, drevet av konkurranse i et mangfoldig økosystem av interoperable løsninger.

Arbeide med standardiseringsorganer

Alphawave forstår viktigheten av interoperabilitet mellom flere leverandører og engasjerer seg aktivt med industristandardorganer som OIF (Optical Internetworking Forum) og IEEE 802.3 for å bidra til utviklingen av 200G-signalstandarder. Dette samarbeidet sikrer interoperabilitet og setter scenen for sømløs integrering av Alphawaves teknologier i det bredere økosystemet. Alphawaves robuste spesifikasjoner og overholdelse av industristandarder sikrer at 200G-sammenkoblingsteknologiene sømløst integreres med en rekke systemer.

Oppsummering

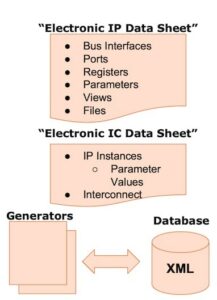

Ved å aktivt bidra til industristandarder, investere i avanserte teknologier og tilby allsidige løsninger, er Alphawave en viktig aktør i å gjøre 1.6T-økosystemet mainstream for tiden med kunstig intelligens. Alphawave tilbyr en omfattende pakke med løsninger designet for tilkobling med høy ytelse. Deres High-Performance Connectivity IP spenner over viktige områder som PCIe/CXL, Ethernet og HBM/DDR, og tilfredsstiller kravene til høyhastighets datakommunikasjon. Inkorporeringen av chipletteknologi, spesielt ved å utnytte UCle, indikerer en forpliktelse til sømløs chiplet-sammenkobling. De spesifikke chiplet-typene – IO, Memory og Compute – understreker en modulær tilnærming, som lar forskjellige chiplets fungere harmonisk sammen.

Ettersom dataintensive applikasjoner fortsetter å utvikle seg, posisjonerer Alphawaves forpliktelse til innovasjon det som en nøkkelmuliggjører for morgendagens høyhastighets, pålitelige og skalerbare AI-datainfrastruktur. I hovedsak er Alphawave en nøkkelspiller for å muliggjøre fleksibilitet, skalerbarhet og innovasjon for det kommende 1.6T-økosystemet.

For å lytte til webinaret, besøk her.

Les også:

Disaggregerte systemer: Aktiverer databehandling med UCIe Interconnect og Chiplet-basert design

Grensesnitt-IP i 2022: 22 % årlig vekst fortsatt datasentrert

Alphawave Semi-besøk på #60DAC

Del dette innlegget via:

- SEO-drevet innhold og PR-distribusjon. Bli forsterket i dag.

- PlatoData.Network Vertical Generative Ai. Styrk deg selv. Tilgang her.

- PlatoAiStream. Web3 Intelligence. Kunnskap forsterket. Tilgang her.

- PlatoESG. Karbon, CleanTech, Energi, Miljø, Solenergi, Avfallshåndtering. Tilgang her.

- PlatoHelse. Bioteknologisk og klinisk etterretning. Tilgang her.

- kilde: https://semiwiki.com/ip/alphawave/339080-unleashing-the-1-6t-ecosystem-alphawave-semis-200g-interconnect-technologies-for-powering-ai-data-infrastructure/

- : har

- :er

- :ikke

- $OPP

- 1

- 1.

- 2022

- 32

- a

- evne

- Om oss

- adgang

- oppnå

- tvers

- aktivt

- tilpasning

- adaptive

- adresse

- adresser

- adressering

- binding

- justeringer

- adoptere

- Adopsjon

- avansert

- fremskritt

- fremover

- AI

- AI-data

- sikte

- algoritmer

- Justerer

- Alle

- tillate

- tillater

- allerede

- også

- an

- og

- forutse

- søknader

- anvendt

- tilnærming

- tilnærminger

- arkitektur

- ER

- områder

- kunstig

- kunstig intelligens

- Kunstig intelligens (AI)

- AS

- stigning

- Asics

- assosiert

- At

- Balansere

- balansering

- Båndbredde

- basert

- BE

- vært

- nytte

- mellom

- Bit

- organer

- øke

- bredere

- bygget

- men

- by

- som heter

- CAN

- Kapasitet

- saker

- catering

- Sentre

- utfordringer

- Kanal

- samarbeid

- samarbeids

- kombinasjon

- engasjement

- Kommunikasjon

- kommunikasjonssystemer

- kommunikasjon

- Selskapet

- Selskapets

- kompatibilitet

- kompatibel

- konkurranse

- komplekse

- kompleksiteten

- kompleksitet

- komponenter

- omfattende

- kompromittere

- beregnings

- Beregn

- databehandling

- bekymringer

- forhold

- Konfigurasjon

- Tilkobling

- betraktninger

- fortsette

- bidra

- medvirkende

- konvensjonell

- Kostnader

- kritisk

- avgjørende

- skjøger

- skjærekant

- dato

- datasentre

- datainfrastruktur

- datasett

- leverer

- Etterspørsel

- krav

- distribusjon

- Distribueres

- utforming

- designet

- Gjenkjenning

- Utvikling

- forskjellig

- digitalt

- dimensjoner

- Dispersion

- diverse

- doblet

- drevet

- kjøring

- to

- dynamisk

- dynamisk

- Tidlig

- tidlig adopters

- lette

- lett

- økosystem

- Effektiv

- effektivt

- effekten

- effektivitet

- innsats

- eliminere

- Omfavner

- vekt

- ansatt

- myndiggjøring

- bemyndiger

- enabler

- muliggjør

- muliggjør

- energi

- engasjerer

- konstruert

- forbedre

- Forbedrer

- nok

- sikre

- sikrer

- miljøer

- Era

- feil

- feil

- essens

- etablere

- Selv

- utvikle seg

- utvikling

- strekker

- faktor

- faktorer

- FAST

- Featuring

- Felt

- fleksibilitet

- Til

- teten

- skjema

- Forum

- Forward

- foster

- fra

- funksjon

- funksjonalitet

- framtid

- mål

- Vekst

- her.

- høy ytelse

- høyere

- vert

- Hvordan

- HTTPS

- identifisere

- IEEE

- betydning

- viktig

- in

- inkludere

- inkluderer

- Inkludert

- inkludering

- økende

- indikerer

- bransjer

- industri

- industristandarder

- Infrastruktur

- Innovasjon

- innovative

- integrere

- integrert

- integrering

- integritet

- Intelligens

- grensesnitt

- forstyrrelser

- Interoperabilitet

- interoper

- inn

- investere

- investerer

- innebærer

- IP

- saker

- IT

- DET ER

- nøkkel

- nøkkelspiller

- landskap

- Leverage

- utnytte

- i likhet med

- sannsynligheten

- lenker

- Se

- Mainstream

- Making

- ledelse

- marked

- massive

- matematisk

- max bredde

- bety

- møter

- Minne

- metoder

- minimere

- Moderne

- modulære

- Moduler

- mer

- flere

- navigerer

- Trenger

- nødvendig

- nettverk

- aldri

- Ny

- Ny teknologi

- spesielt

- of

- tilby

- tilbud

- Tilbud

- on

- bare

- åpner

- drift

- optimal

- Optimalisere

- Optimaliserer

- optimalisere

- alternativer

- or

- enn

- overvinne

- emballasje

- spesielt

- for

- ytelse

- plato

- Platon Data Intelligence

- PlatonData

- Spille

- spiller

- støpsel

- plug and play

- stillinger

- muligheter

- mulig

- Post

- makt

- Slå

- prosessering

- prosessor

- Produkter

- Propell

- utprøvd

- gir

- gi

- puls

- raskere

- heve

- område

- raskt

- Sats

- priser

- Lese

- sanntids

- riket

- gjenkjent

- gjenkjenner

- redusere

- i slekt

- pålitelighet

- pålitelig

- bemerkelsesverdig

- representere

- Krav

- Resultater

- Revolution

- robust

- skalerbarhet

- skalerbar

- scenarier

- ordninger

- sømløs

- sømløst

- Søk

- Sekund

- Semi

- Sequence

- sett

- innstilling

- delt

- utstillingsvindu

- Signal

- betydning

- betydelig

- enkelt

- Software

- løsning

- Solutions

- sofistikert

- spenn

- spesifikk

- spesifikasjoner

- fart

- hastigheter

- kvadrat

- Scene

- standarder

- står

- blir

- Stick

- Still

- strategier

- effektivisere

- styrke

- strengere

- suksess

- slik

- suite

- støtte

- Bytte om

- symbol

- system

- Systemer

- skreddersydd

- tar

- mål

- oppgaver

- teknikk

- teknikker

- Technologies

- Teknologi

- testament

- Det

- De

- Fremtiden

- deres

- denne

- terskel

- tid

- til

- sammen

- i morgen

- Tema

- mot

- overføre

- ultimate

- understreker

- forstår

- unikt

- utløsningen

- I motsetning til

- enestående

- kommende

- upon

- bruke

- Brukere

- innvarsling

- variasjon

- ulike

- Varierende

- allsidig

- av

- Besøk

- webinar

- hvilken

- mens

- vil

- med

- innenfor

- uten

- X

- zephyrnet