Med et økende antall selskaper som er interessert i enheter basert på RISC-V ISA, og et økende antall kjerner, akseleratorer og infrastrukturkomponenter som gjøres tilgjengelig, enten kommersielt eller i åpen kildekode-form, står sluttbrukere overfor en stadig vanskeligere utfordring med å sikre at de tar de beste valgene.

Hver bruker vil sannsynligvis ha et sett med behov og bekymringer som nesten tilsvarer fleksibiliteten til RISC-V-tilbudene, og strekker seg langt utover tradisjonelle PPA-beregninger til sikkerhets- og sikkerhetshensyn eller kvalitetshensyn. Det kan inkludere tilpasningsevnen til verifikasjonssikkerheten, som gjør det mulig for den arkitektoniske utvidelsen og den nødvendige verifiseringen å følge med.

Tradisjonelt har tre nivåer av prototyping blitt distribuert - virtuelle prototyper, emulering og FPGA-prototyper, inkludert hybrider mellom dem. Hver plattform brukes deretter til en rekke formål, inkludert programvareverifisering, arkitektonisk validering, funksjonell verifisering av maskinvaren, ytelsesanalyse og mer.

Mens design- og programvareøkosystemene for RISC-V blir etablert, er konfigurasjons- og verifiseringsøkosystemene etterfølgende og krever at ny teknologi bygges. Det er selve fleksibiliteten til RISC-V som skaper store utfordringer for verifisering, utover det som kreves for verifisering av faste prosessorer. Det gjør også samutvikling av maskinvare og programvare ikke bare mulig, men nødvendig.

Samutvikling

Tidligere ble maskinvare valgt og deretter utviklet programvare for å kjøre på den. Med RISC-V er maskinvaren ofte drevet av programvare. "Det første du må velge er hvilke standard RISC-V-alternativer du vil ha," sier Simon Davidmann, grunnlegger og administrerende direktør for Imperas programvare. "RISC-V-funksjonssettet har for øyeblikket 200 eller 300 alternativer. Hvordan vet du om algoritmen din vil ha nytte av en flyttallsenhet, eller SIMD, maskinvaremultiplikatorer eller til og med en vektormotor? Du må finne ut hvilke maskinvarefunksjoner du trenger, og har råd til, for den typen applikasjon eller jobben du vil at prosessoren skal gjøre. Det i seg selv blir litt av en utfordring."

Det kreves prototyper for å gjøre slike avveininger. "Hvis designerens mål er å evaluere ytelse og egnethet til formålet, så er virtuell prototyping det eneste levedyktige valget," sier Steve Roddy, CMO ved andregradsflate. "Å bygge maskinvareprototyper er mer enn 10 til 50 ganger mer tidkrevende enn å lage en SystemC-modell av et undersystem eller hele SoC. Den virtuelle SystemC-prototypen kjører generelt raskt nok til å svare på ytelsesspørsmål, for eksempel hvor mange bilder per sekund med gjennomstrømning kan jeg få med denne prosessorkjernen, eller hva er topp- og gjennomsnittsbåndbreddekravet til funksjon X, innenfor en akseptabel nøyaktighet.

Å få riktig nøyaktighet kan være vanskelig. "Det handler om nøyaktighet og din evne til å spinne en modell veldig raskt," sier Frank Schirrmeister, visepresident for løsninger og forretningsutvikling hos Arteris IP. «Riktig nøyaktighet er definert av hva spørsmålet ditt krever, og å generere disse er ikke trivielt. Hvis du er en ASIP-leverandør, vil du kunne generere disse fra hvilken mal du har. Avhengig av spørsmålet kan du trenge pipeline-nøyaktighet, du kan trenge minnenøyaktighet, den trenger ikke være helt nøyaktig, men når du har en CAD-avdeling involvert, er de for redde for å svare på feil spørsmål.»

Men nøyaktighet er en avveining mot hastighet. "Selv om noen virtuelle prototyper er syklusnøyaktige, kjører disse ofte for sakte til å kunne ha den nødvendige programvaregjennomstrømningen," sier Davidmann fra Imperas. "De virtuelle prototypene med høyest ytelse er ikke ytelsesmotorer, fordi de ikke modellerer prosessorpipelines. De ser på det fra et programvaresynspunkt, der du kan kompilere det og kjøre det på maskinvare, og du kan se omtrentlig ytelse ved å se på antall instruksjoner eller omtrentlige tidsberegninger. Dette burde være nok til å ta denne typen arkitektoniske beslutninger.»

Det krever ofte flere prototyper. "Vi prototyper vanligvis av to grunner," sier Venki Narayanan, seniordirektør for programvare og systemutvikling i Microchip Technologys FPGA-forretningsenhet. "Den ene er for arkitektonisk validering for å sikre at vi oppfyller alle ytelsesmålinger og -krav og funksjonell validering. Den andre grunnen er innebygd programvare og fastvareutvikling. Vi bruker ulike nivåer av prototyping-teknikker, hvor det vanligste er å bruke våre egne FPGAer for å utvikle en emuleringsplattform for både arkitektonisk og funksjonell validering. Vi bruker også arkitektoniske modeller som QEMU for å bygge virtuelle plattformer for både ytelsesvalidering og innebygd programvareutvikling."

Antallet muligheter vokser. "Det er mange måter bedrifter lager prototyper med RISC-V på i dag," sier Mark Himelstein, CTO for RISC-V International. "Disse spenner fra enkeltkortdatamaskiner på produsentnivå, til LINUX-kompatible brett. Emuleringsmiljøer (som QEMU) lar utviklere komme videre med programvare før maskinvaren deres er fullført, og det er hyllevaredeler overalt fra innebygde SoC-er (fra selskaper som Espressif og Telink), til FPGA-er (fra selskaper som Microsemi), til det kommende Horse Creek-styret fra Intel og SiFive.»

Det kommer tilbake til avveiningen mellom ytelse og nøyaktighet. "Fysiske prototyper krever mye mer designarbeid, fordi du kobler til og syntetiserer ekte RTL, men de leverer langt større nøyaktighet og gjennomstrømning," sier Quadrics Roddy. "En fysisk prototype i et FPGA-system, enten det er hjemmelaget eller fra de store EDA-selskapene, krever innsats å få opp. Men den kan kjøre en størrelsesorden raskere enn en SystemC-modell, og flere størrelsesordener raskere enn simulering på full gatenivå. Designteam vil vanligvis pivotere fra C-baserte modeller under IP-utvelgelsesprosessen til fysiske modeller for både verifisering av det faktiske designet etter IP-valg, og som en utviklingsplattform for systemprogramvare."

Når du vet hvilket funksjonssett du vil ha i maskinvaren, kan du se om noen allerede har laget en løsning som oppfyller de fleste behovene dine. "Sjansene er at med alle leverandørene der ute, vil det være en kommersiell løsning som vil ha den typen ting du leter etter," sier Davidmann. "Men med RISC-V trenger du ikke å akseptere den løsningen som den er. En betydelig del av verdien med RISC-V er friheten til å endre den, modifisere den og legge til forskjellige ting du vil ha."

Velge en implementering

Det er mange måter å implementere et sett med funksjoner på, for eksempel antall pipeline-trinn eller spekulative utførelsesfunksjoner. Hver vil ha en annen avveining mellom kraft, ytelse og område. "ISA-smaken, det være seg RISC-V, Arm, Cadence's Xtensa, Synopsys' ARC, påvirker egentlig ikke målene for modellering og prototyping og avveininger," sier Roddy. "En systemarkitekt må svare på spørsmål om SoC-designmål uavhengig av prosessormerke. På et teknisk nivå er RISC-V-vognen virkelig i en stabil posisjon i markedet i forhold til støtte for modellering og ytelsesanalyse. Det er mange konkurrerende kjerneleverandører, hver med forskjellige implementeringer og prosessorfunksjoner. Som en hovedsystem-CPU har den ikke lang levetid som en arm, og derfor har færre økosystemaktører i EDA-verdenen bredt validert, klar til bruk modelleringsstøtte for hyllevare RISC-V-kjerner fra utvalget av RISC-V-leverandører. Som en konfigurerbar, modifiserbar kjerne, henger RISC-V-verdenen etter nivået av instruksjonssett-automatisering som Tensilica har brukt 25 år på å bygge. Dermed har RISC-V mindre modelleringsstøtte som en ferdig byggekloss og mindre automatisering å bruke som en plattform for instruksjonssetteksperimentering.»

Men det er bare ett aspekt ved en implementering som må vurderes. Hva er kvaliteten på den? Hvis du vil endre den, hvordan revaliderer du den?

Ytelse er den enkleste av disse å vurdere. "Dette er ikke annerledes enn å gå til en hvilken som helst tradisjonell prosessorleverandør," sier Davidmann. "De vil fortelle deg at denne kjernen gir deg så mange Dhrystones per watt, de vil gi deg typiske prosessoranalytiske data, som sier at dette er hvor raskt denne mikroarkitekturen kjører. De har alle disse dataene, og alle som lisensierer en prosessorkjerne vil være kjent med disse dataene og vil snakke med dem og få den informasjonen. De vil sannsynligvis ha mange valgbare alternativer i dataarket, og de vil si: 'Hvis du slår på dette alternativet, får du dette eller det.' Du kan se på det på dataarket, på nettstedene til leverandørene."

På dette nivået trenger du sannsynligvis syklusnøyaktighet. "Jeg ser at de fleste pumper den inn i en emulator og kjører nok data gjennom den til å ta en fornuftig avgjørelse," sier Schirrmeister. «Jeg ser ikke at det går opp til virtuelle prototyper med det første. Noen selskaper snakker om FPGA-prototyper, hvor du har din egen enkeltkortløsning. Avhengig av spørsmålet du trenger å svare på, kan du bestemme deg for å konfigurere det, generere det og deretter pumpe det inn i en FPGA for å kjøre mer data gjennom det, med de riktige programvarerutinene på toppen. Industrien har tilstrekkelig raske inngangsveier til emulatorer og prototyping for å gjøre dette mulig. Det grunnleggende problemet er at du vil ta denne avgjørelsen basert på så nøyaktige data du kan, men du har kanskje ikke de nøyaktige dataene på det tidspunktet du vil ta den avgjørelsen.»

Mange av disse prototypene må inneholde mer enn bare prosessoren. "Virtuelle plattformer gir muligheten til å integrere med andre eksterne fysiske maskinvarefunksjoner, som minne og sensorer som opererer i et virkelig miljø," sier Microchips Narayanan. «Hybride systemer kan bringe sammen virtuelle plattformer med fysiske prototyper for andre eksterne funksjoner. FPGA-emulering og prototyping hjelper til med å finne tidsrelaterte feil, for eksempel løpsforhold, ettersom dette er mer syklusnøyaktig og eksterne funksjoner kjører med hastighet.»

Verifisering

Fordi prosessordesign har vært internt i lang tid, er det ikke noe offentlig verifiseringsøkosystem for å bygge en prosessor, og funksjonene til RISC-V krever en mye mer fleksibel verifiseringsløsning enn noen gang har eksistert tidligere. Opprettelsen av dette begynner bare å skje.

"Det finnes industriberegninger som Dhrystones eller CoreMark, slik at folk kan sammenligne ytelse," sier Davidmann. "Men hvordan kan du sammenligne verifiseringskvalitet? Det må være like konkurransevilkår slik at hver leverandør kan si: "Dette er hvordan vi gjør det." Vi trenger noen kvalitetsmålinger for verifisering.»

Det er her åpen kildekode-bevegelsen kan hjelpe. "Hvis du ser på RISC-V-økosystemet, har du et stort antall svært erfarne prosessorutviklere," sier Schirrmeister. «Det er to ytterpunkter. En er at jeg får en kjerne fra en leverandør, og hvis det ikke fungerer, har du et problem med dem. På den andre enden har jeg total frihet og gjør alt selv. En likevekt utvikler seg et sted mellom disse to ytterpunktene. Du får noe der en viss mengde bekreftelse er gitt av leverandøren din, og deretter er utvidelsene ditt eget ansvar."

Og det er her beregninger kommer inn. "ISA-kompatibilitet er bare det første trinnet i en stige full av kompleksiteter som bare noen få selskaper har klatret på," sier Dave Kelf, administrerende direktør for Breker Verification Systems. "Prototyping kan være den eneste måten å sikre pålitelig prosessordrift på, men å utnytte reelle arbeidsbelastninger for å drive disse prototypene skraper overflaten av ekte prosessordekning. Dette er i strid med konkurransearbeidet til en åpen ISA som driver frem akselerert utvikling og tid til markedsproblemer.»

Men hva er disse beregningene? "I OpenHW-kvalitetsgruppen prøver vi å finne ut hva disse beregningene skal være," sier Davidmann. "Det inkluderer ting som funksjonell dekning, fordi det ikke bare er enkle instruksjoner. For en prosessor av høy kvalitet trenger du mye mer enn det. Du må ha en metodikk for verifisering, der det er tillit til at sammenligningene dine mot en referanse dekker alt. Funksjonell dekning viser bare at du har testen, men det må kombineres med en metodikk som sammenlignes med en form for kjent referanse. Vi kommer til å legge til feilinjeksjonsteknologi slik at det blir mulig å finne ut om testbenken din faktisk oppdager problemer.»

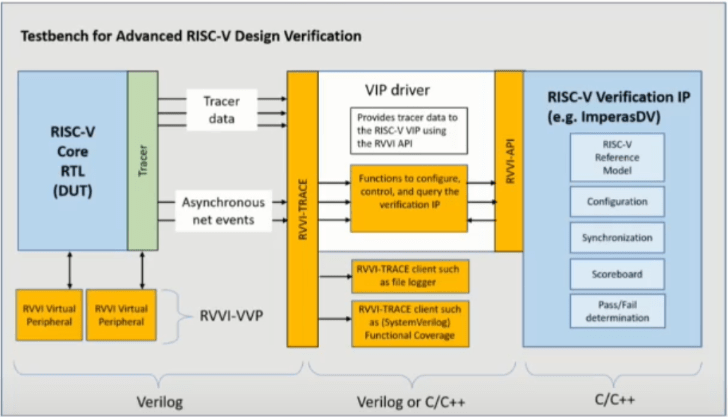

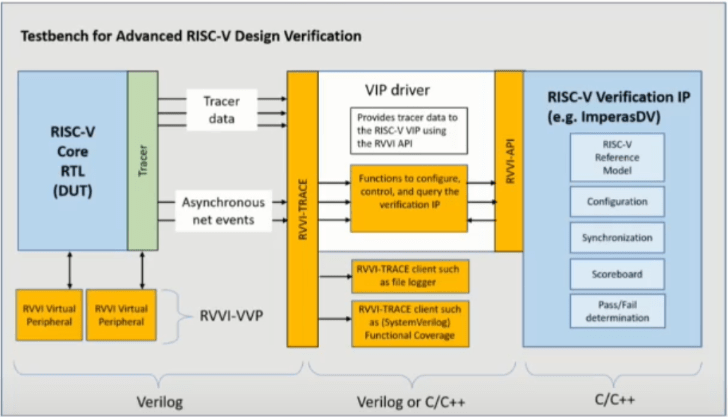

Fig. 1: Definere arkitekturen til en RISC-V-verifiseringsløsning. Kilde: Imperas

Det vil kreve en rekke verktøy. "Når RISC-V-økosystemet modnes, begynner kommersielle implementeringer å støtte definerte markedssegmenter," sier Ashish Darbari, grunnlegger og administrerende direktør for Axiomise. "Vi ser støtte for markeder, som bilindustrien, som krever samsvar med funksjonell sikkerhet. Vi ser støtte for IoT, som krever sikkerhet. RISC-V-leverandører investerer i avanserte verifiseringsteknikker, inkludert virtuell prototyping for arkitektonisk modellering og ytelse. Verktøy er nå tilgjengelige for tidlig bruk av formelle metoder for å beskjære feil tidlig i designprosessen og unngå feilinnsetting ettersom designere sliter med å fange opp feil i hjørnet med simulering på prosessor-minnegrensesnittet.»

Et av verktøyene som vil være nødvendig er muligheten til å generere testcaser basert på en funksjonsliste eller et sett med funksjoner. "Den automatiserte genereringen av testinnhold for å drive prototyper som tar hensyn til verifikasjonskompleksitetene i tide er nøkkelen," sier Breker's Kelf. "Disse generasjonsmekanismene begynner nå å dukke opp på markedet."

konklusjonen

Et økosystem er bare så godt som sin svakeste komponent, og for RISC-V er det EDA-verktøykjeden. Årsakene til dette er todelt. For det første, inntil nylig, var det ikke noe kommersielt marked for prosessorverifiseringsverktøy. Mens de eksisterte i fortiden, hadde de alle enten forsvunnet eller blitt oppløst i de eldre prosessorselskapene. For det andre skaper fleksibiliteten til RISC-V ISA en ny optimaliseringstilnærming på systemnivå som krever et nytt sett med verktøy. Det tar tid før denne muligheten blir forstått og for kommersielle verktøy dukker opp som adresserer den på riktig måte.

I slekt

En minimal RISC-V

Er det plass til en enda mindre versjon av en RISC-V-prosessor som kan erstatte 8-bits mikrokontrollere?

RISC-V skyver inn i hovedstrømmen

Åpen kildekode prosessorkjerner begynner å dukke opp i heterogene SoCs og pakker.

Effektiv sporing i RISC-V

Hvordan jobbe med den nye RISC-V feilsøkingsstandarden.

Hvor sikre er RISC-V-brikker?

Åpen kildekode i seg selv garanterer ikke sikkerhet. Det kommer fortsatt ned til det grunnleggende i design.

- SEO-drevet innhold og PR-distribusjon. Bli forsterket i dag.

- Platoblokkkjede. Web3 Metaverse Intelligence. Kunnskap forsterket. Tilgang her.

- kilde: https://semiengineering.com/selecting-the-right-risc-v-core/

- 1

- 10

- a

- evne

- I stand

- Om oss

- ovenfor

- akselerert

- akseleratorer

- Aksepterer

- akseptabelt

- Logg inn

- nøyaktighet

- nøyaktig

- faktisk

- adresse

- Adopsjon

- avansert

- Etter

- mot

- algoritme

- Alle

- allerede

- beløp

- analyse

- Analytisk

- og

- og infrastruktur

- besvare

- vises

- Søknad

- tilnærming

- hensiktsmessig

- Arc

- arkitektonisk

- arkitektur

- AREA

- ARM

- aspektet

- vurderes

- Automatisert

- Automatisering

- automotive

- tilgjengelig

- gjennomsnittlig

- tilbake

- Båndbredde

- basert

- grunnleggende

- fordi

- blir

- bli

- før du

- Begynnelsen

- være

- nytte

- BEST

- mellom

- Beyond

- Stor

- Bit

- Blokker

- borde

- merke

- bringe

- bredt

- Bug

- bugs

- bygge

- Bygning

- bygget

- virksomhet

- forretningsutvikling

- CAD

- evner

- stand

- Catch

- konsernsjef

- viss

- utfordre

- utfordringer

- sjansene

- endring

- chips

- valg

- valg

- Velg

- klatret

- CMO

- Collateral

- Kom

- kommersiell

- kommersielt

- Felles

- Selskaper

- sammenligne

- kompatibilitet

- konkurrerende

- konkurranse

- fullføre

- kompleksiteten

- samsvar

- komponent

- komponenter

- datamaskiner

- bekymringer

- forhold

- selvtillit

- Konfigurasjon

- Tilkobling

- betraktninger

- innhold

- Kjerne

- kunne

- kombinert

- dekning

- dekker

- prosessor

- opprettet

- skaper

- Opprette

- skaperverket

- Creek

- CTO

- I dag

- dato

- Dave

- avgjørelse

- definere

- leverer

- krav

- Avdeling

- avhengig

- utplassert

- utforming

- design prosess

- designere

- utvikle

- utviklet

- utviklere

- utvikle

- Utvikling

- Enheter

- forskjellig

- vanskelig

- Regissør

- ikke

- ikke

- ned

- stasjonen

- drevet

- kjøring

- under

- hver enkelt

- Tidlig

- enkleste

- økosystem

- økosystemer

- innsats

- innsats

- enten

- innebygd

- muliggjør

- Motor

- Ingeniørarbeid

- Motorer

- nok

- sikre

- sikrer

- Enterprise

- Hele

- entry

- Miljø

- miljøer

- Er lik

- Equilibrium

- etablert

- estimater

- evaluere

- Selv

- NOEN GANG

- alt

- gjennomføring

- erfaren

- strekker

- forlengelse

- utvidelser

- utvendig

- ytterpunktene

- Face

- kjent

- Mote

- FAST

- raskere

- Trekk

- Egenskaper

- Noen få

- felt

- Fiken

- Finn

- finne

- Først

- passer

- fikset

- fleksibilitet

- fleksibel

- skjema

- formell

- Grunnleggeren

- Grunnlegger og administrerende direktør

- FPGA

- Frihet

- fra

- fullt

- fullt

- funksjon

- funksjonelle

- funksjoner

- Fundamentals

- generelt

- generere

- genererer

- generasjonen

- få

- få

- Gi

- gir

- Go

- Mål

- skal

- god

- større

- Gruppe

- Økende

- garantere

- skje

- maskinvare

- hjelpe

- hjelper

- høykvalitets

- hjemmelaget

- Hest

- Hvordan

- HTTPS

- stort

- Påvirkning

- iverksette

- gjennomføring

- in

- inkludere

- inkluderer

- Inkludert

- økende

- stadig

- industri

- informasjon

- Infrastruktur

- instruksjoner

- integrere

- Intel

- interessert

- Interface

- internasjonalt

- investere

- involvert

- IOT

- IP

- saker

- IT

- selv

- Jobb

- nøkkel

- Type

- Vet

- kjent

- stigen

- stor

- Legacy

- Nivå

- nivåer

- utnytte

- Lisensiering

- Sannsynlig

- linux

- Liste

- Lang

- lang tid

- levetid

- Se

- ser

- laget

- Hoved

- gjøre

- maker

- GJØR AT

- mange

- merke

- marked

- Markets

- modnes

- max bredde

- Møt

- Minne

- metodikk

- metoder

- Metrics

- minimal

- modell

- modellering

- modeller

- modifisere

- mer

- mest

- bevegelse

- flytting

- nødvendig

- Trenger

- behov

- Ny

- Antall

- mange

- Målet

- odds

- tilbud

- ONE

- åpen

- åpen kildekode

- drift

- drift

- Opportunity

- optimalisering

- Alternativ

- alternativer

- rekkefølge

- ordrer

- Annen

- egen

- pakker

- del

- deler

- Past

- Topp

- porsjoner

- ytelse

- fysisk

- rørledning

- Pivot

- plattform

- Plattformer

- plato

- Platon Data Intelligence

- PlatonData

- spillere

- spiller

- Point

- Synspunkt

- posisjon

- muligheter

- mulig

- makt

- president

- sannsynligvis

- Problem

- problemer

- prosess

- prosessor

- prosessorer

- Progress

- riktig

- prototype

- prototyper

- prototyping

- gi

- forutsatt

- leverandør

- offentlig

- pumpe

- pumping

- formål

- formål

- kvalitet

- spørsmål

- spørsmål

- Race

- område

- ferdige

- ekte

- virkelige verden

- grunnen til

- rimelig

- grunner

- nylig

- Uansett

- pålitelig

- erstatte

- krever

- påkrevd

- behov

- Krav

- Krever

- ansvar

- rom

- Kjør

- rennende

- Sikkerhet

- Trygghet og sikkerhet

- Sekund

- sikre

- sikkerhet

- segmenter

- valgt

- velge

- utvalg

- senior

- sensorer

- sett

- flere

- bør

- Vis

- Viser

- signifikant

- Simon

- Enkelt

- simulering

- enkelt

- Sakte

- mindre

- So

- Software

- programvareutvikling

- løsning

- Solutions

- noen

- Noen

- noe

- et sted

- Snart

- kilde

- fart

- brukt

- Snurre rundt

- stabil

- stadier

- Standard

- Start

- Steve

- Still

- Struggle

- slik

- suite

- støtte

- overflaten

- system

- Systemer

- Ta

- tar

- Snakk

- snakker

- lag

- Teknisk

- teknikker

- Teknologi

- mal

- test

- De

- deres

- derfor

- ting

- ting

- tre

- Gjennom

- gjennomstrømning

- tid

- tidkrevende

- ganger

- timing

- til

- i dag

- sammen

- også

- verktøy

- topp

- Totalt

- spore

- tradisjonelle

- SVING

- typisk

- typisk

- forstås

- enhet

- kommende

- bruke

- Bruker

- Brukere

- validert

- validering

- verdi

- variasjon

- leverandør

- leverandører

- Verifisering

- versjon

- levedyktig

- Vice President

- Se

- virtuelle

- virtuelle plattformer

- ønsker

- måter

- nettsteder

- Hva

- Hva er

- om

- hvilken

- mens

- vil

- innenfor

- Arbeid

- trene

- verden

- ville

- Feil

- X

- år

- Din

- zephyrnet