På det nylige RISC-V-toppmøtet var den aller siste økten et panel om chiplets kalt Chiplets i RISC-V-økosystemet. Det ble moderert av Calista Redmond, administrerende direktør i RISC-V International. Paneldeltakerne var:

- Laurent Moll, COO i Arteris

- Aniket Saha, VP of Product Management i Tenstorrent

- Dale Greenley, VP for Engineering of Ventana Microsystems

- Rob Aitken, fremtredende arkitekt for Synopsys

Dette er en litt merkelig kombinasjon av emner for meg. Selvfølgelig kan du sette en RISC-V-prosessor på en brikke, men utfordringene er egentlig ikke forskjellige fra noen annen prosessor. Men RISC-V er hot og det samme er chiplets, og selskaper som Ventana kombinerer dem.

La meg gi deg litt bakgrunn om selskapene for å sette dem i sammenheng:

- Som du sikkert vet, lager Arteris nettverk-på-brikke (NoCs). Det er et nøytralt selskap blant chiplet-leverandører (og IP-leverandører).

- Tenstorrent designer en portefølje av meget høyytelses multicore RISC-V-brikker

- Ventana har RISC-V IP, men den leverer den også som chiplets

- Synopsys er åpenbart et EDA-selskap, men de annonserte RISC-V-kjerner tidligere på toppmøtet

]

Den faktiske diskusjonen

Det første spørsmålet fra Calista var en softball som spurte hva som var verdien av chiplets.

Dale sa at det ikke var noe spesifikt om RISC-V for chiplets, men markedet bestemmer når du gjør store monolittiske ting eller chiplets. Det avhenger av hva en kunde vil betale deg for å gjøre. "Vi leverer både IP og chiplets, det er plass til begge."

Aniket sa at "å lage chiplets er ikke billig, men å gjøre chiplets og RISC-V er fleksibelt, og du kan komme opp med huggeprodukter raskt."

Laurent gikk for produksjonskostnader. NRE er svært viktig å holde under kontroll siden det ikke er mange som bygger 100M deler. Så det er flere leverandører involvert og en komplisert forsyningskjede. En SoC er kompleks, men chiplets er verre.

Rob påpekte heterogenitet som å legge til chiplets for RF og analog, ha en valgfri akselerator og så videre. Dette åpner potensielt nye markeder.

Calista fortsatte med å spørre om hvor vi er innen bilindustrien.

Aniket påpekte at bilindustrien er veldig konservativ, og nå er de aggressive når det gjelder plattformer som kan skaleres fra lavprisbiler til avanserte biler. Med chiplets har ingen egentlig vurdert funksjonell sikkerhet.

Rob gikk til romfart (ikke helt bil) og diskuterte hvordan det vanligvis er et fast fysisk volum definert for tiår siden. Det er vanskelig å få plass til ting.

Laurent: Bilselskaper er de ultimate katalogkundene, og chiplets lar dem ta det beste innen AI, radar, infotainment og så videre.

Hvordan får du programvaren til å kjøre?

Rob: Hvis du gjør systemet lite, er det greit. Men shopping i bilkatalogen gjør det vanskeligere.

Aniket: Relaterte en uttalelse "hvis du legger den til, vil vi ikke bruke den". Programvarestabler for biler vil støtte RISC-V om 5 år, noe som er raskt. Det tok Arm 15 år å komme dit.

Spørsmål: Hva trenger vi for tilkobling?

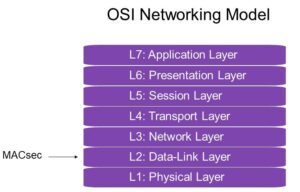

Laurent: Det er veldig komplekst, spesielt med folk som shopper etter chiplets. PHY-er fra forskjellige leverandører kan være interoperable. Alle er opptatt av UCIe. Folk vil ha standarder som gjør at chiplets passer bedre.

Aniket klaget over at det ikke finnes standard designflyter for chiplet. Stor mangel på standarder.

Rob tror vi kan komme opp med en standard flyt, men med forskjellige chiplets vil vi ikke ha N forskjellige designstrømmer.

Spørsmål: Hvor ser du ting om 3-5 år?

Rob: vi vil være videre sammen med forskjellige

«Katalogkjøp avhenger kanskje av OEM-er for biler. Det vil kreve mye bransjeinnsats. Alle heterogene ting vil ta lengre tid.

Aniket sa at chiplets først vil være i datasenteret og deretter i bilindustrien. Men første bølge vil være enkeltleverandør.

Oppsummering

Dette er en kombinasjon av ting deltakerne sa og mine egne meninger.

Jeg tror at foreløpig vil brikkebaserte RISC-V-design være enkeltselskapsinnsats (unntatt kanskje for høybåndbredde-minne (HBM). Det er for komplekst å bygge design med flere brikker fra forskjellige selskaper, interposers , og nettverket for å koble dem alle, vanligvis kjent som RDL.

Design vil være 2.5D, ikke ekte 3D (hvor terninger er stablet oppå hverandre og kommuniserer med gjennom-silisium-vias eller TSV-er) i overskuelig fremtid.

Automotive har sitt eget sett med utfordringer, spesielt for å sikre at chiplet-baserte design er pålitelige i et miljø med mye vibrasjon. Dette vil kreve omfattende testing. Et annet problem er å sikre funksjonell sikkerhet i et miljø med flere matriser.

UCIe er lovende og er noe basert på PCIe. PCIe-selskaper sikret pålitelighet gjennom plugfests. Jeg ser ikke hvordan du økonomisk kan sikre UCIe-interoperabilitet i chiplets gjennom en lignende mekanisme.

Til slutt, i tillegg til tekniske utfordringer, er det kommersielle utfordringer hvis vi skal komme til nirvana med å kunne kjøpe chiplets hyllevare og sette dem sammen til systemer til en rimelig pris. Den største utfordringen er hvem som skal betale for og holde beholdningen av chiplets. Hvis alle chiplets må produseres på forespørsel, vil mange av fordelene med en rask syklustid gå tapt.

Men RISC-V-chiplets kommer sikkert raskt i form av multi-die-design på 2.5D-interposers bygget av et enkelt selskap.

Les også:

NoC-er gir arkitekter fleksibilitet i system-i RISC-V-design

Paring av RISC-V-kjerner med NoC-er binder SoC-protokoller sammen

#60DAC-oppdatering fra Arteris

Del dette innlegget via:

- SEO-drevet innhold og PR-distribusjon. Bli forsterket i dag.

- PlatoData.Network Vertical Generative Ai. Styrk deg selv. Tilgang her.

- PlatoAiStream. Web3 Intelligence. Kunnskap forsterket. Tilgang her.

- PlatoESG. Karbon, CleanTech, Energi, Miljø, Solenergi, Avfallshåndtering. Tilgang her.

- PlatoHelse. Bioteknologisk og klinisk etterretning. Tilgang her.

- kilde: https://semiwiki.com/ip/arteris/338888-risc-v-and-chiplets-a-panel-discussion/

- : har

- :er

- :ikke

- :hvor

- $OPP

- 100M

- 15 år

- 15%

- 167

- 200

- 300

- 3d

- a

- I stand

- Om oss

- akselerator

- faktiske

- legge til

- legge

- tillegg

- fordeler

- Aerospace

- aggressiv

- siden

- AI

- Alle

- langs

- også

- blant

- an

- og

- annonsert

- En annen

- noen

- arkitekter

- ER

- ARM

- rundt

- AS

- spør

- spør

- At

- automotive

- bakgrunn

- basert

- BE

- være

- BEST

- Bedre

- Stor

- Biggest

- Bit

- både

- bygge

- Bygning

- bygget

- men

- by

- som heter

- CAN

- biler

- katalog

- konsernsjef

- Gjerne

- kjede

- utfordre

- utfordringer

- billig

- farge

- kombinasjon

- kombinere

- Kom

- kommer

- kommersiell

- kommunisere

- Selskaper

- Selskapet

- komplekse

- komplisert

- Koble

- Tilkobling

- konservativ

- ansett

- kontekst

- kontroll

- COO

- Kostnad

- Kostnader

- kunde

- syklus

- Datacenter

- tiår

- definert

- leverer

- avhengig

- avhenger

- utforming

- utforme

- design

- Die

- forskjellig

- diskutert

- diskusjon

- Fornem

- do

- gjør

- ikke

- hver enkelt

- Tidligere

- innsats

- slutt

- Ingeniørarbeid

- sikre

- sikres

- sikrer

- Miljø

- spesielt

- alle

- Unntatt

- omfattende

- FAST

- slutt

- Først

- passer

- fikset

- fleksibilitet

- fleksibel

- flyten

- Flows

- Til

- overskuelig

- skjema

- fra

- funksjonelle

- videre

- framtid

- få

- Gi

- Hard

- hardere

- Ha

- å ha

- Høy

- høy ytelse

- hold

- HOT

- Hvordan

- HTTPS

- i

- if

- viktig

- in

- industri

- internasjonalt

- Interoperabilitet

- interoper

- inn

- inventar

- involvert

- IP

- utstedelse

- IT

- DET ER

- jpg

- Keen

- Hold

- Vet

- kjent

- maling

- Siste

- la

- i likhet med

- lenger

- tapte

- Lot

- Lav

- gjøre

- GJØR AT

- ledelse

- produsert

- mange

- mange folk

- marked

- Markets

- max bredde

- Kan..

- kan være

- me

- mekanisme

- Monolithic

- mer

- flere

- my

- Trenger

- nettverk

- Nøytral

- Ny

- Nei.

- ingenting

- nå

- of

- on

- På etterspørsel

- ONE

- åpner

- Meninger

- or

- Annen

- ut

- egen

- panel

- paneldebatt

- deltakere

- Spesielt

- deler

- Betale

- Ansatte

- kanskje

- fysisk

- Plattformer

- plato

- Platon Data Intelligence

- PlatonData

- portefølje

- Post

- potensielt

- sannsynligvis

- prosessor

- Produkt

- produktledelse

- Produksjon

- Produkter

- lovende

- protokoller

- gi

- Kjøp

- sette

- spørsmål

- ganske

- radar

- Lese

- virkelig

- rimelig

- nylig

- i slekt

- pålitelighet

- pålitelig

- krever

- rom

- Kjør

- Sikkerhet

- Sa

- Skala

- se

- Session

- sett

- shoppere

- Shopping

- lignende

- siden

- enkelt

- liten

- So

- Software

- noe

- spesifikk

- stablet

- Stabler

- Standard

- standarder

- Uttalelse

- Summit

- levere

- forsyningskjeden

- støtte

- system

- Systemer

- Ta

- snakker

- Teknisk

- Testing

- Det

- De

- Dem

- deretter

- Der.

- de

- ting

- tror

- tenker

- denne

- Gjennom

- Ties

- tid

- til

- også

- tok

- topp

- temaer

- sant

- ultimate

- etter

- Oppdater

- bruke

- vanligvis

- verdi

- leverandør

- leverandører

- veldig

- av

- volum

- vp

- ønsker

- var

- Wave

- we

- gikk

- var

- Hva

- når

- hvilken

- HVEM

- vil

- med

- verre

- år

- du

- zephyrnet