En ny teknisk artikkel med tittelen "Non-Traditional Design of Dynamic Logics using FDSOI for Ultra-Efficient Computing" ble publisert av forskere ved University of Stuttgart, UC Berkeley, Indian Institute of Technology Kanpur og TU Munich, med finansiering fra German Research Foundation .

Abstrakt

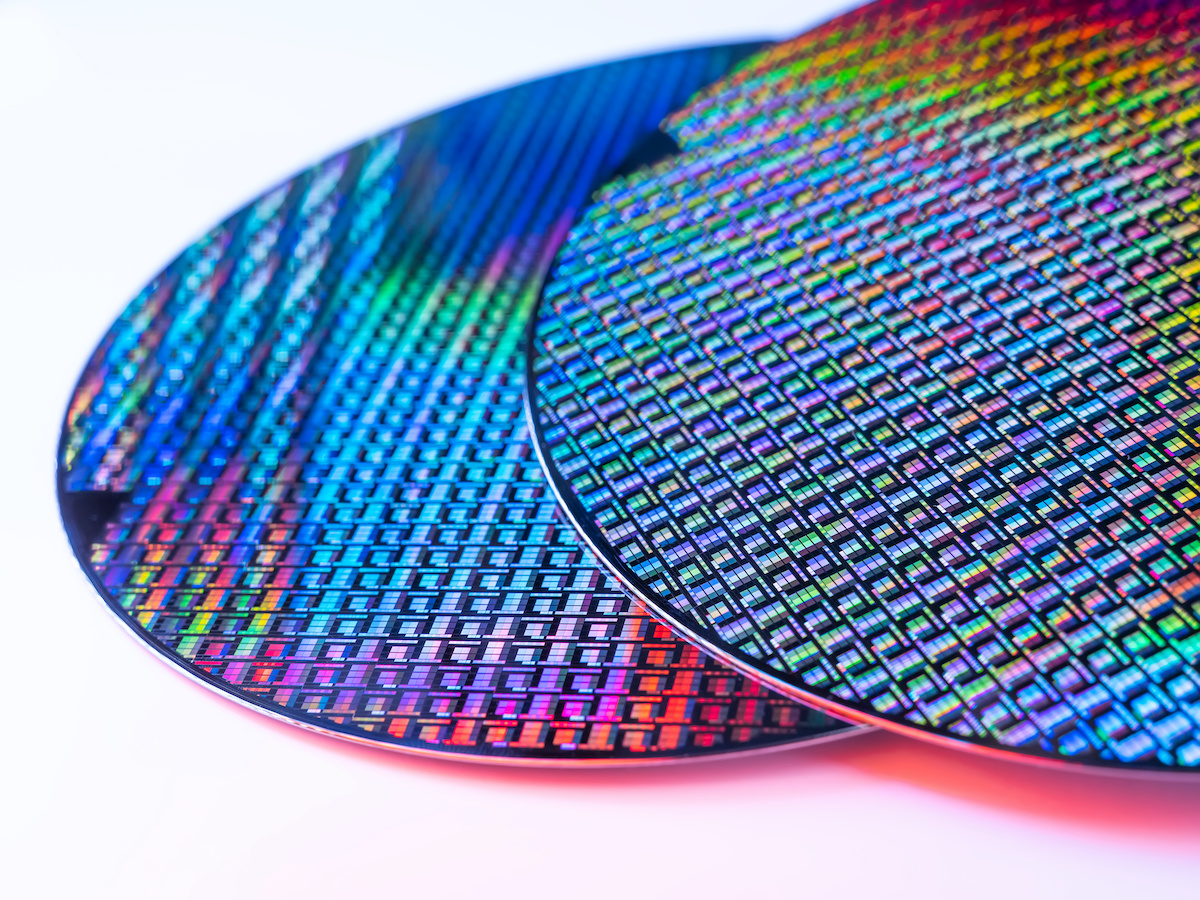

"I denne artikkelen foreslår vi en ikke-tradisjonell design av dynamiske logiske kretser som bruker FET-er med fullstendig uttømt silisium på isolator (FDSOI). FDSOI FET tillater terskelspenningen (Vt ) for å være justerbar (dvs. lav-Vt- og høy-Vt-tilstander) ved å bruke bakgate-bias. Vår design bruker front- og bakportene til en FDSOI FET som inngangsterminaler og foreslår de dynamiske logiske portene (som; NAND, NOR, AND, OR, XOR og XNOR) og kretser (som; halv adderer og full adderer). Det krever færre transistorer for å bygge dynamiske logiske porter og oppnår høy ytelse med lavt effekttap sammenlignet med konvensjonelle dynamiske logiske design. Den kompakte industrielle modellen til FDSOI FET (BSIM-IMG) har blitt brukt til å simulere dynamiske logiske porter og er fullstendig kalibrert for å reprodusere 14nm FDSOI FET-teknologinodedata. Kalibrering utføres for både elektriske egenskaper og prosessvariasjoner. Simuleringsresultatene viser en gjennomsnittlig forbedring i transistorantall, forplantningsforsinkelse, effekt og effektforsinkelsesprodukt på henholdsvis 23.43 %, 57.16 %, 47.05 % og 77.29 % sammenlignet med de konvensjonelle designene. Videre reduserer designen vår ladningsdelingseffekten, noe som påvirker kjørbarheten til de dynamiske logiske portene. I tillegg har vi analysert virkningen av prosessen, forsyningsspenning og belastningskapasitansvariasjoner på forplantningsforsinkelsen til den dynamiske logikkfamilien i detalj. Resultatene viser at disse variasjonene har en mindre innvirkning på utbredelsesforsinkelsen til de foreslåtte FDSOI-baserte dynamiske logiske portene sammenlignet med konvensjonelle dynamiske logiske porter."

Finn det teknisk papir her. Publisert april 2023.

S. Kumar, S. Chatterjee, CK Dabhi, YS Chauhan og H. Amrouch, "Non-Traditional Design of Dynamic Logics using FDSOI for Ultra-Efficient Computing," i IEEE Journal on Exploratory Solid-State Computational Devices and Circuits, doi: 10.1109/JXCDC.2023.3269141. Åpne Tilgangs.

- SEO-drevet innhold og PR-distribusjon. Bli forsterket i dag.

- PlatoAiStream. Web3 Data Intelligence. Kunnskap forsterket. Tilgang her.

- Minting the Future med Adryenn Ashley. Tilgang her.

- Kjøp og selg aksjer i PRE-IPO-selskaper med PREIPO®. Tilgang her.

- kilde: https://semiengineering.com/non-traditional-design-of-dynamic-logic-gates-and-circuits-with-fdsoi-fets/

- : har

- :er

- 10

- 2023

- 23

- 77

- a

- oppnår

- tillegg

- justerbar

- tillater

- an

- og

- April

- AS

- At

- gjennomsnittlig

- tilbake

- BE

- vært

- Berkeley

- Bias

- både

- bygge

- by

- egenskaper

- kostnad

- sammenlignet

- databehandling

- konvensjonell

- dato

- forsinkelse

- utforming

- design

- detalj

- Enheter

- dynamisk

- e

- effekt

- familie

- FET

- færre

- Til

- Fundament

- foran

- fullt

- fullt

- finansiering

- videre

- Gates

- Tysk

- Halvparten

- Ha

- Høy

- HTTPS

- i

- IEEE

- Påvirkning

- forbedring

- in

- indisk

- industriell

- inngang

- Institute

- IT

- journal

- i likhet med

- laste

- logikk

- Lav

- mindre

- modell

- München

- Ny

- node

- of

- on

- or

- vår

- Papir

- ytelse

- plato

- Platon Data Intelligence

- PlatonData

- makt

- prosess

- Produkt

- foreslå

- foreslått

- foreslår

- publisert

- reduserer

- Krever

- forskning

- forskere

- henholdsvis

- Resultater

- s

- deling

- Vis

- Silicon

- simulering

- Stater

- levere

- Teknisk

- Teknologi

- Det

- De

- Disse

- denne

- terskel

- tittelen

- til

- universitet

- brukt

- ved hjelp av

- bruker

- Spenning

- var

- we

- hvilken

- med

- zephyrnet