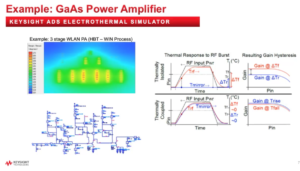

Den gamle setningen om at kuren er verre enn sykdommen er apropos når man diskuterer MBIST for store SOC-er der det å kjøre mange MBIST-tester parallelt kan overskride evnene til kraftdistribusjonsnettverk (PDN). Memory Built-In Self-Test (MBIST) kjører vanligvis automatisk under strøm på hendelser. På grunn av ønsket om å fremskynde test- og oppstartstidene for chip, kjøres disse testene ofte parallelt. Problemet er at de enkelt kan produsere bytteaktivitet som er en størrelsesorden over nivåene som finnes under vanlig brikkedrift. Faktisk kan disse høyere bytteaktivitetsnivåene ikke bare føre til at forsyningen reduseres som påvirker testresultatene, men også den høye varmen som genereres kan skade chips. Disse effektene kan føre til feil binning eller direkte og latente feil.

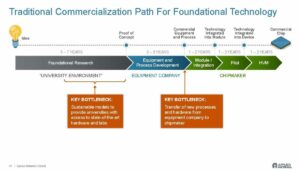

Løsningen er å simulere MBIST-aktivitet for å forutsi belastningen på PDN og de relaterte termiske effektene. Med simuleringsresultater i hånden kan designere riktig bestemme hvor mange og hvilke minneblokker som kan testes parallelt. Dette er imidlertid ikke alltid mulig i store SOC-er med mange minneblokker fordi simuleringstidene kan være uoverkommelige. Med gatenivå og enda mindre nøyaktig RTL-simulering er det kanskje ikke mulig å kjøre nok sykluser til å få den nødvendige informasjonen.

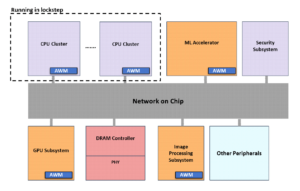

I en hvitbok med tittelen "Analyzing the power impplications of MBIST usage" ser Siemens EDA på hvordan designere kan kjøre tilstrekkelig simulering til å ta informerte beslutninger om teststrategien før tapeout. Siemens jobbet med ARM på en av testbrikkene deres for å lage en testcase der de kunne bruke maskinvareemulering med DFT- og Power-appene for Siemens maskinvareemulator Veloce. For det første brukes Veloce DFT-appen til å sende ut den interne aktiviteten under MBIST-emulering. Appen bruker Standard Test Interface Language (STIL) og produserer industristandard utdatafiler.

Veloce Power-appen henter aktivitetsinformasjonen fra MBIST-kjøringene for å generere bølgeformer, kraftprofiler og varmekart som kan indikere når det er krafttopper over spesifiserte grenser. Med denne informasjonen kan testingeniører ta informerte beslutninger om sekvenseringen av MBIST.

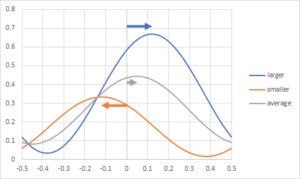

ARM-testsaken beskrevet i Siemens hvitbok inneholder 176 millioner porter. Siemens brukte et Veloce-system med 6 Veloce Strato-brett for denne testsaken. Veloce-emulatorkjøringen tok bare 26 timer, som er 15,600 XNUMX ganger raskere enn gatenivåsimulering. En annen fordel med Veloce-flyten er at aktivitetsinformasjonen strømmes av Power-appen til strømverktøyene i flyten, noe som sparer diskplass og tid. Resultatene fra testsaken viste flere krafttopper som brøt med SOC-designspesifikasjonene. Utgangen fra Veloce Power-appen viser de totale effektnivåene gjennom simuleringen sammen med de separate effektbidragene for klokken, kombinasjonslogikken og minnet. Likeledes er det informasjon om hvor på terningen strømmen brukes. Denne informasjonen gjør det enkelt å finne ut hvor det er problemer.

Å finne slike problemer krever å kjøre millioner eller milliarder av klokkesykluser. Begrensningene til programvaresimulatorer gjør det uoverkommelig å utføre den nødvendige analysen. Emulering tilbyr en unik mulighet for å nøye undersøke kraftpåvirkningene av MBIST og andre testoperasjoner lenge før silisium. Siemens hvitbok gir innsikt i kraftmetoden som brukes på en ekte testsak. Hvitboken er tilgjengelig for nedlasting for lesing på Siemens nettside.

Del dette innlegget via: Kilde: https://semiwiki.com/eda/306889-mbist-power-creates-lurking-danger-for-socs/

- Om oss

- analyse

- app

- apps

- ARM

- tilgjengelig

- være

- Årsak

- chip

- chips

- klokke

- inneholder

- kunne

- kur

- utforming

- sykdom

- under

- lett

- Ingeniører

- Event

- hendelser

- raskere

- Først

- flyten

- funnet

- Gates

- generere

- maskinvare

- Høy

- Hvordan

- HTTPS

- industri

- informasjon

- IT

- Språk

- stor

- føre

- Nivå

- nivåer

- laste

- Lang

- Kart

- millioner

- millioner

- nødvendig

- nettverk

- Tilbud

- Drift

- rekkefølge

- Annen

- Papir

- makt

- Problem

- Profiler

- Lesning

- Resultater

- Kjør

- rennende

- besparende

- Siemens

- simulering

- Software

- Rom

- fart

- Strategi

- streames

- levere

- system

- test

- Testing

- tester

- termisk

- Gjennom

- tid

- verktøy

- unik

- vanligvis

- Nettsted

- hvitt papir

- arbeidet