To nyere programvarebaserte algoritmiske teknologier – autonom kjøring (ADAS/AD) og generativ AI (GenAI) – holder halvledermiljøet oppe om natten.

Mens ADAS på nivå 2 og nivå 3 er i rute, er AD på nivå 4 og 5 langt fra virkeligheten, noe som forårsaker et fall i venturekapitalentusiasme og penger. I dag får GenAI oppmerksomheten, og VC-er investerer ivrig milliarder av dollar.

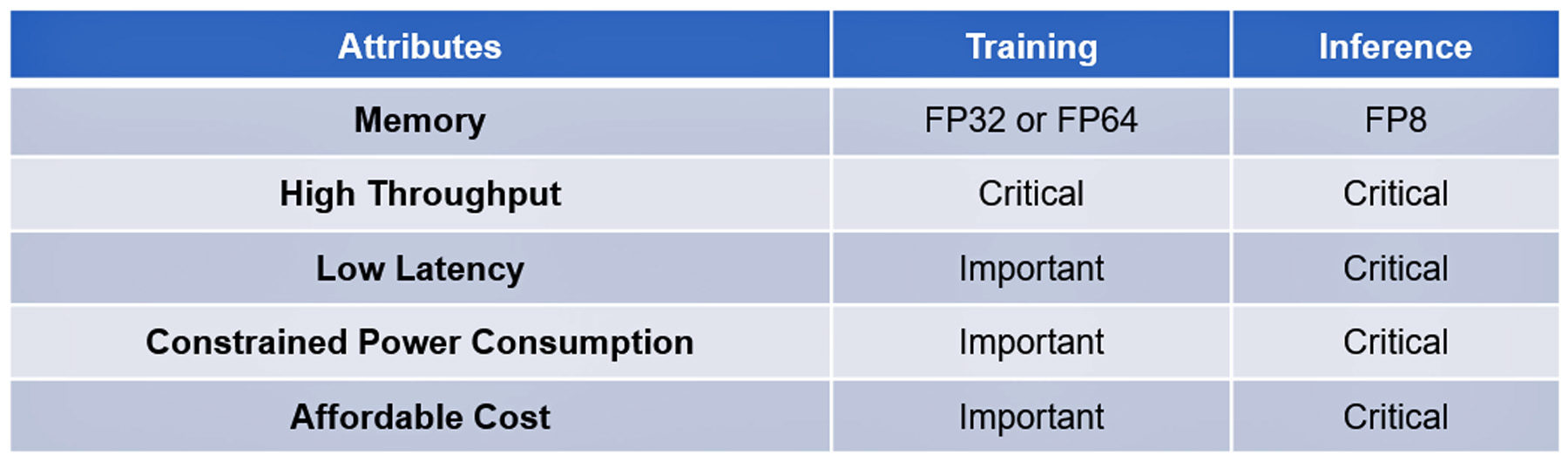

Begge teknologiene er basert på moderne, komplekse algoritmer. Behandlingen av opplæringen og slutningen deres deler noen få egenskaper, noen kritiske, andre viktige, men ikke avgjørende: Se tabell I.

Den bemerkelsesverdige programvarefremgangen i disse teknologiene har til nå ikke blitt gjenskapt av fremskritt innen algoritmisk maskinvare for å akselerere gjennomføringen av dem. For eksempel har ikke toppmoderne algoritmiske prosessorer ytelsen til å svare på ChatGPT-4-forespørsler på ett eller to sekunder til en pris på ¢2 per spørring, standarden etablert av Google-søk, eller til å behandle de enorme dataene samles inn av AD-sensorene på mindre enn 20 millisekunder.

Det er inntil det franske oppstartsselskapet VSORA investerte hjernekraft for å ta tak i minneflaskehalsen kjent som minneveggen.

Minneveggen

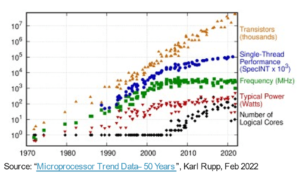

Minneveggen til CPU-en ble først beskrevet av Wulf og McKee i 1994. Helt siden har minnetilgang blitt flaskehalsen for dataytelse. Fremskritt i prosessorytelse har ikke blitt speilet i minnetilgangsfremgang, noe som får prosessorer til å vente lenger på data levert av minner. På slutten faller prosessoreffektiviteten langt under 100 % utnyttelse.

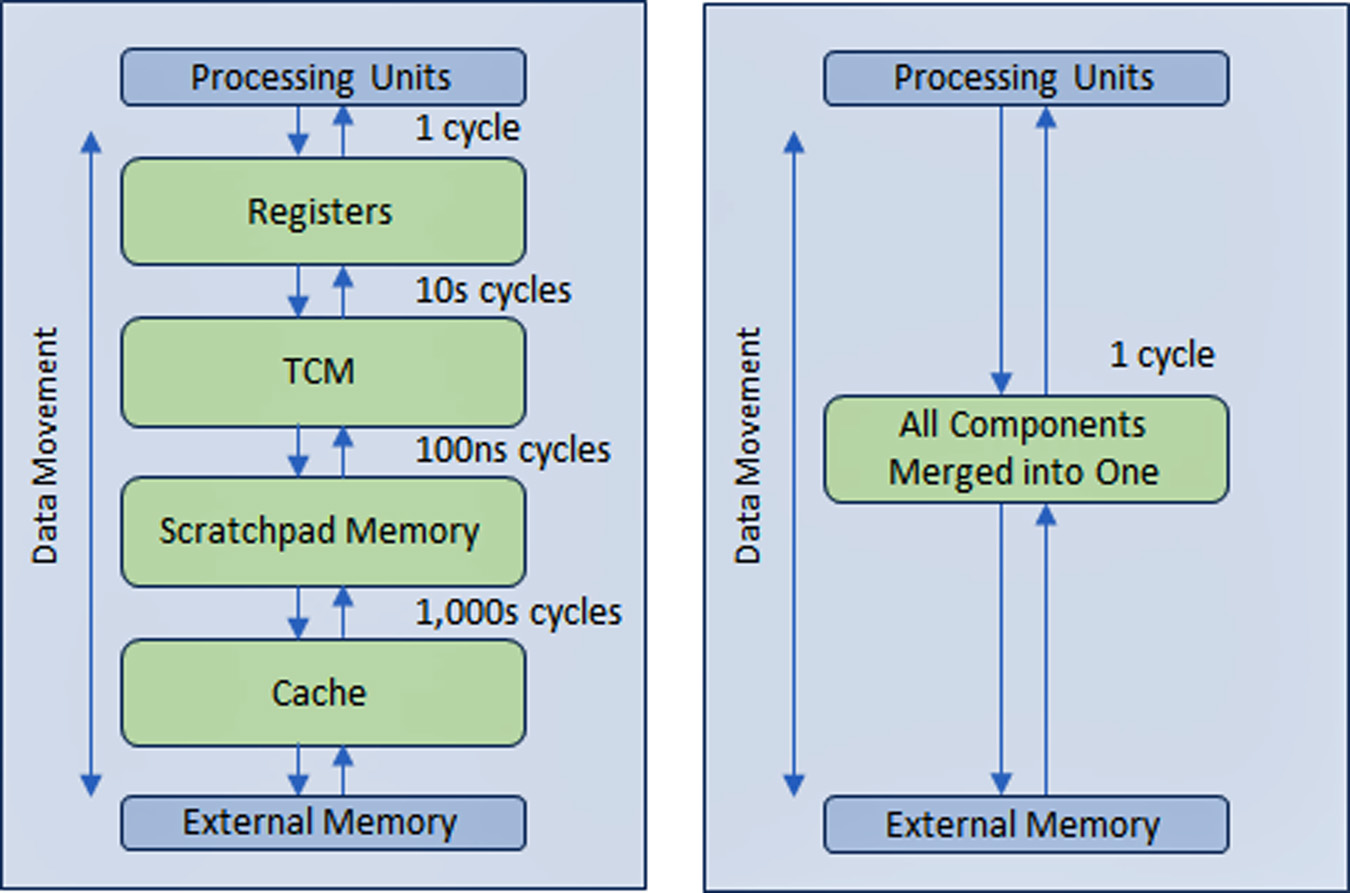

For å løse problemet skapte halvlederindustrien en hierarkisk minnestruktur på flere nivåer med flere nivåer av hurtigbuffer nærmere prosessoren som reduserer mengden trafikk med de tregere hoved- og eksterne minnene.

Ytelsen til AD- og GenAI-prosessorer avhenger mer enn andre typer dataenheter på bred minnebåndbredde.

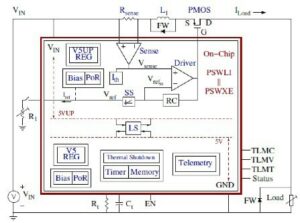

VSORA, grunnlagt i 2015 for å målrette mot 5G-applikasjoner, oppfant en patentert arkitektur som kollapser den hierarkiske minnestrukturen til en stor båndbredde, tett koblet minne (TCM) tilgjengelig i én klokkesyklus.

Fra prosessorkjernenes perspektiv ser og fungerer TCM som et hav av registre i mengden MByte versus kByte faktiske fysiske registre. Muligheten til å få tilgang til en hvilken som helst minnecelle i TMC i én syklus gir høy utførelseshastighet, lav latenstid og lavt strømforbruk. Det krever også mindre silisiumareal. Lasting av nye data fra eksternt minne til TCM mens gjeldende data behandles påvirker ikke systemets gjennomstrømning. I utgangspunktet tillater arkitekturen 80+% utnyttelse av prosesseringsenhetene gjennom designen. Likevel er det en mulighet for å legge til cache og skrapeloddminne hvis en systemdesigner ønsker det. Se figur 1.

Gjennom en registerlignende minnestruktur implementert i praktisk talt alle minner på tvers av alle applikasjoner, kan ikke fordelen med VSORA-minnetilnærmingen overvurderes. Vanligvis leverer banebrytende GenAI-prosessorer enkeltsifrede prosentvise effektivitet. For eksempel leverer en GenAI-prosessor med nominell gjennomstrømning på én Petaflops med nominell ytelse, men mindre enn 5 % effektivitet, en brukbar ytelse på mindre enn 50 Teraflops. I stedet oppnår VSORA-arkitekturen mer enn 10 ganger større effektivitet.

VSORAS algoritmiske akseleratorer

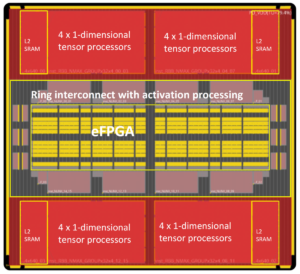

VSORA introduserte to klasser av algoritmiske akseleratorer – Tyr-familien for AD-applikasjoner og Jotunn-familien for GenAI-akselerasjon. Begge leverer fantastisk gjennomstrømning, minimal latens, lavt strømforbruk i et lite silisiumfotavtrykk.

Med nominell ytelse på opptil tre Petaflops, kan de skilte med en typisk implementeringseffektivitet på 50-80 % uavhengig av algoritmetype, og et maksimalt strømforbruk på 30 Watt/Petaflops. Dette er fantastiske egenskaper, ikke rapportert av noen konkurrerende AI-akselerator ennå.

Tyr og Jotunn er fullt programmerbare og integrerer AI- og DSP-funksjoner, om enn i forskjellige mengder, og støtter direktevalg av aritmetikk fra 8-biters til 64-biters enten heltalls- eller flyttallsbasert. Deres programmerbarhet rommer et univers av algoritmer, noe som gjør dem algoritmeagnostiske. Flere forskjellige typer sparsitet støttes også.

VSORA-prosessorenes egenskaper driver dem til forkant av det konkurrerende algoritmiske prosesseringslandskapet.

VSORA-støtteprogramvare

VSORA designet en unik kompilerings-/valideringsplattform skreddersydd for maskinvarearkitekturen for å sikre at dens komplekse, høyytelses SoC-enheter har rikelig med programvarestøtte.

En rekke hierarkiske verifikasjons-/valideringsnivåer – ESL, hybrid, RTL og gate – er ment å sette den algoritmiske designeren i cockpiten, og leverer trykkknapp-tilbakemeldinger til den algoritmiske ingeniøren som svar på designutforskning av rom. Dette hjelper ham eller henne å velge det beste kompromisset mellom ytelse, latens, kraft og område. Programmeringskode skrevet på et høyt abstraksjonsnivå kan kartlegges rettet mot forskjellige prosesseringskjerner transparent for brukeren.

Grensesnitt mellom kjerner kan implementeres innenfor samme silisium, mellom brikker på samme PCB eller gjennom en IP-forbindelse. Synkronisering mellom kjerner administreres automatisk på kompileringstidspunktet og krever ikke programvareoperasjoner i sanntid.

Veisperring til L4/L5 Autonom Driving og Generative AI Inference at the Edge

En vellykket løsning bør også inkludere programmerbarhet i felt. Algoritmer utvikler seg raskt, drevet av nye ideer som foreldes over natten av gårsdagens toppmoderne. Muligheten til å oppgradere en algoritme i feltet er en bemerkelsesverdig fordel.

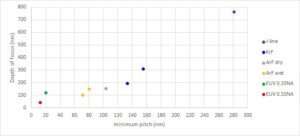

Mens hyperskalabedrifter har satt sammen enorme databehandlingsfarmer med mengder av prosessorer med høyeste ytelse for å håndtere avanserte programvarealgoritmer, er tilnærmingen bare praktisk for trening, ikke for slutninger på kanten.

Trening er vanligvis basert på 32-biters eller 64-biters flytende komma-aritmetikk som genererer store datavolumer. Den pålegger ikke streng ventetid og tolererer høyt strømforbruk i tillegg til betydelige kostnader.

Inferens ved kanten utføres vanligvis på 8-bits flytende komma-aritmetikk som genererer noe mindre mengder data, men krever kompromissløs ventetid, lavt energiforbruk og lave kostnader.

Effekten av energiforbruk på ventetid og effektivitet

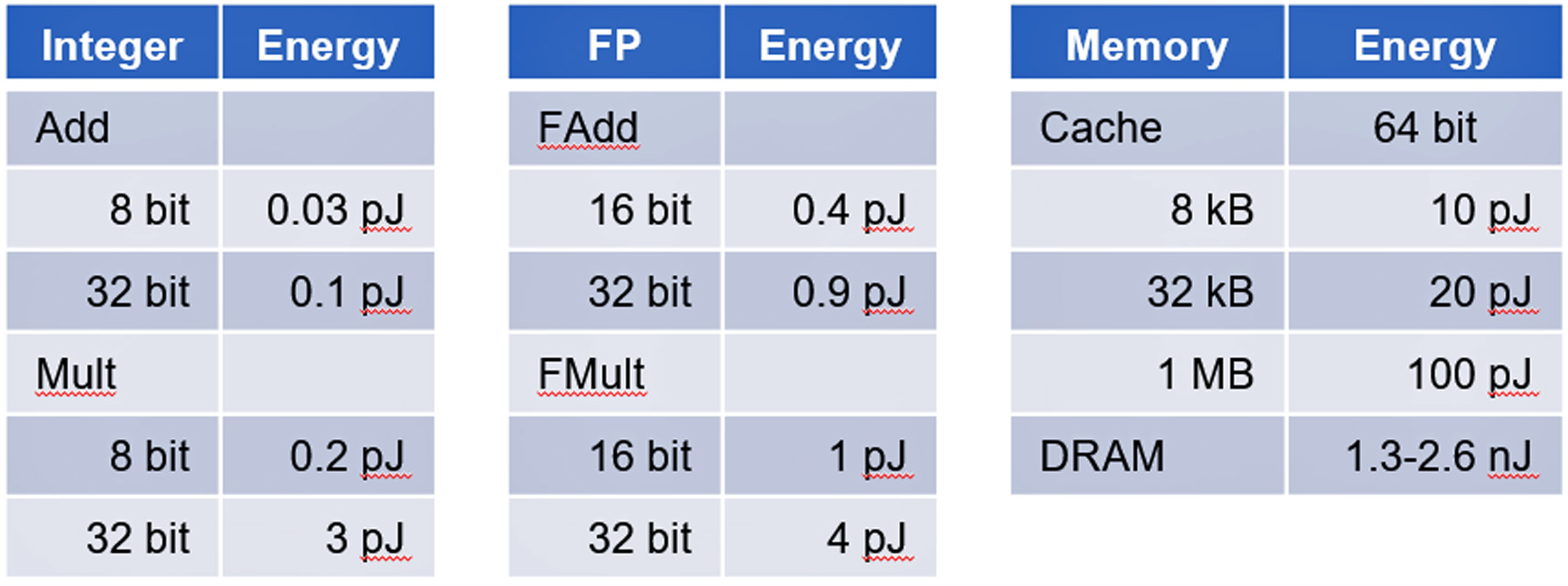

Strømforbruket i CMOS ICer domineres av databevegelse ikke databehandling.

En studie fra Stanford University ledet av professor Mark Horowitz viste at strømforbruket til minnetilgang bruker størrelsesorden mer energi enn grunnleggende digitale logiske beregninger. Se tabell II.

AD- og GenAI-akseleratorer er gode eksempler på enheter dominert av databevegelser som utgjør en utfordring for å begrense strømforbruket.

konklusjonen

AD- og GenAI-slutninger utgjør ikke-trivielle utfordringer for å oppnå vellykkede implementeringer. VSORA kan levere en omfattende maskinvareløsning og støtteprogramvare for å møte alle kritiske krav for å håndtere AD L4/L5 og GenAI som GPT-4-akselerasjon til kommersielt levedyktige kostnader.

Flere detaljer om VSORA og dens Tyr og Jotunn finner du på www.vsora.com.

Om Lauro Rizzatti

Lauro Rizzatti er bedriftsrådgiver for VSORA, en innovativ oppstart som tilbyr silisium IP-løsninger og silisiumbrikker, og en kjent verifikasjonskonsulent og bransjeekspert på maskinvareemulering. Tidligere har han hatt stillinger innen ledelse, produktmarkedsføring, teknisk markedsføring og engineering.

Les også:

Soitec er Engineering the Future of the Semiconductor Industry

ISO 21434 for Cybersecurity-Aware SoC-utvikling

Prediktivt vedlikehold i sammenheng med funksjonell sikkerhet for biler

Del dette innlegget via:

- SEO-drevet innhold og PR-distribusjon. Bli forsterket i dag.

- PlatoData.Network Vertical Generative Ai. Styrk deg selv. Tilgang her.

- PlatoAiStream. Web3 Intelligence. Kunnskap forsterket. Tilgang her.

- PlatoESG. Karbon, CleanTech, Energi, Miljø, Solenergi, Avfallshåndtering. Tilgang her.

- PlatoHelse. Bioteknologisk og klinisk etterretning. Tilgang her.

- kilde: https://semiwiki.com/automotive/336201-long-standing-roadblock-to-viable-l4-l5-autonomous-driving-and-generative-ai-inference-at-the-edge/

- : har

- :er

- :ikke

- $OPP

- 000

- 1

- 10

- 1800

- 1994

- 20

- 30

- 50

- 5G

- a

- evne

- Om oss

- abstraksjon

- akselerere

- akselerasjon

- akselerator

- akseleratorer

- adgang

- aksesseres

- Tilgang

- Oppnå

- oppnår

- tvers

- handlinger

- faktiske

- Ad

- ADA-er

- legge til

- adresse

- avansert

- fremskritt

- Fordel

- rådgiver

- påvirke

- AI

- algoritme

- algoritmisk

- algoritmer

- Alle

- tillater

- også

- beløp

- beløp

- an

- og

- besvare

- noen

- søknader

- tilnærming

- arkitektur

- ER

- AREA

- Kunst

- AS

- At

- oppmerksomhet

- attributter

- automatisk

- automotive

- autonom

- Båndbredde

- basert

- grunnleggende

- I utgangspunktet

- BE

- bli

- vært

- under

- benchmark

- BEST

- mellom

- milliarder

- både

- virksomhet

- men

- by

- cache

- CAN

- kan ikke

- evner

- hovedstad

- forårsaker

- celle

- utfordre

- utfordringer

- chips

- klasser

- klokke

- Cockpit

- kode

- kollapser

- kommersielt

- samfunnet

- Selskaper

- konkurranse

- komplekse

- komplisert

- omfattende

- kompromiss

- beregninger

- Beregn

- databehandling

- tilkobling

- konsulent

- forbruk

- inneholde

- kontekst

- Kostnad

- Kostnader

- kombinert

- prosessor

- opprettet

- kritisk

- Gjeldende

- skjærekant

- syklus

- dato

- databehandling

- leverer

- levert

- leverer

- tett

- avhenger

- beskrevet

- utforming

- designet

- designer

- detaljer

- Enheter

- forskjellig

- digitalt

- sifre

- do

- gjør

- dollar

- drevet

- kjøring

- Drop

- Drops

- ivrig

- Edge

- effektivitet

- enten

- slutt

- energi

- Energiforbruk

- ingeniør

- Ingeniørarbeid

- sikre

- entusiasme

- ESL

- avgjørende

- etablert

- NOEN GANG

- utvikle seg

- eksempel

- eksempler

- gjennomføring

- Expert

- utvendig

- familie

- langt

- Farms

- tilbakemelding

- Noen få

- felt

- Figur

- Først

- flytende

- Fotspor

- Til

- teten

- funnet

- Stiftet

- Fransk

- fra

- fullt

- funksjonelle

- framtid

- genererer

- generative

- Generativ AI

- Google Search

- større

- håndtere

- maskinvare

- Ha

- he

- Held

- hjelper

- her

- Høy

- høy ytelse

- høyest

- ham

- Horowitz

- http

- HTTPS

- stort

- Hybrid

- i

- ICS

- Ideer

- if

- ii

- gjennomføring

- implementeringer

- implementert

- viktig

- pålegge

- in

- inkludere

- industri

- Bransjeekspert

- innovative

- f.eks

- i stedet

- integrere

- inn

- introdusert

- Oppfunnet

- Investere

- investert

- IP

- IT

- DET ER

- jpg

- hopp

- holde

- kjent

- landskap

- stor

- Ventetid

- Led

- mindre

- Nivå

- nivåer

- i likhet med

- lasting

- logikk

- langvarige

- lenger

- UTSEENDE

- Lav

- Hoved

- vedlikehold

- Making

- fikk til

- ledelse

- mandater

- merke

- Marketing

- massive

- max bredde

- Møt

- Minner

- Minne

- millisekunder

- minimal

- Moderne

- penger

- mer

- bevegelse

- flere

- mengder

- Ny

- natt

- bemerket

- bemerkelsesverdig

- nå

- foreldet

- of

- tilby

- on

- ONE

- bare

- Drift

- or

- rekkefølge

- ordrer

- Annen

- andre

- enn

- over natten

- tydelig

- patentert

- Topp

- for

- prosent

- ytelse

- utført

- perspektiv

- fysisk

- plattform

- plato

- Platon Data Intelligence

- PlatonData

- Plenty

- Point

- stillinger

- mulighet

- Post

- makt

- Praktisk

- tidligere

- Prime

- Problem

- prosess

- behandlet

- prosessering

- prosessor

- prosessorer

- Produkt

- Professor

- programmerbar

- Programmering

- Progress

- Propell

- sette

- spørsmål

- område

- raskt

- Lese

- sanntids

- Reality

- nylig

- reduserer

- Uansett

- registre

- bemerkelsesverdig

- replikert

- rapportert

- krever

- Krav

- Krever

- svar

- samme

- SEA

- Søk

- sekunder

- se

- utvalg

- halvledere

- sensorer

- flere

- Del

- Aksjer

- bør

- viste

- Silicon

- siden

- enkelt

- liten

- So

- Software

- løsning

- Solutions

- LØSE

- noen

- noe

- kilde

- Rom

- fart

- brukt

- stanford

- Stanford University

- oppstart

- Tilstand

- state-of-the-art

- Stellar

- Still

- strømlinjeformet

- strengere

- struktur

- Studer

- betydelig

- vellykket

- støtte

- Støttes

- Støtte

- synkronisering

- system

- bord

- skreddersydd

- Target

- rettet mot

- Teknisk

- Technologies

- enn

- Det

- De

- Fremtiden

- deres

- Dem

- Der.

- Disse

- de

- denne

- tre

- Gjennom

- gjennomstrømning

- tett

- tid

- ganger

- til

- i dag

- spor

- tradisjonelle

- trafikk

- Kurs

- transparent

- to

- typen

- typer

- typisk

- typisk

- unik

- lomper

- Universe

- universitet

- til

- oppgradering

- bruk

- Bruker

- ved hjelp av

- ventureselskaper

- venture-

- venture kapital

- Verifisering

- Versus

- av

- levedyktig

- nesten

- volumer

- vente

- Wall

- var

- Vei..

- VI VIL

- når

- mens

- bred

- ønsker

- med

- innenfor

- skrevet

- ennå

- rentene

- zephyrnet