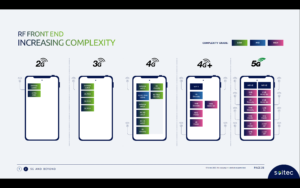

I marsjen til mer dyktige, raskere, mindre og lavere kraftsystemer ga Moores lov programvare en gratis tur i over 30 år eller så rent på utvikling av halvlederprosesser. Datamaskinvare leverte forbedrede ytelses-/areal-/kraftmålinger hvert år, slik at programvaren kan utvides i kompleksitet og levere mer kapasitet uten ulemper. Da ble de lette gevinstene mindre lette. Mer avanserte prosesser fortsatte å levere høyere portteller per arealenhet, men gevinster i ytelse og kraft begynte å flate ut. Siden våre forventninger til innovasjon ikke stoppet, har fremskritt i maskinvarearkitektur blitt viktigere for å ta opp slakk.

Drivere for å øke antall kjerne

Et tidlig skritt i denne retningen brukte flerkjerne-CPU-er for å akselerere total gjennomstrømning ved å tråde eller virtualisere en blanding av samtidige oppgaver på tvers av kjerner, og redusere kraften etter behov ved å gå på tomgang eller slå av inaktive kjerner. Multi-core er standard i dag, og en trend innen mange-kjerne (enda flere CPUer på en brikke) er allerede tydelig i serverforekomstalternativer tilgjengelig i skyplattformer fra AWS, Azure, Alibaba og andre.

Multi-/many-core arkitekturer er et skritt fremover, men parallellitet gjennom CPU-klynger er grovkornet og har sine egne ytelses- og kraftgrenser, takket være Amdahls lov. Arkitekturer ble mer heterogene, og la til akseleratorer for bilde, lyd og andre spesialiserte behov. AI-akseleratorer har også presset på finkornet parallellisme, og flyttet til systoliske arrays og andre domenespesifikke teknikker. Noe som fungerte ganske bra helt til ChatGPT dukket opp med 175 milliarder parametere med GPT-3 som utviklet seg til GPT-4 med 100 billioner parametere – størrelsesordener mer komplekse enn dagens AI-systemer – og tvinger fram enda mer spesialiserte akselerasjonsfunksjoner innenfor AI-akseleratorer.

På en annen front integreres nå multisensorsystemer i bilapplikasjoner i enkle SoC-er for forbedret miljøbevissthet og forbedret PPA. Her er nye nivåer av autonomi i bilindustrien avhengig av å smelte inn innganger fra flere sensortyper innenfor en enkelt enhet, i undersystemer som replikerer med 2X, 4X eller 8X.

I følge Michał Siwinski (CMO hos Arteris) antyder prøvetaking over en måned med diskusjoner med flere designteam på tvers av et bredt spekter av applikasjoner at disse teamene aktivt henvender seg til høyere kjernetall for å møte kapasitets-, ytelses- og kraftmål. Han forteller meg at de også ser denne trenden akselerere. Prosessfremskritt hjelper fortsatt med SoC-gatetellinger, men ansvaret for å oppfylle ytelses- og kraftmål er nå fast i hendene på arkitektene.

Flere kjerner, mer sammenkobling

Flere kjerner på en brikke innebærer flere dataforbindelser mellom disse kjernene. Innenfor en akselerator mellom nabobehandlingselementer, til lokal cache, til akseleratorer for sparsom matrise og annen spesialisert håndtering. Legg til hierarkisk tilkobling mellom akseleratorfliser og busser på systemnivå. Legg til tilkobling for vektlagring på brikken, dekompresjon, kringkasting, innsamling og re-komprimering. Legg til HBM-tilkobling for fungerende cache. Legg til en fusjonsmotor om nødvendig.

Den CPU-baserte kontrollklyngen må kobles til hvert av disse replikerte undersystemene og til alle de vanlige funksjonene – kodeker, minneadministrasjon, sikkerhetsøy og root of trust hvis det er hensiktsmessig, UCIe hvis en multi-chiplet-implementering, PCIe for høy båndbredde I/O , og Ethernet eller fiber for nettverk.

Det er mye sammenkobling, med direkte konsekvenser for produktets salgbarhet. I prosesser under 16nm bidrar NoC-infrastruktur nå med 10-12 % i areal. Enda viktigere, som kommunikasjonsmotorveien mellom kjerner, kan den ha betydelig innvirkning på ytelse og kraft. Det er reell fare for at en suboptimal implementering vil sløse bort forventet arkitekturytelse og kraftgevinster, eller enda verre, føre til at mange redesign-løkker for å konvergere. Men å finne en god implementering i en kompleks SoC-planløsning avhenger fortsatt av langsomme prøving-og-feil-optimaliseringer i allerede stramme designplaner. Vi må ta steget til fysisk bevisst NoC-design, for å garantere full ytelse og kraftstøtte fra komplekse NoC-hierarkier, og vi må gjøre disse optimaliseringene raskere.

Fysisk bevisste NoC-design holder Moores lov på rett spor

Moores lov er kanskje ikke død, men fremskritt i ytelse og kraft i dag kommer fra arkitektur og NoC-sammenkobling snarere enn fra prosess. Arkitektur presser flere akseleratorkjerner, flere akseleratorer innen akseleratorer og mer delsystemreplikering på brikken. Alle øker kompleksiteten til interconnect på brikken. Ettersom design øker kjernetellinger og går over til prosessgeometrier ved 16nm og lavere, kan de mange NoC-forbindelsene som spenner over SoC og dens undersystemer bare støtte det fulle potensialet til disse komplekse designene hvis de implementeres optimalt mot fysiske begrensninger og tidsbegrensninger – gjennom fysisk bevisst nettverk på brikkedesign.

Hvis du også bekymrer deg for disse trendene, vil du kanskje lære mer om Arteris FlexNoC 5 IP-teknologi HER.

Del dette innlegget via:

- SEO-drevet innhold og PR-distribusjon. Bli forsterket i dag.

- Platoblokkkjede. Web3 Metaverse Intelligence. Kunnskap forsterket. Tilgang her.

- kilde: https://semiwiki.com/artificial-intelligence/326727-interconnect-under-the-spotlight-as-core-counts-accelerate/

- :er

- $OPP

- 100

- a

- Om oss

- akselerere

- akselerer

- akselerasjon

- akselerator

- akseleratorer

- tvers

- aktivt

- avansert

- fremskritt

- mot

- AI

- AI-systemer

- Alibaba

- Alle

- tillate

- allerede

- og

- dukket opp

- søknader

- hensiktsmessig

- arkitektur

- ER

- AREA

- AS

- At

- lyd

- automotive

- tilgjengelig

- bevissthet

- AWS

- Azure

- Båndbredde

- BE

- bli

- under

- mellom

- Milliarder

- kringkaste

- Bussene

- by

- cache

- CAN

- stand

- ChatGPT

- chip

- Cloud

- Cluster

- CMO

- Kom

- Kommunikasjon

- komplekse

- kompleksitet

- Beregn

- samtidig

- Koble

- Tilkoblinger

- Tilkobling

- Konsekvenser

- begrensninger

- fortsatte

- kontroll

- konvergerer

- Kjerne

- prosessor

- FARE

- dato

- død

- leverer

- levert

- avhenger

- utforming

- design

- enhet

- forskjellig

- direkte

- retning

- diskusjoner

- ned

- ulempene

- hver enkelt

- Tidlig

- elementer

- Motor

- Miljø

- Selv

- Hver

- evolusjon

- utvikling

- Expand

- forventninger

- forventet

- raskere

- Egenskaper

- finne

- fast

- Til

- Forward

- Gratis

- fra

- foran

- fullt

- funksjoner

- fusjon

- inntjening

- Mål

- god

- garantere

- Håndtering

- hender

- maskinvare

- Ha

- hjelpe

- her.

- Høy

- høyere

- Hovedvei

- HTTPS

- bilde

- Påvirkning

- gjennomføring

- implementert

- viktig

- forbedret

- in

- inaktiv

- Øke

- økende

- Infrastruktur

- Innovasjon

- f.eks

- Integrering

- IP

- Øya

- IT

- DET ER

- hoppe

- Law

- LÆRE

- Nivå

- nivåer

- grenser

- lokal

- Lot

- gjøre

- ledelse

- Mars

- Matrix

- max bredde

- Møt

- møte

- Minne

- Metrics

- kunne

- Måned

- mer

- flytte

- flytting

- flere

- Trenger

- nødvendig

- behov

- nettverk

- nettverk

- Ny

- mange

- of

- on

- alternativer

- ordrer

- Annen

- andre

- egen

- parametere

- ytelse

- fysisk

- fysisk

- Plattformer

- plato

- Platon Data Intelligence

- PlatonData

- Post

- potensiell

- makt

- Slå

- pen

- prosess

- Prosesser

- prosessering

- Produkt

- rent

- presset

- Skyver

- område

- heller

- ekte

- redusere

- replikert

- replikering

- ansvar

- resultere

- Ride

- root

- Sikkerhet

- halvledere

- signifikant

- siden

- enkelt

- slakk

- langsom

- mindre

- So

- Software

- sparsom matrise

- spesialisert

- Spotlight

- Standard

- startet

- Trinn

- Still

- Stopp

- lagring

- foreslår

- støtte

- system

- Systemer

- oppgaver

- lag

- teknikker

- Teknologi

- forteller

- Det

- De

- Disse

- Gjennom

- gjennomstrømning

- timing

- til

- i dag

- dagens

- Totalt

- Trend

- Trender

- Trillion

- Stol

- Turning

- typer

- etter

- enhet

- av

- vekt

- VI VIL

- hvilken

- bred

- Bred rekkevidde

- vil

- Vinner

- med

- innenfor

- arbeid

- år

- år

- zephyrnet