Multi-die-systemer består av flere spesialiserte funksjonelle dies (eller chiplets) som er satt sammen i samme pakke for å lage det komplette systemet. Multi-die-systemer har nylig dukket opp som en løsning for å overvinne nedbremsingen av Moores lov ved å gi en vei til å skalere funksjonaliteten i den pakkede brikken på en måte som kan produseres med god avkastning.

I tillegg muliggjør multi-die-systemer produkt-SKU-fleksibilitet når det gjelder ytelsesskalering for å matche behovene til ulike markedssegmenter, optimalisering av prosessnoden per funksjon ved å blande og matche ulike prosessnoder i samme produkt, raskere tid til marked og lavere risiko.

For å muliggjøre høyere rutetetthet og støtte høyere båndbreddetrafikk mellom dyser, har pakketeknologi utviklet seg til å lage nye, avanserte pakker, basert på silisium-interposers (med TSV-er) eller silisiumbroer og, mer nylig, omfordelingslag (RDL) , fanouts og HD-substrater.

Et nøkkelaspekt for suksessen til multi-die-systemer er evnen til å sikre testbarhet av systemet i ulike faser av produksjon og montering, samt å sikre pålitelig drift i felten. Ved å bruke ekstra monteringstrinn og mer komplekse bumping- og pakketeknologier, krever multi-die-systemer test- og pålitelighetsprosedyrer som går utover det som var toppmoderne for monolitiske design.

De nakne diesene, og selve pakken, bør forhåndstestes for å sikre at alle defekte dies eller pakker blir oppdaget før de settes sammen i en pakke. Hvis en defekt dyse oppdages først etter montering, må hele multi-die-systemet kasseres med alvorlig innvirkning på kostnadene. Prosessen med å teste nakne dies kalles Known Good Die (KGD) testing.

Selve monteringsprosessen varierer med valgt emballasjeteknologi. For eksempel tillater ikke chip first-teknologier, hvor dies plasseres først og sammenkobling bygges oppå dem, ikke testing av "kjent-god-pakke", noe som potensielt kan resultere i å kassere gode dies hvis sammenkoblingen er defekt. På den annen side, i chip-last-teknologier, hvor sammenkoblingen er bygget separat og dyser er montert på toppen av den, muliggjør forhåndstesting av pakken før montering, noe som reduserer sannsynligheten for at gode dies blir kassert.

Testbarhetsløsningen for multi-die-system kan deles inn i flere aspekter:

- Test dekning av individuelle blokker i formen

- Testdekning av de enkelte dies (nakne dies)

- Test av det sammensatte systemet (med dør-til-die-dekning)

- Tilgang til teststoffet i nakne dyser

- Hierarkisk tilgang til teststoff etter montering

Denne artikkelen beskriver fordelene med en omfattende testbarhetsløsning som utnytter UCIe IP for å sikre multi-die-systempålitelighet.

DFT for UCIe-grensesnittet

En løsning med høy testdekning for UCIe-grensesnittet oppnås ved å implementere omfattende testbarhetsfunksjoner i UCIe IP for å rute ut defekte dies i testfasen av nakne dies. Noen av funksjonene inkluderer:

- Skann kjeder som dekker alle syntetiserte digitale kretser

- Dedikert blokkspesifikk BIST-funksjonalitet

- Loopback innebygd selvtest (BIST) funksjonalitet som dekker hele signalkjeden opp til IO-pinnen

- Programmerbare pseudorandom binære sekvenser (PRBS) og brukerdefinerte testmønstergeneratorer og brikker

- Feilinjeksjon for å eliminere falske pasninger

I tillegg kan funksjonalitet for å utvide dekningen til dyse-til-die-koblingen, etter pakkemontering, bidra til å oppnå et høyt nivå av testdekning, inkludert:

- Fjernside (die-to-die) BIST loopback-funksjonalitet

- Die-to-die link BIST

- 2D øyemarginering for å analysere marginaliteter

- Per lane test og reparasjonsfunksjonalitet

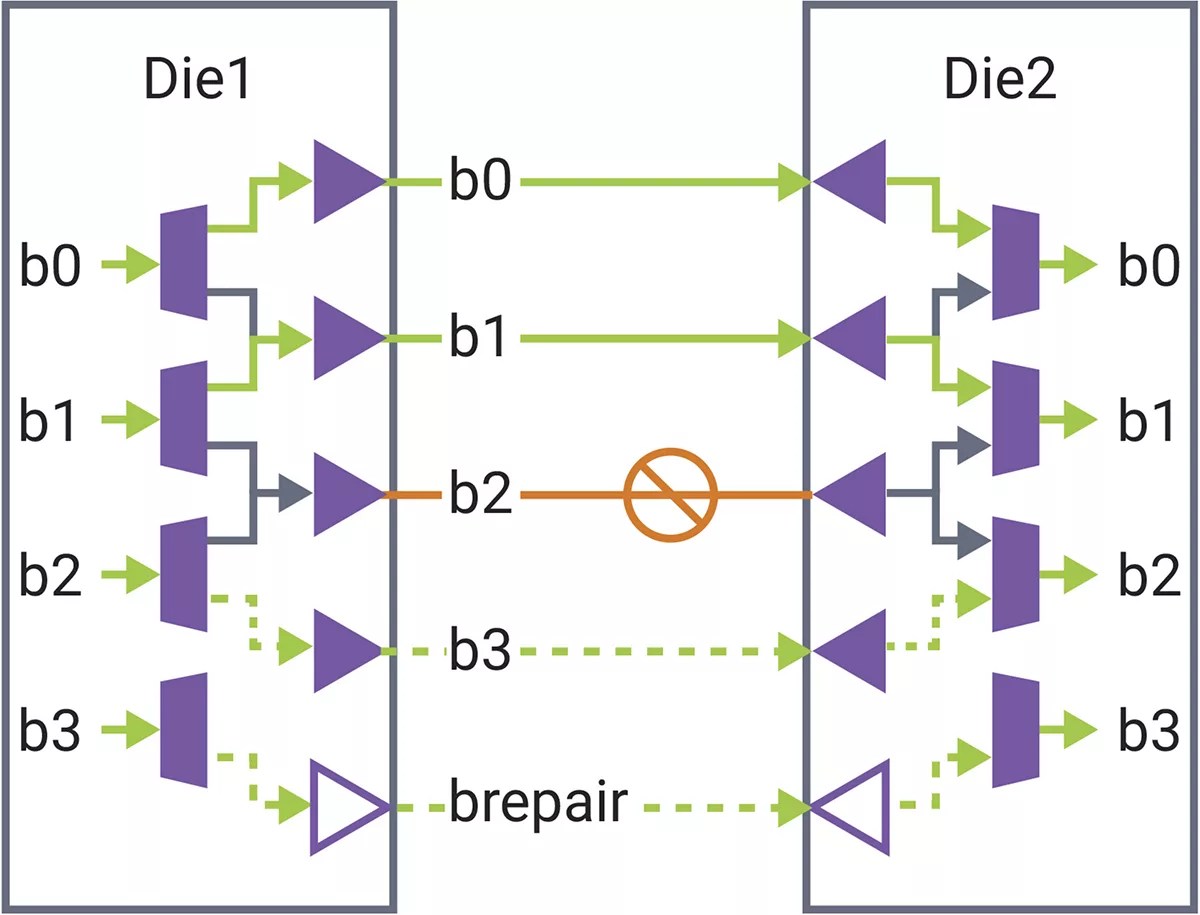

UCIe test og reparasjon

Avanserte pakker muliggjør ruting med høy tetthet med mikrobumping med fin pitch og ruting på silisium- eller RDL-interposers. Under monteringsprosessen kan det hende at noen mikrobump-forbindelser ikke er godt utformet og kan gå i stykker. UCIe tilbyr muligheten til å teste og reparere disse forbindelsene etter montering på en måte som gjenvinner det potensielle avkastningstapet.

UCIe-test og reparasjon utføres under produksjonstest og ved koblingsinitialisering. I testfasen kontrolleres hvert enkelt ledd for defekter ved lav hastighet. Defekte koblinger repareres ved å omdirigere data til reservekoblinger som er forhåndsdefinert av UCIe-standarden.

UCIe-konfigurasjoner rettet mot avanserte pakker inkluderer opptil 8 ekstra pinner per retning (TX og RX) for å muliggjøre reparasjon av alle funksjonelle koblinger:

- Fire reservepinner for reparasjon av datapinner, 2 pinner for hver gruppe med 32 datapinner

- En reservepinne for klokke og klokker og reparasjon av sporstift

- Tre reservepinner, hver for reparasjon av gyldig pin, sidebåndsdatapinne og klokkedatapinne

Test- og reparasjonsutførelsen skjer når det ikke er gyldig trafikk på die-to-die-koblingen. Etter at reparasjonen er fullført og koblingen er initialisert, antas den å være god og at trafikken kan passeres uten problemer. Den resulterende PHY-konfigurasjonen, kalt PHY-reparasjonssignaturen, lagres i interne registre i begge ender av koblingen.

Nedbrytning, på grunn av aldring eller annet, av mikrobump-karakteristikk under drift kan påvirke koblingsytelsen. Dette vil bli oppdaget på protokollnivå ved en økning i bit-feilfrekvens (BER) eller, i verste fall, ved at data går tapt. I så fall forventes koblingen å bli avbrutt og et nytt test- og reparasjonstrinn utført.

Noen applikasjoner har imidlertid strenge krav når det gjelder kontinuitet i trafikken på dør-til-dør-koblingen - de kan ikke tolerere avbrudd i trafikken under drift. For disse tilfellene legger en testbarhetsløsning til Signal Integrity Monitors (SIM) til hver UCIe-mottakerpinne.

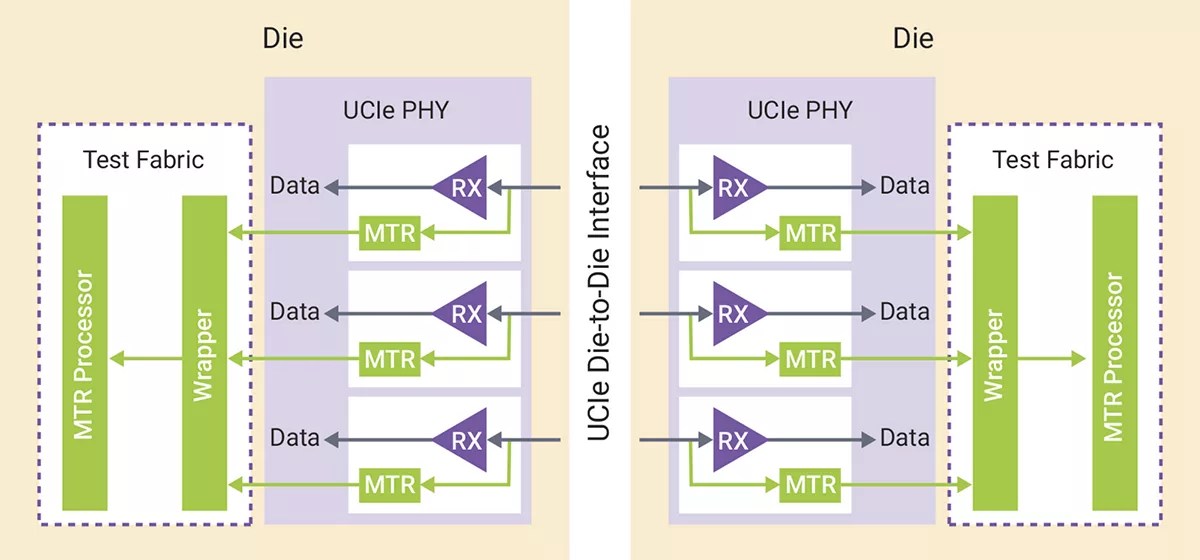

Fig. 1: Linkreparasjon med innebygde reservelenker.

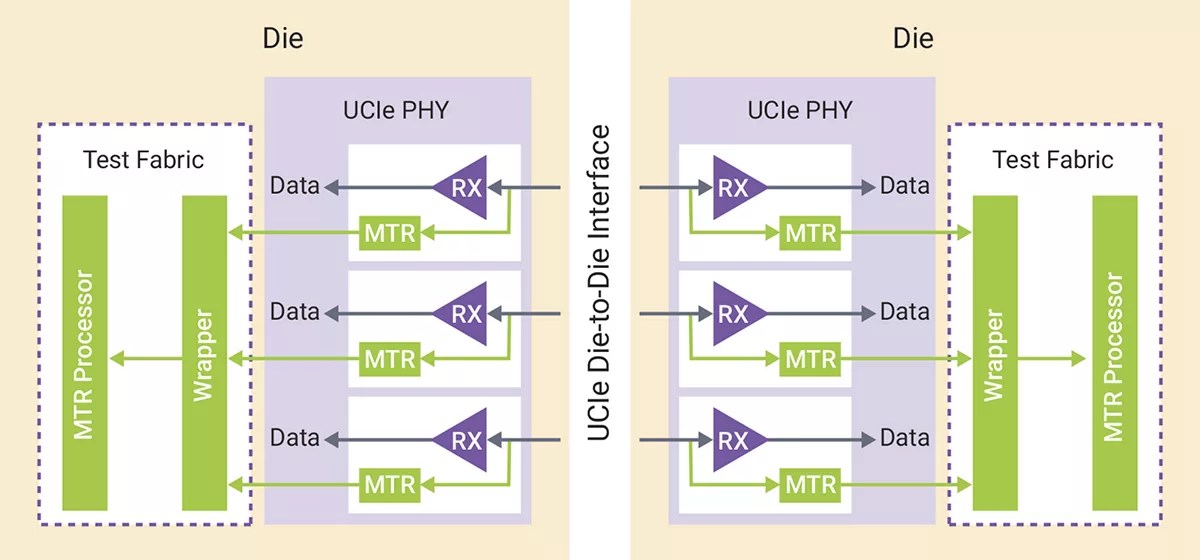

Signalintegritetsmonitorer

SIM-skjermer er små blokker innebygd i mottakeren. De registrerer konstant signalet på mottakerpinnen, under normal drift, for å identifisere variasjoner i signalkarakteristikkene som kan påvirke koblingsytelsen eller indikere at koblingen ikke lenger er sunn og kan bryte i nær fremtid.

Dataene som samles inn av de individuelle sensorene, samles inn i en Monitoring, Test and Repair (MTR) kontroller, utenfor grensesnittet, for videre behandling. Å aggregere dataene fra flere UCIe-koblinger kan gi umiddelbar innsikt i helsen til multi-die-systemet og muliggjøre prediktivt vedlikehold av koblinger.

Hvis en spesifikk kobling er spådd å være i fare for funksjonsfeil gjennom denne prosedyren, kan den deaktiveres og data omdirigeres til en av reservekoblingene, ved å utnytte UCIe PHY-reparasjonsmekanismen, selv uten trafikkavbrudd.

Fig. 2: Helseovervåkingsløsning for UCIe-koblinger.

Akselererer vekketiden

Mens trafikkmønsteret for de fleste brukstilfeller av dør-til-dø-grensesnitt, for eksempel ved serverdeling eller skalering, antas å være stabilt under drift, kan trafikk i noen brukstilfeller vise en eksplodert oppførsel. I slike tilfeller er det ønskelig å sette grensesnittet i en lavstrømsmodus for å spare strøm mens det ikke er trafikk. Reinitialisering av koblinger kan akselereres ved å unngå test- og reparasjonsprosessen og stole på UCIe PHY-reparasjonssignaturen som ble opprettet under forrige PHY-initialisering.

Dette konseptet kan utvides ytterligere til situasjoner der terningen er fullstendig slått av. I disse tilfellene blir PHY-reparasjonssignaturen hentet fra PHY og lagret på et permanent minne (eFuse eller flash). Minnet kan muligens lagre flere signaturer, som dekker forskjellige brukstilfeller eller forhold, noe som muliggjør ekstra brukerfleksibilitet.

Akselererer dysetesting med UCIe

Testtid er en kostbar vare. Det er mulig å akselerere testtiden ved å partisjonere teststrategien hierarkisk for å kjøre tester av forskjellige dies parallelt. Hierarkiet kan utvides over flere dies i et multi-die-system ved å koble testinfrastrukturen til de to dies hierarkisk. En slik tilnærming gir tilgang til alle dysene i multi-die-systemet fra et enkelt JTAG (eller lignende) testgrensesnitt i hovedmatrisen.

Ofte er begrensningen av testtiden tiden for å laste eller lese testvektorene inn i dysene. JTAG-grensesnitt kan bli en flaskehals for hastighet. For å overvinne denne begrensningen kan designere bruke eksisterende høyhastighetsgrensesnitt som PCI Express (PCIe) eller USB osv. som grensesnitt til testutstyret. Testvektorer og kommandoer pakkes for det grensesnittet og depakkes på dysen under produksjonstestfasen.

Mange dies har ikke et høyhastighetsgrensesnitt, men UCIe die-to-die-grensesnittet kan brukes under test for å transportere store testvektorer og kommandoer mellom dies med høy hastighet. UCI-die-to-die-grensesnittet utvider høyhastighets DFT-tilgangen over hele multi-die-systemet uten å øke antall pinner, noe som er spesielt viktig for IO og områdebegrensede dies.

Oppsummering

Foruten UCIe die-to-die-grensesnittet, er fellesnevneren som muliggjør alle disse test- og pålitelighetsforbedringsfunksjonene en test-, reparasjons- og overvåkingsstruktur som kan koble sammen alle interne blokker. Test-, reparasjons- og overvåkingsstoffet spenner over de forskjellige dysene i multi-die-systemet, og gir en strukturert hierarkisk infrastruktur som oppnår følgende viktige funksjoner:

- Styrer testingen av de enkelte diesene i multi-die-systemet

- Optimaliserer testplanlegging for å redusere testtiden

- Støtter høyhastighets testtilgang på tvers av dysene, via UCIe-grensesnittet

- Samler informasjon fra helseovervåkingsgrensesnittene innebygd i UCIe-grensesnittet og muliggjør videre behandling på systemnivå

- Administrerer lagringen av PHY-reparasjonssignaturen i et ikke-flyktig minne

- Og mer

Synopsys tilbyr en omfattende og skalerbar multi-die systemløsning, inkludert EDA og IP, for rask heterogen integrasjon. For en sikker og pålitelig die-to-die-tilkobling tilbyr Synopsys en komplett UCIe Controller, PHY og Verification IP-løsning. Som en del av Synopsys SLM & Test Family er en komplett UCIe Monitoring, Test and Repair (MTR) løsning tilgjengelig sammen med STAR Hierarchical System (SHS) løsning. MTR-løsningen inkluderer signalintegritetsmonitor for måling av signalkvalitet på UCIe-banene, BIST for selvtest og reparasjonslogikk for redundant kjørefeltallokering, mens SHS-løsningen fungerer som tilkoblingsstoffet som støtter industristandarden IEEE 1687, IEEE 1149.1 og IEEE 1838 grensesnitt. Denne komplette løsningen muliggjør effektiv og kostnadseffektiv helseovervåking av UCIe i alle faser av silisiumlivssyklusen, noe som er avgjørende for pålitelig drift av multi-die-systemer.

Ressurser:

- SEO-drevet innhold og PR-distribusjon. Bli forsterket i dag.

- PlatoAiStream. Web3 Data Intelligence. Kunnskap forsterket. Tilgang her.

- Minting the Future med Adryenn Ashley. Tilgang her.

- Kjøp og selg aksjer i PRE-IPO-selskaper med PREIPO®. Tilgang her.

- kilde: https://semiengineering.com/from-known-good-die-to-known-good-system-with-ucie-ip/

- : har

- :er

- :ikke

- :hvor

- $OPP

- 1

- 8

- a

- evne

- akselerere

- akselerert

- adgang

- Oppnå

- oppnådd

- oppnår

- tvers

- tillegg

- Ytterligere

- Legger

- avansert

- Etter

- Aldring

- Alle

- allokering

- tillate

- tillater

- langs

- an

- analysere

- og

- søknader

- tilnærming

- ER

- Artikkel

- AS

- aspektet

- aspekter

- montert

- Montering

- antatt

- At

- tilgjengelig

- unngå

- Båndbredde

- basert

- BE

- bli

- før du

- være

- Fordeler

- mellom

- Beyond

- Blokker

- Blocks

- både

- Break

- broer

- bringe

- bygget

- innebygd

- by

- som heter

- CAN

- kan ikke

- saken

- saker

- kjede

- kjeder

- egenskaper

- sjekket

- chip

- klokke

- Klokker

- handelsvare

- Felles

- fullføre

- helt

- komplekse

- omfattende

- konsept

- forhold

- Konfigurasjon

- Koble

- Tilkobling

- Tilkoblinger

- Tilkobling

- stadig

- controller

- Kostnad

- kostnadseffektiv

- kunne

- dekning

- dekker

- skape

- opprettet

- kritisk

- dato

- definert

- tetthet

- designere

- design

- oppdaget

- Die

- forskjellig

- digitalt

- retning

- deaktivert

- Divided

- do

- ned

- to

- under

- hver enkelt

- effektiv

- eliminere

- innebygd

- dukket

- muliggjøre

- muliggjør

- muliggjør

- slutter

- ekstrautstyr

- sikre

- sikrer

- utstyr

- etc

- Eter (ETH)

- Selv

- utviklet seg

- eksempel

- gjennomføring

- viser

- eksisterende

- forventet

- dyrt

- ekspress

- utvide

- omfattende

- ekstra

- øye

- stoff

- falsk

- familie

- FAST

- raskere

- defekt

- Egenskaper

- felt

- slutt

- Først

- Blitz

- fleksibilitet

- etter

- Til

- dannet

- fra

- funksjon

- funksjonelle

- funksjonalitet

- funksjoner

- videre

- framtid

- samlet

- generatorer

- Go

- god

- Gruppe

- hånd

- Ha

- Helse

- sunt

- hjelpe

- hierarki

- Høy

- høyere

- Men

- HTTPS

- identifisere

- IEEE

- if

- Påvirkning

- implementere

- viktig

- in

- inkludere

- inkluderer

- Inkludert

- Øke

- økende

- indikerer

- individuelt

- industri

- informasjon

- Infrastruktur

- innsikt

- instant

- integrering

- integritet

- Interface

- grensesnitt

- intern

- avbrutt

- inn

- IP

- IT

- selv

- nøkkel

- kjent

- Lane

- stor

- Law

- lag

- Nivå

- utnytter

- utnytte

- Livssyklus

- begrensning

- LINK

- lenker

- laste

- logikk

- lenger

- tap

- tapte

- Lav

- laget

- Hoved

- vedlikehold

- marked

- Match

- matchende

- max bredde

- Kan..

- måling

- mekanisme

- Minne

- Mote

- Overvåke

- overvåking

- skjermer

- Monolithic

- mer

- mest

- MTR

- flere

- må

- Nær

- behov

- Ny

- Nei.

- node

- noder

- normal

- Antall

- of

- Tilbud

- on

- ONE

- bare

- drift

- optimalisering

- or

- Annen

- ut

- utenfor

- Overcome

- pakke

- pakket

- pakker

- emballasje

- Parallel

- del

- spesielt

- bestått

- banen

- Mønster

- mønstre

- ytelse

- permanent

- fase

- pins

- Tonehøyde

- plato

- Platon Data Intelligence

- PlatonData

- mulig

- muligens

- potensiell

- potensielt

- makt

- powered

- spådd

- forrige

- Før

- sannsynlighet

- problemer

- prosedyrer

- prosess

- prosessering

- Produkt

- Produksjon

- protokollen

- gi

- gir

- gi

- kvalitet

- Sats

- Lese

- nylig

- Gjen

- redusere

- redusere

- registre

- pålitelighet

- pålitelig

- reparasjon

- krever

- Krav

- resulterende

- Risiko

- ruting

- Kjør

- RX

- samme

- Spar

- skalerbar

- skalering

- planlegging

- sikre

- segmenter

- valgt

- sensorer

- Sequence

- alvorlig

- serverer

- flere

- bør

- side

- Signal

- signaturer

- Silicon

- JA

- lignende

- enkelt

- situasjoner

- langsom

- bremse

- liten

- løsning

- noen

- spenn

- spesialisert

- spesifikk

- fart

- stabil

- Standard

- Stjerne

- state-of-the-art

- Trinn

- Steps

- lagring

- oppbevare

- lagret

- Strategi

- strukturert

- suksess

- slik

- støtte

- Støtte

- system

- Systemer

- rettet mot

- Technologies

- Teknologi

- vilkår

- test

- Testing

- tester

- Det

- De

- Dem

- deretter

- Der.

- Disse

- de

- denne

- Gjennom

- tid

- til

- topp

- spor

- trafikk

- transporter

- to

- TX

- usb

- bruke

- brukt

- Bruker

- ved hjelp av

- ulike

- Verifisering

- av

- var

- Vei..

- webp

- VI VIL

- Hva

- når

- hvilken

- mens

- vil

- med

- innenfor

- uten

- verste

- Utbytte

- zephyrnet