Plasma-etsing er kanskje den mest essensielle prosessen i halvlederproduksjon, og muligens den mest komplekse av alle fabrikkoperasjoner ved siden av fotolitografi. Nesten halvparten av alle fantastiske trinn er avhengige av et plasma, en energisk ionisert gass, for å gjøre jobben sin.

Til tross for stadig krympende transistor- og minneceller, fortsetter ingeniører å levere pålitelige etseprosesser.

"For bærekraftig å lage brikker med presisjon på nanoskalanivå og riktig kostnadsstruktur, må produsenter av waferfab-utstyr flytte grensene for plasmafysikk, materialteknikk og datavitenskap for å levere utstyrsløsningene som trengs," sa Thomas Bondur, konserndirektør for Etch produktgruppemarkedsføring på Lam Research. Ingen steder er dette mer tydelig enn i plasmaetsing, som fungerer hånd-i-hånd med litografi for å skape nøyaktige, repeterbare funksjoner på wafere.

Denne rapporten undersøker viktige etsingstrinn i 3D NAND, DRAM, nanosheet FET-er og sammenkoblinger, med et blikk fremover på 2D-enheter og lavbudsjetts backend-behandling. Industrien forfølger også mer bærekraftig etsekjemi for å redusere tilsvarende CO2 utslipp fra fabrikkene.

For mange verktøymakere spiller prosessmodellering en sentral rolle i utviklingen av etseprosesser. Målet er å forkorte tiden til markedet og samtidig redusere wafer- og maskekostnadene.

"Optimalisering av etse prosesser på noen av de vanskeligste trinnene kan ta et år eller mer å fullføre," sa Barrett Finch, senior markedsdirektør i Lam Research. "Vi har nylig fullført noe prosesssimuleringsarbeid på tre uker som var forventet å ta tre måneder ved bruk av typisk silisiumbasert testing og utvikling."

Dette kan beløpe seg til hundretusener, eller til og med millioner av dollar, bare for maske- og waferkostnadene for en enhetsprodusent.

Grunnleggende om etsing

Etseprosessen fungerer hånd i hånd med litografi. Etsing innledes vanligvis med avsetning av en film (ved epitaksi, kjemisk eller fysisk dampavsetning, etc.). Vanligvis, a CVD film er belagt med fotoresist og deretter eksponert gjennom en mønstret trådkors (maske) ved hjelp av optisk litografi (248nm eller 193nm UV, 13.5nm EUV). Motstå utvikling avslører da mønsteret. I et plasmaetsekammer med enkelt wafer bombarderer og fjerner typisk etsekjemikaliene og ionene CVD-filmen der fotoresisten mangler (i positiv tonemotstand). Etter etsing, motstå asking, våt kjemisk rengjøring og/eller våt etsing fjern rester.

Plasmaetsingsprosesser kan grovt grupperes som dielektriske, silisium- eller lederetser. Dielektriske stoffer som silisiumdioksid og silisiumnitrid etses best ved bruk av fluorholdige gasser mens silisium- og metalllag reagerer best med klorkjemi. Det er i hovedsak tre tørre etsningsmoduser - reaktiv ionesning, plasmaetsing og sputteretsing (ionestråle). Etseprosesser handler om de komplekse interaksjonene mellom de kjemiske reaktantene, plasma og wafermaterialer. Når RF-bias påføres en reaktiv gass, bombarderer elektroner og positivt ladede ioner waferen for å fysisk fjerne (etse) materiale mens de kjemiske artene og frie radikalene reagerer med det eksponerte materialet for å danne flyktige biprodukter. Etsing kan enten være isotropisk (reagerer like vertikalt og horisontalt), anisotropisk (bare vertikalt) eller et sted i mellom.

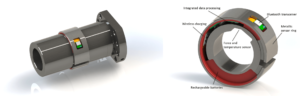

Fig. 1: Overgang fra finFET til GAA driver kritiske isotropiske selektive etsekrav. Kilde: Lam Research

Beregningene etseingeniører bryr seg mest om er etsehastighet, profilkontroll, ensartethet (på tvers av skiven) og etseselektivitet, fordi disse påvirker utbytte og produktivitet. Etseselektivitet er ganske enkelt forholdet mellom fjerning av materialet du ønsker å etse i forhold til underlaget – for eksempel SiO2 på silisium. Under etsing er det også fordelaktig å ikke fjerne for mye fotoresist. Men når det er tilfelle, overføres ofte mønsteret til en hard maske (silisiumdioksid, silisiumnitrid, SiOC, TiN) før det overføres til den underliggende filmen.

Selektivitetsspesifikasjonene varierer fra 2:1 til opptil 1,000:1 (svært selektiv etsning). For hver ny node blir disse spesifikasjonene strammere. "Med høy-NA EUV begynner å erstatte vanlig EUV i løpet av de neste fire årene, er fokuset mye lavere, så du kan ikke lenger eksponere tykk fotoresist - og med tykk mener jeg 30 nanometer," sa Philippe Bézard, tørr etch R&D-ingeniør ved imec. "Men du må fortsatt mønstre den samme filmtykkelsen nedenfor. Så nå ber du om mye høyere selektivitet i den forstand at i stedet for 2:1 må vi nå mer som 10:1, som er en plutselig 4X til 5X selektivitetsforbedring."

Fra proof of concept (POC) til høyvolumproduksjon (HVM)

Bézard beskriver tre faser av utvikling av etseprosesser:

- Bestemme hvilken etser, gasser, hjelpelag osv. som er nødvendig for å utføre etsingen;

- Demonstrere ytelse ved fullstendig fjerning av film innenfor spesifikasjoner med prosessuniformitet over en wafer, og

- Bestemme hvordan prosessen kan gjentas på tvers av tusenvis av wafere i HVM med høyt utbytte og lite drift.

Vanligvis håndterer dyktige etse- og integrasjonsingeniører de to første fasene av utviklingen. Den tredje fasen kan igjen bruke ingeniørkompetanse, men maskinlæring kan hjelpe.

"Maskinlæring og dataanalyse generelt er bare nyttig i den tredje fasen," sa han. "Den er veldig kraftig fordi den har tilgang til massevis av data og kan gi mening om en million små, enkle ting som alle samhandler. Så for en menneskelig hjerne å prøve å finne ut av dette er veldig vanskelig, men det er mer håndterbart for et dataprogram. Men i tilfeller der du har en ny applikasjon, nytt materiale som blir etset eller en ny integrasjon, viser det ingen forbedring i forhold til mennesker.»

ML-bruk gjelder også produksjonskostnader fordi tusenvis av wafere brukes i fase tre - minst en størrelsesorden større enn det som brukes i fase én og to.

Barrett Finch, seniordirektør for Etch Product Group ved Lam Research, beskriver ny prosessbanefinning som å ta et proof-of-concept fra en nominell prosessflyt og layout og utvikle en eller flere arbeidsenheter på en wafer. Denne POC blir deretter overført til et produktutviklingsteam i fabrikken for å skalere opp prosessen og forbedre utbyttet.

"Mengden arbeid som kreves for å forvandle et nominelt proof-of-concept til et levedyktig produkt, er ofte undervurdert, og dette skaper et stort gap til lønnsomhet," sa Finch. "Prosessvindusmodellering søker å lukke dette gapet ved å introdusere fantastisk variasjon i de tidlige stadiene av FoU-stifinning." Han foreslår at virtuelle DOE-er og Monte Carlo-basert analyse på tvers av en rekke prosessparametere tester en POC ved å simulere forventet variasjon.

"Prosessvindusmodellering kan svare på spørsmålet 'Hvilken CD eller nivå av variasjon må jeg opprettholde for å oppnå minimum ytelse og ytelse for enheten?' Vi har fullført virtuelle prosessvindutester med over 1 million virtuelle wafere på noen få dager, noe som ville være umulig å oppnå i det virkelige liv, sa han.

Flere parametere påvirker etsehastighet, profil og selektivitet. En nøkkel er temperatur. "Effekten av termiske effekter i etseprosessering blir sett av våre kunder når de kontrollerer etsehastigheter, selektiviteter og etsede profiler. Alle disse parameterne kan påvirke både enhetsutbytte og utmerket produktivitet, sier Benjamin Vincent, seniorleder for halvlederprosess og integrasjonsteknikk ved Lam Research. Han hevder at simulering kan være spesielt nyttig når et prosesstrinn har flere mulige konfigurasjoner (prosessplassen er stor), eller der nedstrømsresultatene fra trinnet er svært uforutsigbare.

"Etseprosessen er avhengig av overflatetemperaturen til waferen, som avhenger av flere varmeflukser - inkludert termisk ledning, ionpåvirkningsenergier, overflatereaksjoner og plasmastrålingsvarmeflukser," sa Alex Guermouche, produktmarkedssjef i Esgee Technologies, en Lam Research Company. "Som et resultat må plasmamodeller inkorporere alle disse fysikkfunksjonene for å nøyaktig avbilde temperaturendringer på waferens overflate. Prosesssimuleringsprogramvare kan modellere en rekke etseattributter, noe som lar oss få et bedre etseresultat raskere og akselerere kundens evne til å øke produksjonen eller optimalisere utbyttet.»

Nøyaktig tidspunkt for etseprosessen

Med strammere geometrier og tynnere filmer er det behov for å balansere etsehastigheten med stor kontroll over andre driftsparametre.

"Med krympende designregler beveger mange etseprosesser seg til svært raske plasmaetseprosesstrinn som krever svært presis kontroll av alle reaksjonsinnganger: kraft, trykk, kjemi og temperatur," sa Finch, og la merke til at det også er en trend mot optimalisert plasma pulserende oppførsel for å generere et bestemt ione-til-nøytralt forhold, og deretter feie bort biprodukter. "Avansert modellering av slike forhold vil være avgjørende for å muliggjøre ytterligere enhetsskalering."

Produsenter av etsesystemer har brukt modelleringsprogramvare i noen tid for å fremskynde utviklingen av neste node eller rampeutbytte. Dette er ingen overraskelse, gitt den store kompleksiteten til prosessen og alle dens variabler.

"Det er rett og slett ikke nok tid eller nok wafere til å utføre alle mulige prosesseksperimenter når man utvikler neste-node-teknologier," sa Finch. "Antall kombinasjoner av etseutstyrsinnstilling kan løpe inn i millioner, eller til og med milliarder, og utvikling av brute force wafer ved å bruke alle prosessmuligheter er rett og slett umulig."

Selvfølgelig er alle gode modeller verifisert på faktiske sjetonger. "En nøyaktig modell bør være prediktiv, og den bør løse det målrettede problemet som en bruker ønsker å løse," sa Finch. "Hver gang en prosess eller designendring har blitt anbefalt basert på simuleringsarbeid, bør faktiske fabrikkdata gjenspeile resultatene av anbefalingen. I vårt tilfelle har vi vært i stand til nøyaktig å forutsi effekten av prosessendringer ved å bruke modellbaserte resultater, og raskt løse vanskelige prosess- og teknologiutviklingsproblemer.»

Verktøyleverandører jobber også med avanserte etseprosesser for å integrere linjer tettere og transformere det som en gang var en prosess på to maskenivåer (to litografitrinn) til ett for prosessforenkling og kostnadsreduksjon.

"I stedet for å tilpasse eksisterende maskinvare for å gjøre den sveitsiske kniven enda mer utstyrt, introduserer selskaper teknologier som er applikasjonsspesifikke, for eksempel nye systemer for å løse tip-to-tip-problemer," sa Bézard. Målet er å gjøre to linjer som vender mot hverandre nærmere hverandre, som for tiden innebærer et linjemønstertrinn etterfulgt av en kuttet maske. "Det Applied Materials og andre introduserer er en måte å direkte etse i horisontal retning." Slike prosesser kan også utvides via hull.

Etsningstrinn for nanoark FET-er

Den mest kritiske etsingen trer inn nanoark prosessstrømmer inkluderer dummy gate etsing, anisotrop pilar etsing, isotrop spacer etsing og kanalfrigjøringstrinnet. [1] Profilen etser gjennom vekslende lag av silisium og SiGe er anisotropisk og bruker fluorert kjemi. Den indre avstandsetsingen (innrykk) og kanalfrigjøringstrinnet er optimalisert for å fjerne SiGe med ekstremt lavt silisiumtap.

Kanalutgivelsestrinnet er kritisk. "Utgivelsen av nanoarket krever ekstremt høy selektivitet," sa Bézard. "De fleste nanoark er silisium, deretter silisium-germanium og silisium. Du har vekslende lag, og du må fjerne det ene uten å endre det andre i det hele tatt." Noen publikasjoner har diskutert å utføre en flertrinns SiGe-etsing for å redusere stress på strukturen indusert av et enkelt etsetrinn.

Neste i prosessen er dannelsen av selvjusterte kontakter. "Her er det vi prøver å gjøre i utgangspunktet å etse silisiumdioksid og ikke berøre eller senke silisiumnitridet. Nåværende spesifikasjoner er, la oss si, 3 nm fordypning, men folk ber om null tap," sa Bézard. "I dette tilfellet bruker vi ikke engang ordet selektivitet. Vi snakker bare om friminutt – og null fordypning på det.»

3D NAND

Til 3D NAND flash, fortsetter antallet lag å vokse og nødvendiggjør bruk av flere stablede nivåer i fremtiden, og til slutt skaper vertikale strenger av stablede enheter. "Det er også mye drivkraft for å skalere ordlinjestigningen eller vertikal/Z-pitch for lagene etter hvert som antall lag vokser for å fortsette å øke bittettheten," sa Robert Clark, seniormedlem i teknisk stab og teknologidirektør hos TEL. "Fra et prosessperspektiv vil etse- og deponeringsprosesser trenge konstante forbedringer for å imøtekomme de stadig høyere sideforhold og stadig mindre kritiske dimensjoner som fortsatt skalering krever."

Clark beskrev fremtidige endringer. "Når vi ser mot avanserte noder av ladefelleenheter med flere nivåer, vil konstruksjon av portstablene være nødvendig for å oppnå kortere portlengder, flere nivåer per celle og forbedret programmeringseffektivitet - potensielt gjennom bruk av høyk-materialer. Høyere konduktivitetskanaler vil sannsynligvis også være nødvendig for å erstatte poly-Si-kanaler i fremtiden,» sa han.

En av de mest kritiske etsningene i 3D NAND involverer dyp etsing av omtrent 100 nm hull gjennom flerlags oksid-nitrid-stabler (200+ lag), som kan være opptil 10 µm dype. Imecs Bézard sa at dette etsetrinnet er spesielt dyrt.

"Vi har et fysisk fenomen som oppstår, kalt differensiell ladeeffekt," sa han. "I plasmaet har vi elektroner, ioner og nøytrale arter for å forenkle mye. Elektroner beveger seg i alle retninger, men ioner akselereres vinkelrett på overflaten. Så du har positiv ladning i bunnen av hullet og negative ladninger på toppen, og du får et elektrisk felt som prøver å frastøte innkommende ioner."

Som et resultat er det nødvendig med høye kraftnivåer for å etse grøften fullstendig. "Vi prøver å opprettholde 30 til 50 gigawatt kraft uten lysbue, og derfor må chucken være ekstremt godt polert og godt produsert," sa han.

De dype etsningene induserer også spenninger som må minimeres, spesielt fordi flerlags NAND-fabrikasjon deretter krever wafer-tynning, presis justering og hybridbinding til neste lag.

Andre prosesser

Ikke alle brikkeprodusenter produserer ledende brikker som krever EUV-litografi. Mange fabrikker utvider sine 193nm lito- og etseprosesser.

"Vi har et SOC-materiale med høy temperatur som vi nylig har begynt å introdusere, som utvider mønsterevnen og tåler høyere temperaturer, enten det brukes som underlag for et CVD-lag eller maske," sa Brian Wilbur, direktør for diversifisering av halvlederprodukter ved Bryggervitenskap.

BEOL for de trangeste metalllinjene forventes det å gjennomgå en dramatisk overgang fra doble damascene-integrasjonsordninger til subtraktiv avsetning og etsing av andre sammenkoblinger enn kobber. Her har to metaller - ruthenium og molybden - vært de mest grundig utviklet. Imidlertid er det mer sannsynlig at molybden oksiderer under etsing, noe som gjør det mer kompatibelt med doble damascene-skjemaer. Ruthenium er et edelmetall, så det har ikke de samme korrosjonsproblemene, men det er dyrere.

Enhetsstrukturer blir også intolerante overfor kantplasseringsfeil. Nye ordninger for selvjustering fra lag til lag og mellom vias og linjer vil være nødvendig, ifølge TELs Clark. "De første implementeringene vil sannsynligvis være for ting som nedgravde ordlinjer i DRAM, og MOL-metalllagene med liten tonehøyde for logikk der det er behov for høyere termisk stabilitet så vel som lavere resistivitet eller metallfrie metaller."

Neste generasjons utvikling

På lang sikt vil industrien ideelt sett gå over til back-end-prosesser med lavere termisk budsjett (nærmere 300 °C enn 400 °C) for å integrere enheter i back-end-sammenkoblingslag.

"Bransjen har et reelt behov for å begynne å bygge enheter i flere lag," sa TELs Clark. "Det betyr at vi trenger minne- og logikkenheter bygget innenfor BEOL med BEOL termiske budsjetter."

Så langt virker enheter laget med halvledende oksider lovende, både for å integrere minneenheter i en logisk BEOL-flyt, eller for å bygge CMOS-matriser på toppen av minnearrayen i DRAM-er.

Et annet betydelig skifte involverer integreringen av 2D-materialer, som forskningshus og ledende brikkeprodusenter allerede begynner å teste. Etseprosesser for materialer som wolframdisulfid eller molybdendisulfid vurderes. Filmene består av ett enkeltlag med materiale, så det er ekstremt utfordrende å utvikle fantastiske prosesser for å integrere dem.

Bærekraft

Chipmakere og materialleverandører forfølger alternative kjemier for å redusere karbonutslipp. I etsing er hovedskyldige fluorholdige gasser med høyt globalt oppvarmingspotensial.

"En grunn til at du har PFOS (perfluoroktansulfonsyre), som er problematisk, er fordi molekylet er så stabilt," sa imecs Bézard. "Lys eller kjemiske reaksjoner i atmosfæren er ikke tilstrekkelige til å bryte den ned."

Han sa at en rekke alternative gassblandinger med høyere oksygeninnhold er lettere å dissosiere og har lavere GWP. "Men enhver kandidat må levere like god eller enda høyere ytelse for å starte."

Men bærekraft er ikke spesielt en etse- eller deponeringsutfordring. Det er en helhetlig bransjeutfordring fra litografi til emballasje, der virkningen av et nytt materiale påvirker hele enhetens prosessering.

Referanse

1. K. Derbyshire, "Hva er annerledes med neste generasjons transistorer", Semiconductor Engineering, 20. oktober 2022.

Relaterte Stories

Svært selektiv etsing ruller ut for neste generasjons chips

Å produsere 3D-strukturer vil kreve kontroll på atomnivå over hva som fjernes og hva som blir liggende på en wafer.

- SEO-drevet innhold og PR-distribusjon. Bli forsterket i dag.

- PlatoAiStream. Web3 Data Intelligence. Kunnskap forsterket. Tilgang her.

- Minting the Future med Adryenn Ashley. Tilgang her.

- Kjøp og selg aksjer i PRE-IPO-selskaper med PREIPO®. Tilgang her.

- kilde: https://semiengineering.com/etch-processes-push-toward-higher-selectivity-cost-control/

- : har

- :er

- :ikke

- :hvor

- $OPP

- 000

- 1

- 10

- 13

- 20

- 2022

- 2D

- 2D-materialer

- 30

- 3d

- 50

- a

- evne

- I stand

- Om oss

- akselerere

- akselerert

- adgang

- imøtekomme

- utrette

- Ifølge

- nøyaktig

- nøyaktig

- tvers

- faktiske

- adresse

- Adopsjon

- avansert

- fordelaktige

- påvirke

- en gang til

- sikte

- alex

- Alle

- tillate

- allerede

- også

- alternativ

- beløp

- an

- analyse

- og

- En annen

- besvare

- noen

- vises

- Søknad

- applikasjonsspesifikk

- anvendt

- ER

- Army

- Array

- AS

- aspektet

- bistå

- At

- Atmosfære

- attributter

- borte

- Back-end

- Balansere

- basert

- I utgangspunktet

- BE

- Beam

- fordi

- bli

- vært

- før du

- Begynnelsen

- være

- under

- Benjamin

- BEST

- Bedre

- mellom

- Bias

- Stor

- milliarder

- Bit

- både

- Bunn

- grenser

- Brain

- Break

- Brian

- brute force

- budsjett

- Budsjetter

- Bygning

- bygget

- men

- by

- som heter

- CAN

- kandidat

- karbon

- karbonutslipp

- hvilken

- saken

- saker

- CD

- Celler

- utfordre

- utfordrende

- Chamber

- endring

- Endringer

- Kanal

- kanaler

- kostnad

- ladet

- avgifter

- lading

- kjemisk

- kjemikalier

- kjemi

- chips

- Rengjøring

- Lukke

- tett

- nærmere

- kombinasjoner

- Selskaper

- Selskapet

- kompatibel

- fullføre

- Terminado

- komplekse

- kompleksitet

- datamaskin

- konsept

- forhold

- ledningsevne

- dirigent

- ansett

- konstant

- kontakter

- innhold

- fortsette

- fortsatte

- fortsetter

- kontroll

- Kobber

- Bedriftens

- korrosjon

- Kostnad

- kostnadsreduksjon

- Kostnader

- kunne

- kurs

- skape

- skaper

- Opprette

- kritisk

- Gjeldende

- I dag

- Kunder

- Kutt

- dato

- dataanalyse

- datavitenskap

- Dager

- dyp

- leverer

- tetthet

- avhenger

- beskrevet

- utforming

- utviklet

- utvikle

- Utvikling

- enhet

- Enheter

- forskjellig

- vanskelig

- dimensjoner

- retning

- direkte

- Regissør

- diskutert

- diversifisering

- do

- gjør

- dollar

- ned

- dramatisk

- stasjonen

- tørk

- under

- hver enkelt

- Tidlig

- lett

- effekt

- effekter

- effektivitet

- enten

- Elektrisk

- elektroner

- Utslipp

- muliggjør

- ingeniør

- Ingeniørarbeid

- Ingeniører

- nok

- like

- utstyr

- utstyrt

- Tilsvarende

- spesielt

- avgjørende

- hovedsak

- etc

- Selv

- etter hvert

- Hver

- krevende

- undersøker

- henrette

- eksisterende

- forventet

- dyrt

- eksperimenter

- ekspertise

- utsatt

- strekker

- ekstremt

- vendt

- langt

- FAST

- raskere

- Egenskaper

- Noen få

- felt

- Figur

- Film

- filmer

- Først

- Blitz

- flyten

- Flows

- Fokus

- fulgt

- etter

- Til

- Tving

- skjema

- formasjon

- Forward

- fire

- Gratis

- fra

- fullt

- videre

- framtid

- mellomrom

- GAS

- general

- generere

- få

- gitt

- Global

- global oppvarming

- mål

- god

- flott

- Gruppe

- Grow

- Vokser

- Halvparten

- håndtere

- Hard

- maskinvare

- Ha

- he

- nyttig

- her.

- Høy

- High Yield

- høyere

- svært

- Hole

- Holes

- helhetlig

- Horisontal

- hus

- Hvordan

- Men

- HTTPS

- menneskelig

- Mennesker

- Hundrevis

- Hybrid

- i

- Påvirkning

- umulig

- forbedre

- forbedret

- forbedring

- in

- inkludere

- Inkludert

- Innkommende

- innlemme

- økende

- industri

- innganger

- f.eks

- i stedet

- integrere

- Integrering

- integrering

- samhandler

- interaksjoner

- sammenkoblinger

- inn

- innføre

- saker

- IT

- DET ER

- jpg

- bare

- nøkkel

- Lam

- stor

- større

- lag

- lag

- Layout

- ledende

- læring

- minst

- Nivå

- nivåer

- Life

- i likhet med

- Sannsynlig

- linje

- linjer

- LITHO

- lite

- logikk

- lenger

- Se

- tap

- Lot

- Lav

- maskin

- maskinlæring

- laget

- Hoved

- vedlikeholde

- gjøre

- Makers

- Making

- leder

- produsert

- Produsent

- produksjon

- mange

- marked

- Marketing

- Marketing Director

- maske

- materiale

- materialer

- max bredde

- Kan..

- bety

- midler

- medlem

- Minne

- metall

- Metaller

- Metrics

- kunne

- millioner

- millioner

- minimum

- mangler

- modell

- modellering

- modeller

- moduser

- MOL

- molekyl

- måneder

- mer

- mest

- flytte

- flytting

- mye

- flere

- nesten

- Trenger

- nødvendig

- behov

- negativ

- Nøytral

- Ny

- neste

- Nei.

- Noble

- node

- noder

- nå

- Antall

- oktober

- of

- ofte

- on

- gang

- ONE

- bare

- drift

- Drift

- optimalisering

- Optimalisere

- optimalisert

- or

- rekkefølge

- Annen

- andre

- vår

- ut

- enn

- Oksygen

- emballasje

- parametere

- Spesielt

- spesielt

- Mønster

- Ansatte

- utføre

- ytelse

- utfører

- kanskje

- perspektiv

- fase

- fenomen

- Philippe

- fysisk

- fysisk

- Fysikk

- Pillar

- Tonehøyde

- sentral

- Plasma

- plato

- Platon Data Intelligence

- PlatonData

- spiller

- PoC

- positiv

- muligheter

- mulig

- muligens

- potensiell

- potensielt

- makt

- kraftig

- presis

- Precision

- forutsi

- president

- press

- Problem

- problemer

- prosess

- Prosesser

- prosessering

- produsere

- Produkt

- produktutvikling

- Produksjon

- produktivitet

- Produkter

- Profil

- Profiler

- lønnsomhet

- program

- Programmering

- lovende

- bevis

- proof of concept

- publikasjoner

- Skyv

- spørsmål

- raskt

- FoU

- Rampe

- område

- Sats

- priser

- ratio

- å nå

- Reager

- reaksjon

- reaksjoner

- ekte

- ekte liv

- grunnen til

- nylig

- Anbefaling

- anbefales

- redusere

- redusere

- reduksjon

- reflektere

- regelmessig

- slipp

- pålitelig

- avhengige

- fjerning

- fjerne

- fjernet

- fjerne

- repeterbar

- gjentatt

- erstatte

- rapporterer

- krever

- påkrevd

- Krav

- Krever

- forskning

- resultere

- Resultater

- avslører

- ikke sant

- ROBERT

- Rolle

- ruller

- omtrent

- regler

- Kjør

- Sa

- samme

- sier

- Skala

- skalering

- ordninger

- Vitenskap

- søker

- sett

- selektiv

- halvledere

- senior

- forstand

- innstilling

- flere

- skift

- bør

- Silicon

- Enkelt

- forenkle

- ganske enkelt

- simulering

- enkelt

- dyktig

- liten

- So

- Software

- Solutions

- LØSE

- noen

- et sted

- kilde

- Rom

- spesifikk

- spesifikasjoner

- specs

- fart

- Stabilitet

- stabil

- stablet

- Stabler

- Staff

- stadier

- Begynn

- startet

- Trinn

- Steps

- Still

- stresset

- struktur

- I ettertid

- betydelig

- slik

- plutselig

- tilstrekkelig

- foreslår

- leverandører

- overflaten

- overraskelse

- Bærekraft

- bærekraftig

- Sweep

- Sveitsiske

- Systemer

- Ta

- ta

- Snakk

- målrettet

- lag

- Teknisk

- Technologies

- Teknologi

- Teknologiutvikling

- begrep

- test

- Testing

- tester

- enn

- Det

- De

- Fremtiden

- deres

- Dem

- deretter

- Der.

- termisk

- Disse

- de

- ting

- Tredje

- denne

- grundig

- tusener

- tre

- Gjennom

- nivået

- strammere

- tid

- timing

- til

- sammen

- ton

- TONE

- også

- topp

- berøre

- mot

- overføres

- Transform

- overgang

- Trend

- prøve

- to

- typisk

- typisk

- underliggende

- uforutsigbare

- upon

- oppover

- us

- bruke

- brukt

- Bruker

- ved hjelp av

- bruke

- verifisert

- vertikal

- vertikalt

- veldig

- av

- levedyktig

- Vice President

- vincent

- virtuelle

- volatile

- ønsker

- ønsker

- var

- Vei..

- we

- uker

- VI VIL

- Hva

- når

- om

- hvilken

- mens

- hele

- hvorfor

- vil

- med

- innenfor

- uten

- ord

- Arbeid

- arbeid

- virker

- ville

- år

- år

- Utbytte

- givende

- rentene

- du

- zephyrnet

- null