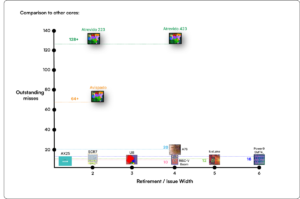

Chiplets har forenklet ett designområde, men åpnet pandoras boks på en annen front. Simuleringskompleksiteten til hver brikke er lavere, men nå har chiplet-til-chiplet-forbindelsen blitt kompleks. Folk eksperimenterer med forskjellige sammenkoblingsprotokoller, varianter av UCIe, modifisering av UCIe-innstillinger, grensesnitthastigheter, antall fysiske lag og så ett. Legg nå til eldre standarder som AXI, nye protokoller som PICe6.0 og cache-koherens til blandingen.

Alt i alt skaper dette et helt nytt sett med eksperimenter. En som tradisjonell emulering og RTL-modellering ikke vil fungere for. Du må først bruke en innsats på å bytte arkitektur, ikke bare på å velge komponenter. Dette vil bety at du må utføre trafikkanalyse, applikasjonspartisjonering, systemdimensjonering og påvirkning av ulike typer fysiske lag. Også, avhengig av applikasjonen, vil benchmark være veldig forskjellig.

UCIe-spesifikasjonen er ny, og det er ingen klare standarder. UCIe-spesifikasjonen gir også kun veiledning om ventetid og kraft. Begge er strenge krav. Dette betyr at en Power-Performance-Area-studie er uunngåelig. Siden du har protokoll-protokoll-protokollkonvertering som PCIe 6.0 til UCIe til AXI, er modelleringsoppsettet komplekst.

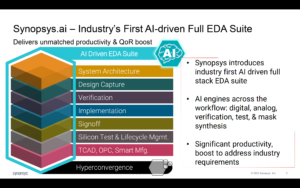

En løsning er å se på systemmodellering ved hjelp av VisualSim fra mirabilis Design. De har nylig lansert en UCIe-systemnivå IP-modell og vil demonstrere en rekke brukstilfeller av sammenkoblingen på Chiplet Summit. For å veilede designere, har de publisert en guide med mange brukstilfeller, forventede kraftytelsesresultater og alternativer for optimalisering. De har både en papirpresentasjon og en stand på Summit. Jeg håper å se deg der!

Her er også lenken til en artikkel som folk kan få: Ytelsesmodellering av et heterogent datasystem basert på UCIe Interconnect Architecture

Abstrakt:

Dagens komplekse brikkedesign på ledende noder består vanligvis av flere dies (eller brikker). Tilnærmingen tillater dyser fra forskjellige produsenter eller prosesser, samt gjenbrukbar IP. Designere trenger en modell på systemnivå for å evaluere ulike implementeringer av slike komplekse situasjoner.

Et eksempelsystem består av en I/O-brikke, en kjernebrikke med lav effekt, en kjernebrikke med høy ytelse, en audio-videobrikke og en analog brikke, sammenkoblet ved hjelp av UCIe-standarden (Universal Chiplet Interconnect Express).

Teamet vårt vurderte flere scenarier og konfigurasjoner, inkludert avanserte og standardpakker, varierte trafikkprofiler og ressurser, og en retimer for å utvide rekkevidden og evaluere hendelser ved tidsavbrudd. Identifisering av styrker og svakheter ved UCIe-sammenkoblingen for oppdragsapplikasjoner hjalp oss med å oppnå den optimale konfigurasjonen for hvert delsystem for å møte ytelses-, kraft- og funksjonskrav.

Om Mirabilis Design Inc.

Mirabilis Design er et programvareselskap i Silicon Valley, som leverer programvare og opplæringsløsninger for å identifisere og eliminere risiko i produktspesifikasjonen, nøyaktig forutsi de menneskelige og tidsmessige ressursene som kreves for å utvikle produktet, og forbedre kommunikasjonen mellom ulike ingeniører.

team.

VisualSim Architect kombinerer intellektuell eiendom, modellering på systemnivå, simulering, miljøanalyse og applikasjonsmaler for å forbedre modellkonstruksjon, simulering, analyse og RTL-verifisering betydelig. Miljøet gjør det mulig for designere å raskt konvergere til et design som oppfyller et mangfoldig sett av gjensidig avhengige tids- og kraftkrav. Den brukes veldig tidlig i designprosessen parallelt med (og som en hjelp til) den skriftlige spesifikasjonen og før en implementering (for eksempel RTL, programvarekode eller skjematisk) av produktet.

Les også:

WEBINAR: Hvordan oppnå 95 %+ nøyaktig effektmåling under utforskning av arkitektur

Kartlegging av SysML til maskinvarearkitektur

Modellbaserte designkurs for studenter

Del dette innlegget via:

- SEO-drevet innhold og PR-distribusjon. Bli forsterket i dag.

- PlatoData.Network Vertical Generative Ai. Styrk deg selv. Tilgang her.

- PlatoAiStream. Web3 Intelligence. Kunnskap forsterket. Tilgang her.

- PlatoESG. Karbon, CleanTech, Energi, Miljø, Solenergi, Avfallshåndtering. Tilgang her.

- PlatoHelse. Bioteknologisk og klinisk etterretning. Tilgang her.

- kilde: https://semiwiki.com/ip/mirabilis-design-ip/341339-chiplets-open-pandoras-box/

- : har

- :er

- :ikke

- a

- nøyaktig

- nøyaktig

- Oppnå

- legge til

- avansert

- Aid

- tillater

- langs

- også

- an

- analyse

- og

- En annen

- Søknad

- søknader

- tilnærming

- arkitektur

- ER

- AREA

- AS

- At

- basert

- BE

- bli

- før du

- benchmark

- benchmarks

- mellom

- både

- Eske

- men

- cache

- CAN

- Kan få

- saker

- chip

- fjerne

- kode

- skurtreskerne

- Kommunikasjon

- Selskapet

- helt

- komplekse

- kompleksitet

- komponenter

- databehandling

- Gjennomføre

- Konfigurasjon

- ansett

- består

- konstruksjon

- konvergerer

- Konvertering

- Kjerne

- kurs

- skaper

- demonstrere

- avhengig

- utforming

- design prosess

- designere

- design

- utvikle

- forskjellig

- diverse

- under

- hver enkelt

- Tidlig

- innsats

- eliminere

- emulering

- muliggjør

- Miljø

- evaluere

- hendelser

- eksempel

- forventet

- eksperimentere

- eksperimenter

- ekspress

- utvide

- Først

- Til

- fra

- foran

- funksjonelle

- generelt

- få

- veiledning

- veilede

- maskinvare

- Ha

- hjulpet

- her.

- høy ytelse

- håp

- Hvordan

- Hvordan

- HTTPS

- menneskelig

- i

- identifisere

- identifisering

- Påvirkning

- gjennomføring

- implementeringer

- forbedre

- in

- Inkludert

- intellektuell

- intellektuell eiendom

- sammenhengende

- Interface

- IP

- IT

- jpg

- bare

- Ventetid

- lansert

- lag

- lag

- Legacy

- Nivå

- i likhet med

- LINK

- Se

- masse

- Lav

- lavere

- Produsenter

- max bredde

- bety

- midler

- måling

- Møt

- møter

- Oppdrag

- bland

- modell

- modellering

- modellering

- flere

- Trenger

- Ny

- Nei.

- noder

- nå

- Antall

- få

- of

- on

- ONE

- bare

- åpen

- åpnet

- optimal

- optimalisering

- alternativer

- or

- pakker

- Papir

- Parallel

- ytelse

- fysisk

- plato

- Platon Data Intelligence

- PlatonData

- Post

- makt

- forutsi

- presentasjon

- prosess

- Prosesser

- Produkt

- Profiler

- eiendom

- protokoller

- gir

- gi

- publisert

- raskt

- å nå

- Lese

- nylig

- påkrevd

- Krav

- Ressurser

- Resultater

- gjenbruk

- Risiko

- scenarier

- se

- velge

- sett

- innstillinger

- oppsett

- flere

- betydelig

- Silicon

- Silicon Valley

- forenklet

- simulering

- situasjoner

- So

- Software

- løsning

- Solutions

- spesifikasjon

- hastigheter

- bruke

- Standard

- standarder

- styrker

- strengere

- Studer

- slik

- Summit

- system

- lag

- maler

- Det

- De

- Der.

- de

- denne

- tid

- til

- tradisjonelle

- trafikk

- Kurs

- typer

- Universell

- us

- bruke

- brukt

- ved hjelp av

- Dal

- variasjoner

- Verifisering

- veldig

- av

- svakheter

- VI VIL

- hvilken

- vil

- med

- Arbeid

- skrevet

- du

- zephyrnet