Chiplets begynner å påvirke chipdesign, selv om de ennå ikke er mainstream og ingen kommersiell markedsplass eksisterer for denne typen herdet IP.

Det er pågående diskusjoner om silisiums livssyklusstyring, den beste måten å karakterisere og koble disse enhetene på, og hvordan man skal håndtere slike problemer som ujevn aldring og termisk misforhold. I tillegg pågår en stor innsats for å forbedre observerbarheten av Chiplets over tid, noe som er spesielt viktig ettersom disse enhetene brukes i sikkerhetskritiske og virksomhetskritiske applikasjoner.

Alle disse problemene må løses for å muliggjøre utbredt bruk, og brikkeindustrien har erkjent at nedbremsingen av Moores lov kombinert med faste trådkorsstørrelser vil kreve endringer i hvordan brikker utformes, produseres og pakkes. Det er fysisk umulig å passe alle funksjonene som kreves for mange applikasjoner i en enkelt SoC, og målet nå er en ryddig, forutsigbar og repeterbar tilnærming til å skille mange av disse komponentene. I teorien vil dette tillate enheter å bli lettere tilpasset, raskere tiden til markedet og unngå kostbar skalering av komponenter som ikke krever det, for eksempel analoge funksjoner.

Å oppnå dette målet vil imidlertid kreve å løse noen komplekse og vanskelige problemer. For det første vil det kreve mye bedre observerbarhet, overvåking og analyse av hva som legges inn i en pakke. Mens konseptet med å legge flere sjetonger i en pakke dateres tilbake til 1990-tallet med multi-chip moduler, med chiplets er dysene vanligvis mindre og tynnere, og dynamikken i hvordan man karakteriserer, tester og observerer dem har endret seg betydelig.

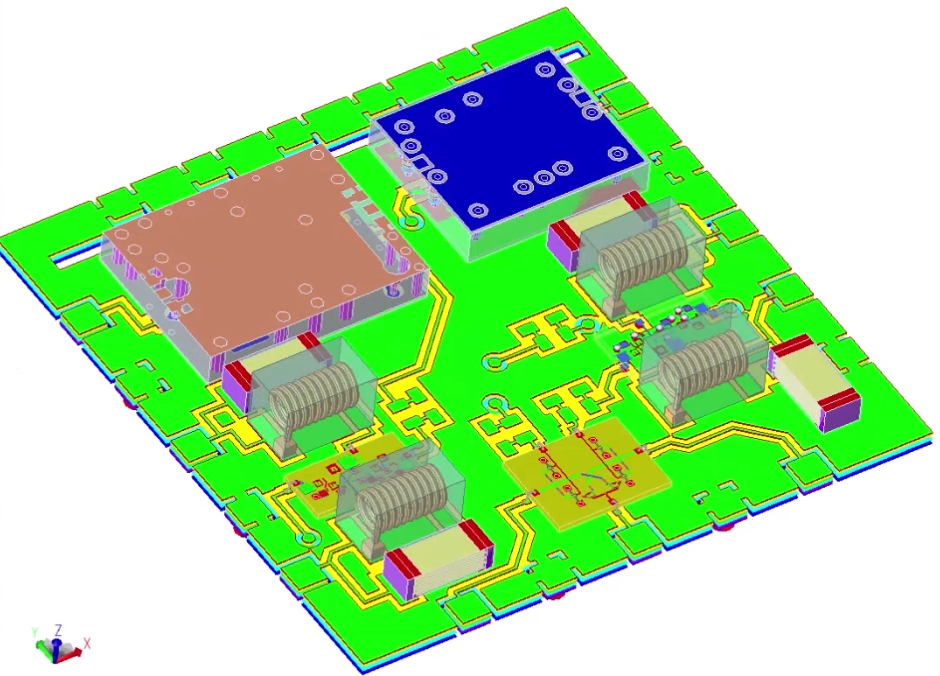

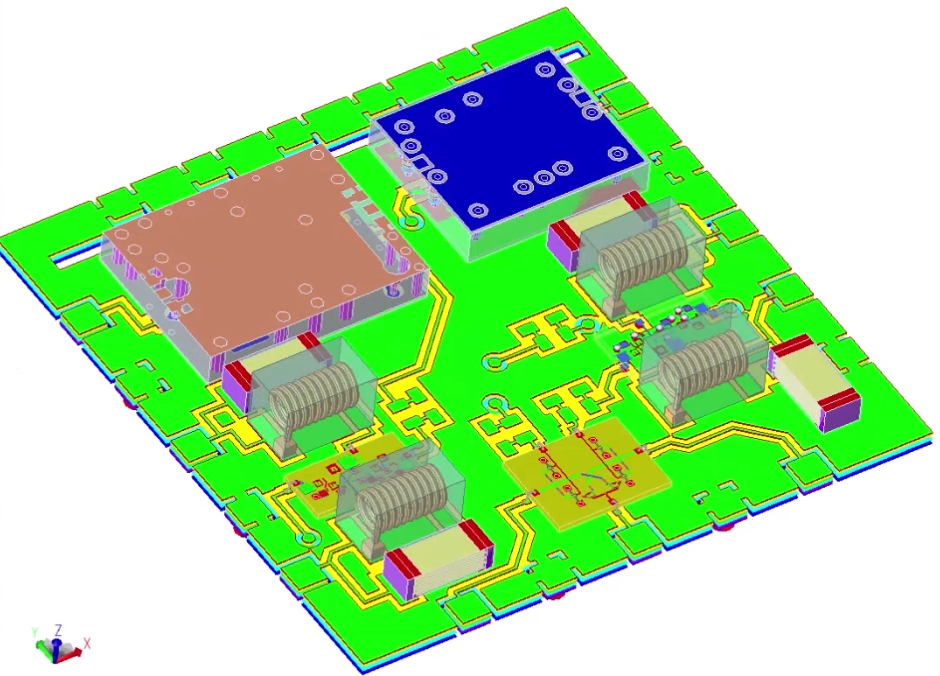

"Historisk har vi kalt disse multi-chip-modulene, som er veldig populære i den trådløse verden i dag," sa Nilesh Kamdar, leder for RF/mikrobølgeportefølje ved Nøkkelsikt. "Du plukker opp hvilken som helst smarttelefon, og den trådløse delen av smarttelefonen er en frontmodul som er 20 til 30 brikker presset sammen på en liten plass som er mindre enn en negl. Det har skjedd i bransjen i minst et tiår, om ikke lenger. Også flere romfarts- og andre høyfrekvente problemer har krevd denne typen integrasjon, så vi har gjort dette tidligere.»

Fig. 1. RF-moduloppsettet med flere brikker vist i Keysights PathWave ADS. Kilde: Keysight

Det store skiftet som nå pågår involverer en mye bredere anvendelse for denne tilnærmingen, samt forbedringer i brikkedesignet, og standardmåter for å koble til, teste og måle hva som skjer inne i selve brikkene, samt den avanserte pakken som omgir dem.

"Bil er et godt eksempel på hva som endrer seg," sa Kamdar. "På en nylig konferanse snakket en visepresident fra en stor OEM om ikke å kunne ta et datasenter og sette det i baksetet på en bil, fordi det er det som trengs for å ha et autonomt kjøretøy i dag. Hvis du gjør mer integrering – og hvis du på en eller annen måte får brettet til å forsvinne, og alt presses sammen – kan vi kanskje presse det vertikalt inn i baksetet på en bil. Det er mange lignende brukstilfeller. Strømbehovet for brikker kan være lavere hvis du vurderer fysiske datasentre. Det er mange fordeler, og det er det som driver chiplets i dag.»

Imidlertid er disse endringene villedende komplekse, og industrien kan trenge å gå tilbake til skolen på dette. "Å bygge chiplets i stor skala er en så annerledes modell at vi alle trenger å revurdere ferdighetene våre," sa han. "Vi må revurdere hvordan organisasjoner er satt opp og hvordan arkitektur skjer. Vi må revurdere rollen til en systemdesigner. De kan ha sett på ting på en annen måte, og de kan ha sagt: 'Jeg er en systemdesigner. Jeg designer spesifikasjonene for systemene. Jeg deler det ned i komponenter på mindre nivå, individuelle IC-er og distribuerer spesifikasjonene. Jeg går bort og kommer tilbake seks måneder senere og ser hvordan alle gjorde det.’ Kanskje det ikke engang er mulig. Kanskje er det flere systemdesignere som må eksistere opp og ned i kjeden. Det er slike samtaler som må skje. Innenfor de største aktørene i bransjene skjer disse samtalene allerede, men ikke overalt.»

Antall potensielle interaksjoner i sammenheng med en multi-chiplet-design er betydelig, og i mange tilfeller designspesifikke. "Hvis du tror på multi-die, hvis du tror på chiplets, må du tro at det bare vil forverre hele [design og integrering]-problemet," sa Shekhar Kapoor, seniordirektør for produktlinjeledelse for Synopsys EDA Group. "Chiplets kommer til å komme fra mange steder, mange kilder. Det kommer til å være mange valg, mange alternativer for alle. Det største problemet er dagens bruk rundt alt dette. Store selskaper gjør dette på en skreddersydd og tilpasset måte. Men hvis du går bredt ut med standardisering, hvordan vet du at en brikke som kommer inn kommer til å passe inn i miljøet, i produktet du prøver å bygge?»

Til tross for fokus på standarder som UCIe og Bunch of Wires, er det fortsatt nyanser når det gjelder hvordan de enkelte brikkene karakteriseres i sammenheng med et system. «Hvordan vet du egentlig profilen til det? Det er der enda mer overvåking vil komme inn i bildet, som nesten er som en signatur, sa Kapoor. "Du kan lese den og vite om den er ideell for miljøet ditt. Gitt at industrien beveger seg mot mer chiplet-aktivering, vil dette være en kjernebetraktning. Flere krav vil dukke opp, flere standarder vil dukke opp, så da kan du se om noe kommer til å passe eller ikke."

Det er også andre utfordringer å overvinne.

"Med chiplets er alle høyhastighetssignalene i pakken, så observerbarhet er mye mer utfordrende," sa Sue Hung Fung, produktlinjemarkedssjef for UCIe ved Cadence. «Dette kan gjøres gjennom lenkefeilsjekker, øyeskanninger, BiST osv., for å komme til en kjent god terning (KGD). Alle testmetoder er bygget rundt dette. I tillegg vil det være verdifullt å ha gode monitorer for helsen til koblingen, og det er nye og forskjellige forslag fra forskjellige leverandører."

Nøkkelen er å overvåke signalkvaliteten i sammenheng med resten av komponentene i en pakke, noe som blir vanskeligere ettersom flere funksjoner deles opp i chiplets.

«Kan vi overvåke signalene og kvaliteten på disse under dataoverføring? Treningsteknikker utføres før oppdragsmodus for å forbedre robustheten i dataoverføringen,» bemerket Hung Fung. «Omskolering er ikke ønsket, da det kan føre til dataavbrudd. Vi må være i stand til kontinuerlig å overvåke og rapportere hvert kjørefelt og oppdage eventuelle hendelser som kan forårsake feil før en feil oppstår. Forebygging av systemsvikt og reparasjon av disse feilene inkluderer redundant filomlegging eller andre reparasjonsmetoder for å oppdage marginalt sviktende kjørefelt. Trening og kontinuerlig overvåking av disse interne chiplet-signalene er utfordringene for å analysere koblingsatferden."

Arbeidsgrupper for UCIe er ute etter å standardisere noe av denne observerbarheten for å ha et åpent lenkeøkosystem. Men å legge til observerbarhet og overvåking kan også variere sterkt etter vertikalt segment.

Randy Fish, direktør for produktlinjeledelse for Synopsys EDA Group, forklarte at fordi det ikke har vært noen standardtilnærming og få kommersielle leverandører for observerbarhetsløsninger, har nesten alle løsningene blitt skreddersydd. "Hvis du går inn i noen av de ledende semifinalene, gjør de noe," sa han. "Spørsmålet er, er det funksjoner rundt multi-die som vil tvinge oss til å standardisere for å ha en sammenhengende eller sammenhengende infrastruktur for overvåking og feilsøking - i utgangspunktet for å se hva som skjer, spesielt hvis du får flere dies fra flere leverandører. Noen av multi-die-løsningene går inn i bilindustrien, og der bryr de seg om ting som aldring og hva som skjer med disse dør. Og som vi vet, er det avanserte noder. Det er ikke slik at du har 6 dører av moden 10 år gammel teknologi. Dette er avanserte noder som ikke har en lang historie. Av den grunn er det en rekke faktorer som tvinger dette til å skje."

Chiplets introduserer også noen interessante kontraster. Keysights Kamdar bemerket at under et nylig CEO-panel sa en av paneldeltakerne at chiplets har en unik dikotomi. "På den ene siden kan hver brikke være en uavhengig IP som du kan anskaffe fra en IP-leverandør og integrere den i systemet ditt til relativt lave kostnader, relativt enkelt. Imidlertid tvinger hele stabelen du prøver å bygge deg plutselig til å vite alt. Tidligere kunne du bare ha sagt: 'Jeg trenger seks ting. Jeg skal kjøpe fem fra en IP-leverandør, og de vil finne ut hva den trenger. Jeg skal fokusere på en.’ Men nå lykkes du kanskje ikke med det. Du kan faktisk trenge å vite hvordan du gjør alle seks, og finne ut hvordan alt dette skjer fordi kompleksiteten til problemet nettopp gikk opp. Dette kan tvinge bransjen til å i utgangspunktet bare la de store aktørene finne ut av dette. Det kan ta mye lengre tid for de mindre leverandørene å være i stand til å lykkes i dette miljøet.»

Likevel vil det kreve mer enn ett selskap for å akselerere chipletintegrasjon og -adopsjon.

"Keysight deltok på TSMC Symposium, som er en mer offentlig begivenhet, og som en oppfølging var det en workshop med bare partnerne som er en del av 3D Fabric Alliance," sa Kamdar. "TSMC startet og avsluttet hele dagen med å snakke om hvordan vi alle trenger å jobbe med dette sammen, noe som ble gjentatt av andre deltakere, inkludert AMD og Qualcomm. Høyttalere fra begge selskapene sa at ikke et eneste EDA-selskap vet hvordan de skal løse chiplet-problemet på egen hånd. Hele bransjen må samarbeide.»

Tekniske utfordringer

En annen viktig bekymring med chiplets er varmespredning. Dette er en del av karakteriseringen, men det er også svært avhengig av brukstilfeller, pakkevalg og den generelle system-i-pakke-arkitekturen.

"For chiplets er marginaliteten i designet slank gitt optimal PPA (målrettet mot aggressiv pj/bit og beachfront density), som er avgjørende når man designer chiplet PHYs," sa Rishi Chugh, visepresident for produktmarkedsføring, IP Group i Cadence. "Pålitelighet er nøkkelen, og det samme er observerbarhet for å screene KGD, samt få den til kommersiell operasjonell suksess. Dataintegritetsordninger som CRC (syklisk redundanssjekk), øyeskanning, BiST og overvåkingskretser er implementert i designet for robusthet, og designet må være overutstyrt med feilmekanismer for å sikre at datalinjen er spenstig."

Et helt kapittel i UCIe-protokollen er dedikert til initialisering og trening knyttet til UCIe-protokollen, som dekker observerbarhetsaspektet ved protokollen, la Chugh til.

I tillegg er det debatt om hvorvidt det faktiske grunnleggende ved å legge til observerbarhet i et system er den vanskeligste delen, eller om endringen i tenkning rundt disse konseptene er vanskeligere.

«Det er faktisk ikke så komplisert i motsetning til andre ting, fordi det «bare» er en annen blokk å koble til. Det er observasjon, og vi har evner til å spore ting, sier Frank Schirrmeister, visepresident for løsninger og forretningsutvikling hos Arteris IP. "Brukere etterspør allerede ting som å se på registrene fra et programvareperspektiv. Så nå blir utfordringen å gjøre disse registrene tilgjengelige i NoC. Fra et NoC-perspektiv er det selve protokollene som CHI, ACE, AMBA, OCP eller andre, og det er mekanismene til språket - hvordan de snakker og hvordan de samhandler. Innenfor NoC, med de mer komplekse protokollene, er det ting som skjer over flere sykluser, så du må vente på svar, du setter ting i pipelinen.»

Dette ligner på spekulativ utførelse i prosessorer. "Vi snakker om disse kredittene, som hvor lenge må jeg vente på svar og så videre," forklarte Schirrmeister. "Dette er alle deler av protokollene. I NoC må du forstå problemer som hvor dype bufferne er? Når venter jeg egentlig på data? Det er delvis ytelse. Deretter, for observerbarheten, kan du koble til dataene, og sensorene kan bruke sitt eget nettverk avhengig av hvordan du vil konfigurere det. Når det gjelder on-chip monitorer, må du bestemme deg for om du for eksempel skal sette dette på en spesiell observerbarhetsbuss. Det er alltid en diskusjon hvor mye feilsøking jeg faktisk har? På slutten av dagen er det "bare" en annen sammenkobling av disse komponentene, og du må bestemme hvordan du eksporterer den ut av brikken, og så videre. Hvor mye du lagrer på chip er et spørsmål om hvor mye silisiumeiendom jeg er villig til å bruke for det?»

Det blir spesielt viktig når du syr sammen chiplets. "Hvordan sikrer jeg at jeg har nok plass til denne beregningsenheten som bare ser ut som data, som faktisk ikke tilfører noen verdi til den umiddelbare funksjonen?" spør Gajinder Panesar, sjefsarkitekt i Picocom. "Dessuten er jeg kanskje ikke en overvåkingsekspert, men jeg vet at jeg trenger det. Så jeg trenger noe som sier: «Bare trykk på den knappen.» Du har et miljø, vi designer, og «dette» skjer. Ideelt sett bør vi observere oppførselen til CPU-ytelsen og deretter dynamisk justere visse aspekter av kjernen for å få bedre ytelse."

En av brikkene som ennå ikke er utviklet er dynamisk kontroll av enhetene, og justeringene som kan gjøres i løpet av levetiden.

"Si at vi har all muligheten til å modellere alt på forhånd," sa Lee Harrison, direktør for produktmarkedsføring i Tessent-gruppen på Siemens Digital Industries programvare. "Vi har alle skjermer innebygd for å gjøre ting i systemet, men det lukker den sløyfen. For de nyere geometriene er det fortsatt mye å lære for å virkelig optimalisere hvordan vi kan justere de forskjellige parameterne til enheten for å utvide denne påliteligheten. Stykket som lukker sløyfen til systemet i livet er der det er en enorm mengde verdi. Likevel er det fortsatt arbeid å gjøre.

Endre ansvarsroller

Kommersielle chiplets legger til et annet vanskelig problem, som er hvem som er ansvarlig når noe uventet blir observert eller går galt.

"Hvis jeg er en brikkeprodusent, lager jeg brikken, og jeg kan gå gjennom en OSAT for testing,” sa Paul Karazuba, visepresident for markedsføring ved Expedera. "Jeg kan bruke ASE som et pakkehus, men jeg selger det med mitt navn og min garanti. Det kommer til å bli interessant når vi har chiplets. I alle våre møter om chiplets reises det alltid spørsmål om hvem som skal ha ansvaret for hva. La oss si at jeg skulle lage en AI-chiplet og jeg selger inn i et system og en pakke med seks andre selskapers brikker. Hvilket selskap skal være garantien? Hvilket selskap vil utføre tjenesten på den? Det er ingen reell konsensus akkurat nå."

Arbeidsideen er at selskapet hvis navn står på utsiden av pakken vil være ansvarlig, sa Karazuba. "Det selskapet kommer sannsynligvis til å være det som har et sluttansvar for tjenesten til kundene sine, men det bringer inn et annet lag med tjenester som chipletprodusenter må tilby, og det kommer til å bli interessant. Frykten er at rundt 2000, Intel-Microsoft-Dell-trekanten av alle som peker fingre mot hverandre. Det er en uuttalt frykt i bransjen akkurat nå."

Og kanskje er det ikke en av chipletene. Hva skjer hvis et underlag eller en fysisk sammenkobling er defekt?

"Fra et testsynspunkt kan en chiplet teste helt bra," sa Karazuba. "Men når det er et fysisk sammenkoblingsproblem, hvordan forstår brikkeprodusenten det kontra multichipmodulprodusenten? Det kommer til å bli interessant. Den eneste måten å løse disse problemene på er å prøve og feile. Vi kan designe så mange juridiske kontrakter vi vil som halvlederprodusenter, men vi er i ukjent farvann her og ting må justeres. Støttemodeller må justeres for å gjenspeile den nye virkeligheten med at monolitisk silisium ikke er et primært kjøretøy i halvledersalget.»

Synopsys' Kapoor har allerede sett refleksjoner i økosystemet. "Det har alltid vært økosystemer, men ditt aktive økosystem uansett hvor du er var kanskje den neste sirkelen rundt det. Hvis du driver med design, vil du bare være bekymret for støperidesignreglene og designregelmanualen. Det endrer seg når du snakker om chiplets. Selv med designet, tenker du nå på å teste enda mer enn du noen gang har gjort før. du snakker med Fordelaktig og Teradyne. Selv om du bare er en designer, må du finne ut hva du trenger å sette inn fra et ATPG-synspunkt og hvordan det skal testes. Den relevante økosystemstørrelsen øker."

Likevel har industrien ikke noe annet valg enn å løse disse problemene. "Vi har snakket om chiplet-markedet. Du vil kunne trekke ut en terning og ha den klar. Vi er fortsatt langt unna det, men trinnene blir tydeligere om hva vi må oppnå. Tilkobling er grunnleggende. UCIe-standarder er et must, og med det kommer protokollene og reglene fra et tilkoblingssynspunkt som du må etablere. Neste ville være veldig klart definerte modeller. Utfordringene vi snakker om påvirkes av termikk, spesielt, og kraft. Noen standarder eksisterer allerede rundt det, og vi vil gå fra tilkobling til den karakteriserte modellen, slik at vi kan bruke den mer pålitelig. Da trenger vi en slags signatur, som er der vi fra et testbarhetssynspunkt kan se levetiden og hvordan alle dør kommer til å endre seg annerledes.»

Inndataene til alt dette vil komme fra chip- og systemmonitorer, som også må være basert på standarder.

- SEO-drevet innhold og PR-distribusjon. Bli forsterket i dag.

- PlatoAiStream. Web3 Data Intelligence. Kunnskap forsterket. Tilgang her.

- Minting the Future med Adryenn Ashley. Tilgang her.

- Kjøp og selg aksjer i PRE-IPO-selskaper med PREIPO®. Tilgang her.

- kilde: https://semiengineering.com/chiplet-planning-kicks-into-high-gear/

- : har

- :er

- :ikke

- :hvor

- $OPP

- 1

- 20

- 30

- 3d

- a

- evne

- I stand

- Om oss

- akselerere

- Oppnå

- aktiv

- faktiske

- faktisk

- legge til

- la til

- legge

- tillegg

- justert

- justeringer

- Adopsjon

- annonser

- avansert

- Aerospace

- aggressiv

- Aldring

- AI

- Alle

- Allianse

- tillate

- allerede

- også

- alltid

- am

- AMD

- beløp

- an

- analyse

- analyserer

- og

- En annen

- noen

- Søknad

- søknader

- tilnærming

- arkitektur

- ER

- rundt

- AS

- aspektet

- aspekter

- assosiert

- At

- automotive

- autonom

- autonome kjøretøy

- tilgjengelig

- unngå

- borte

- tilbake

- basert

- I utgangspunktet

- BE

- fordi

- blir

- bli

- vært

- før du

- Begynnelsen

- være

- tro

- Fordeler

- BEST

- Bedre

- Stor

- Biggest

- Bit

- Blokker

- borde

- både

- Break

- Bringer

- bred

- bredere

- bygge

- bygget

- Bunch

- buss

- virksomhet

- forretningsutvikling

- men

- knapp

- kjøpe

- by

- Cadence

- som heter

- CAN

- evner

- bil

- hvilken

- saken

- saker

- Årsak

- sentrum

- Sentre

- konsernsjef

- viss

- kjede

- utfordre

- utfordringer

- utfordrende

- endring

- endret

- Endringer

- endring

- Kapittel

- karakter

- karakterisert

- sjekk

- Sjekker

- sjef

- chip

- chips

- valg

- valg

- Circle

- tydeligere

- klart

- Stenger

- lukking

- SAMMENHENGENDE

- sammenhengende

- kombinert

- Kom

- kommer

- kommer

- kommersiell

- Selskaper

- Selskapet

- komplekse

- kompleksitet

- komplisert

- komponenter

- konsept

- konsepter

- Bekymring

- bekymret

- Konferanse

- Koble

- tilkoblet

- Tilkobling

- Konsensus

- Vurder

- hensyn

- kontekst

- kontinuerlig

- kontinuerlig

- kontrakter

- kontrast

- kontraster

- kontroll

- samtaler

- Kjerne

- Kostnad

- kunne

- dekker

- prosessor

- CRC

- studiepoeng

- avgjørende

- Gjeldende

- Kunder

- tilpasset

- sykluser

- dato

- Datasenter

- datasentre

- datoer

- dag

- avtale

- debatt

- tiår

- bestemme

- dedikert

- dyp

- definert

- tetthet

- avhengig

- avhengig

- utforming

- designet

- designer

- designere

- utforme

- ønsket

- utviklet

- Utvikling

- enhet

- Enheter

- gJORDE

- Die

- forskjellig

- vanskelig

- digitalt

- Regissør

- forsvinne

- diskusjon

- diskusjoner

- distribuere

- do

- gjør

- gjør

- gjort

- ikke

- ned

- kjøring

- under

- dynamisk

- dynamisk

- dynamikk

- hver enkelt

- lett

- økosystem

- økosystemer

- innsats

- dukke

- muliggjøre

- aktivering

- slutt

- nok

- sikre

- Hele

- enhet

- Miljø

- feil

- spesielt

- etablere

- eiendom

- etc

- Selv

- Event

- hendelser

- NOEN GANG

- alle

- alt

- eksempel

- gjennomføring

- eksisterer

- finnes

- dyrt

- Expert

- forklarte

- eksportere

- utvide

- øye

- stoff

- faktorer

- sviktende

- Failure

- langt

- Mote

- frykt

- Noen få

- Fiken

- Figur

- Fisk

- passer

- fikset

- Fokus

- Til

- Tving

- Krefter

- videre

- Støperi

- fra

- foran

- funksjon

- funksjoner

- fundamental

- Fundamentals

- Gear

- få

- få

- gitt

- Go

- mål

- Går

- skal

- god

- flott

- sterkt

- Gruppe

- Gruppens

- hånd

- skje

- Skjer

- skjer

- Ha

- å ha

- he

- Helse

- her.

- Høy

- Høy frekvens

- svært

- historie

- hus

- Hvordan

- Hvordan

- Men

- HTTPS

- stort

- i

- ICS

- Tanken

- ideell

- if

- umiddelbar

- Påvirkning

- påvirket

- implementert

- viktig

- umulig

- forbedre

- forbedringer

- in

- inkluderer

- Inkludert

- økende

- uavhengig

- individuelt

- bransjer

- industri

- Infrastruktur

- i utgangspunktet

- innganger

- integrere

- integrering

- integritet

- samhandle

- interaksjoner

- interessant

- intern

- inn

- introdusere

- IP

- utstedelse

- saker

- IT

- DET ER

- bare

- Kapoor

- nøkkel

- Kicks

- Type

- Vet

- kjent

- Lane

- Språk

- stor

- seinere

- Law

- lag

- Layout

- føre

- ledende

- læring

- minst

- Lee

- Lovlig

- Nivå

- Livssyklus

- levetid

- livstid

- i likhet med

- linje

- LINK

- Lang

- lenger

- ser

- Lot

- Lav

- laget

- Mainstream

- større

- gjøre

- maker

- Makers

- Making

- ledelse

- leder

- håndbok

- produsert

- mange

- marked

- Marketing

- markedsplass

- moden

- max bredde

- Kan..

- måle

- mekanismer

- møter

- metoder

- kunne

- Oppdrag

- Mote

- modell

- modeller

- moduler

- Moduler

- Overvåke

- overvåking

- skjermer

- Monolithic

- måneder

- mer

- flytting

- mye

- flere

- må

- my

- navn

- Trenger

- behov

- nettverk

- Ny

- neste

- Nei.

- noder

- bemerket

- nå

- Antall

- observere

- of

- off

- on

- ONE

- pågående

- bare

- åpen

- operasjonell

- optimal

- Optimalisere

- alternativer

- or

- rekkefølge

- organisasjoner

- Annen

- Andre deltakere

- andre

- vår

- ut

- utenfor

- enn

- samlet

- Overcome

- egen

- pakke

- pakket

- emballasje

- panel

- parametere

- del

- deltakere

- Spesielt

- spesielt

- partnere

- deler

- Past

- paul

- ytelse

- perspektiv

- fysisk

- fysisk

- plukke

- bilde

- brikke

- stykker

- rørledning

- steder

- planlegging

- plato

- Platon Data Intelligence

- PlatonData

- spillere

- Point

- Synspunkt

- Populær

- portefølje

- mulig

- potensiell

- makt

- Forutsigbar

- president

- trykk

- Forebygging

- tidligere

- primære

- Før

- sannsynligvis

- Problem

- problemer

- prosessorer

- Produkt

- Profil

- forslag

- protokollen

- protokoller

- gi

- offentlig

- sette

- Sette

- Qualcomm

- kvalitet

- spørsmål

- hevet

- Lese

- klar

- ekte

- eiendomsmegling

- Reality

- virkelig

- grunnen til

- nylig

- gjenkjent

- reflektere

- Refleksjoner

- registre

- relativt

- relevant

- pålitelighet

- reparasjon

- repeterbar

- rapporterer

- krever

- påkrevd

- Krav

- spenstig

- svar

- svar

- ansvar

- ansvarlig

- REST

- ikke sant

- robusthet

- Rolle

- Regel

- regler

- Sa

- salg

- sier

- sier

- sier

- Skala

- skalering

- skanne

- ordninger

- Skole

- Skjerm

- se

- sett

- segmentet

- selger

- Å Sell

- halvledere

- senior

- sensorer

- tjeneste

- sett

- flere

- Hylle

- skift

- bør

- vist

- side

- Signal

- signaler

- signifikant

- betydelig

- Silicon

- lignende

- enkelt

- SIX

- Seks måneder

- Størrelse

- størrelser

- ferdigheter

- bremse

- liten

- mindre

- smarttelefon

- So

- Software

- Solutions

- LØSE

- løse

- noen

- noe

- kilde

- Kilder

- Rom

- høyttalere

- spesiell

- specs

- spekulativ

- fart

- bruke

- Klemme

- stable

- Standard

- standarder

- startet

- Steps

- Still

- oppbevare

- suksess

- vellykket

- slik

- saksøke

- leverandører

- støtte

- Symposium

- system

- Systemer

- Ta

- tar

- Snakk

- snakker

- rettet mot

- teknikker

- Technologies

- vilkår

- test

- Testing

- enn

- Det

- De

- deres

- Dem

- seg

- deretter

- teori

- Der.

- termisk

- Disse

- de

- ting

- ting

- tenker

- denne

- De

- selv om?

- Gjennom

- tid

- til

- i dag

- sammen

- mot

- spore

- Kurs

- overføre

- prøve

- prøving og feiling

- tsmc

- typisk

- forstå

- underveis

- Uventet

- unik

- us

- bruke

- brukt

- Verdifull

- verdi

- ulike

- kjøretøy

- leverandør

- leverandører

- Versus

- vertikal

- vertikalt

- veldig

- Vice President

- Se

- vente

- venter

- ønsker

- var

- Waters

- Vei..

- måter

- we

- VI VIL

- gikk

- Hva

- Hva er

- når

- om

- hvilken

- mens

- HVEM

- hele

- hvem sin

- utbredt

- vil

- villig

- trådløs

- med

- innenfor

- Arbeid

- arbeide sammen

- arbeid

- verksted

- verden

- ville

- Feil

- ennå

- du

- Din

- zephyrnet