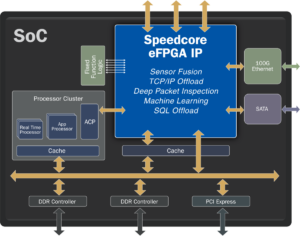

TSMC biedt sinds 1987 gieterijdiensten aan en hun eerste 3nm-knooppunt werd gebeld N3 en debuteerde in 2022; nu hebben ze een verbeterd 3nm-knooppunt genaamd N3E dat is gelanceerd. Elk nieuw knooppunt vereist vervolgens een IP-adres dat zorgvuldig is ontworpen, gekarakteriseerd en gevalideerd in silicium om ervoor te zorgen dat aan de IP-specificaties wordt voldaan en veilig kan worden gebruikt in SoC-ontwerpen. Dit nieuwe IP-adres moet een breed scala aan functies omvatten, zoals interface, geheugen en logica. Synopsys heeft een groot IP-team dat de uitdaging is aangegaan door nieuwe IP te creëren voor het TSMC N3E-knooppunt en first-pass siliciumsucces te behalen.

Chiplet-interconnect

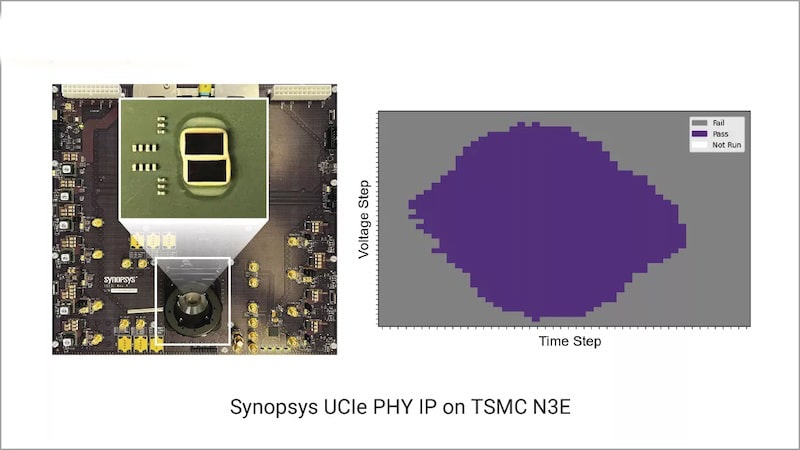

Systemen die uit chiplets bestaan, vereisen 'die-to-die'-communicatie, en dat is waar de UCIe-standaard om de hoek komt kijkeno spelen. Synopsys is een bijdragend lid van de UCIe-consortium, en ze bieden IP voor zowel a UCIe Cbestuurder en een UCIe PHY in het TSMC N3E-knooppunt.

De UCIe PHY IP had de eerste siliciumresultaten in augustus 2023, met datasnelheden van 16 GB/s en schaalbaar tot 24 GB/s per kanaal. De energie-efficiëntie bedraagt 0.3 pJ/bit.

PHY-IP

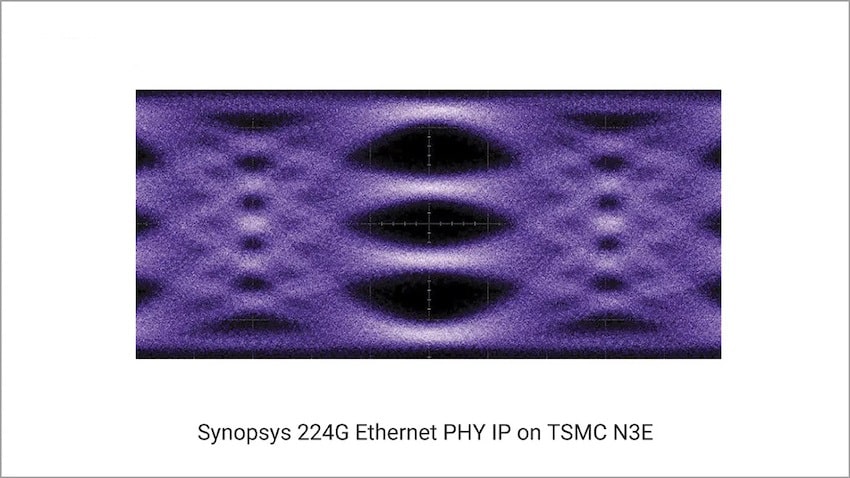

De IEEE heeft de 802.3-standaard voor Ethernet weer goedgekeurd 1983, een behoorlijk uitgebreide standaard, terwijl de Synopsys 224G Ethernet PHY IP het eerste siliciumsucces had in augustus 2023. Netwerkingenieurs kijken naar het oogdiagram om de PAM-4-codering te zien. De jitterniveaus overtroffen zowel de IEEE 802.3- als de OIF-standaardspecificaties.

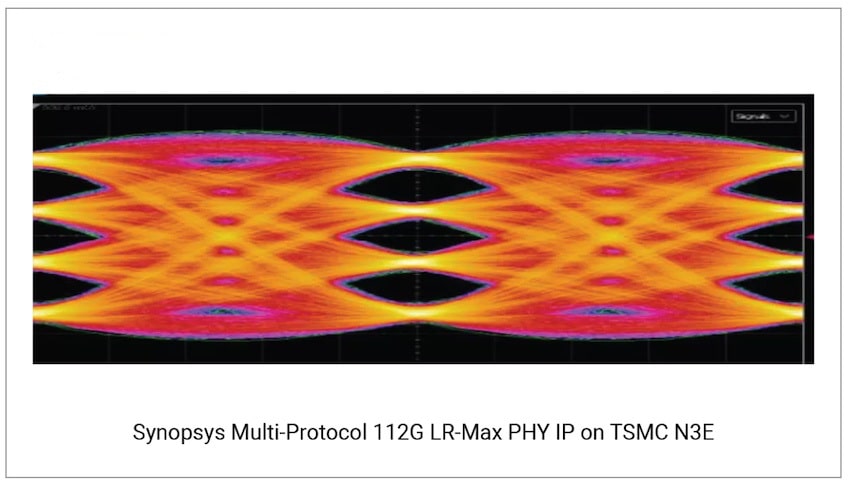

Ter ondersteuning van standaarden zoals PCI Express 6.0, 400G/800G Ethernet, CCIX, CXL2.0/3.0, JESD204 en CPRI is er de Synopsys Multiprotocol 112G PHY IP. Ingenieurs kunnen deze PHY IP combineren met een MAC en PCS om een 200G/400G/800G Ethernet-blok te bouwen.

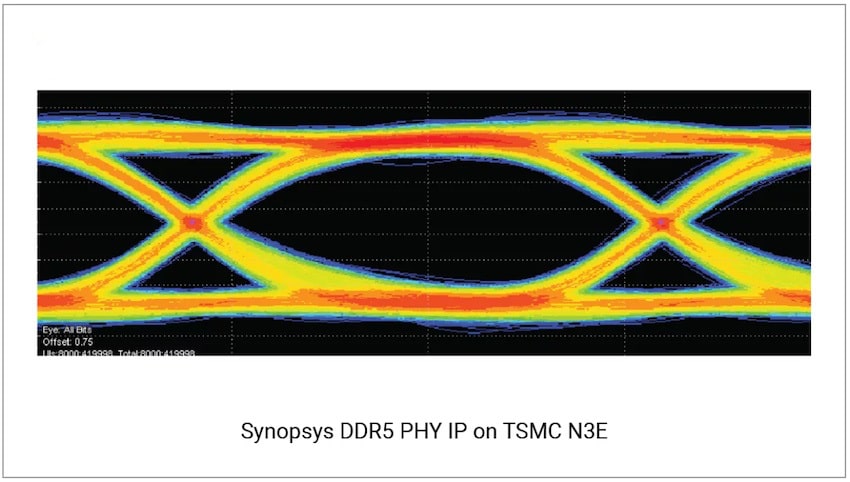

SDRAM en geheugenmodules kunnen de Samenvatting DDR5 PHY IP op TSMC N3E om overdrachtssnelheden tot 8400 Mbps te bereiken. U kunt de wijd open ogen en duidelijke marges zien voor dit IP-adres dat snel werkt.

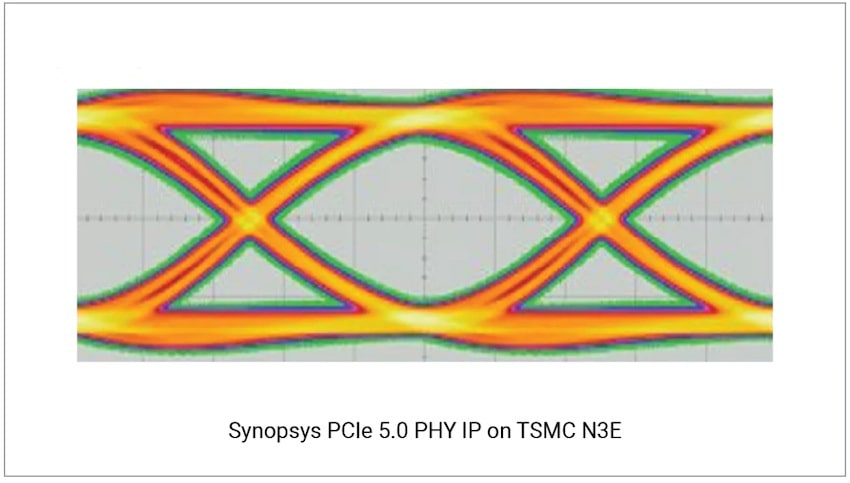

De PCI Express-standaard begon in 2003 en wordt voortdurend bijgewerkt om te voldoen aan de groeiende eisen van cloud computing, opslag en AI. PCIe 5.0 wordt nu ondersteund met behulp van de Synopsys PCIe 5.0 PHY IP. Eerste silicium op TSMC N3E vertoonde bedrijfssnelheden van 32 GT / s, en het heeft de nalevingstests doorstaan.

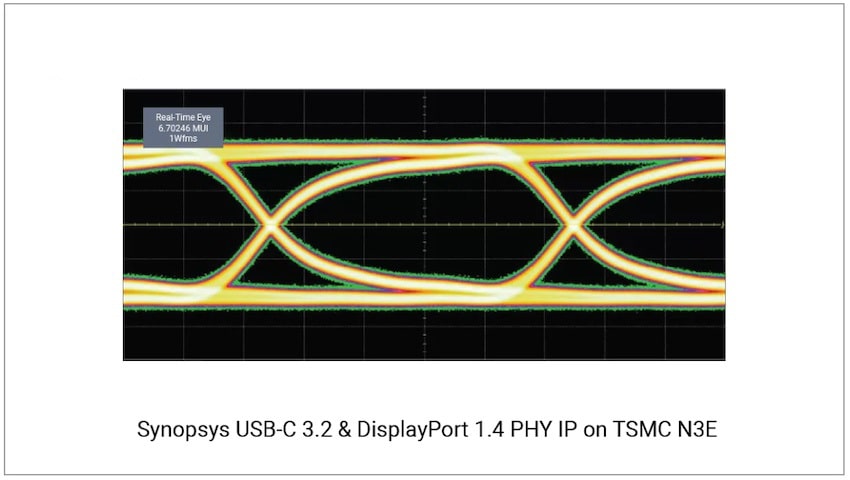

Ik gebruik al jaren USB-C op mijn MacBook Pro, iPad Pro en Android-telefoon. Synopsys ondersteunt nu USB-C 3.2 en DisplayPort 1.4 PHY IP in het nieuwste TSMC-proces. Met dit IP-adres kunnen gebruikers maximaal 8K Ultra High Definition-schermen aansluiten.

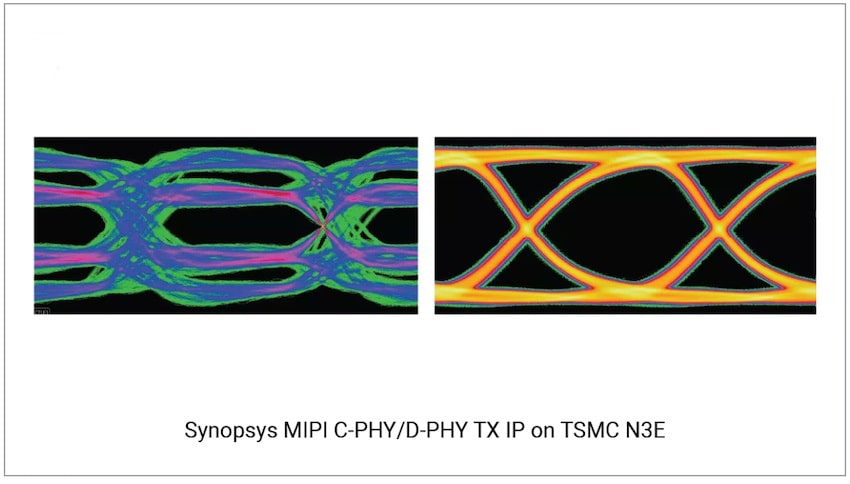

Smartphonebedrijven hebben jaren geleden het MIPI-protocol gestandaardiseerd als een efficiënte manier om camera's aan te sluiten Synopsys MIPI C-PHY IP/D-PHY IP kan werken met 6.5 Gb/s per baan en 6.5 Gs/s per trio. De C-PHY IP ondersteunt v2.0 en de D-PHY IP2.1.

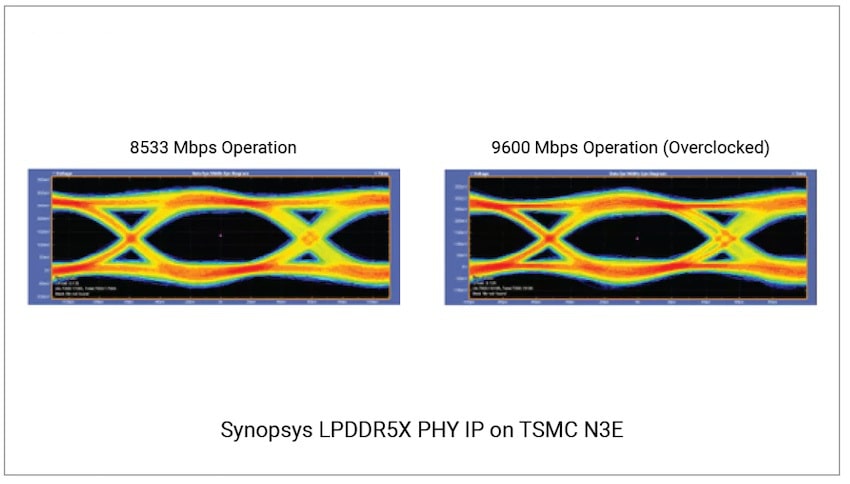

De nieuwste synchrone DRAM-controllerspecificatie is LPDDR5X, die gegevensoverdrachtsnelheden tot 8533 Mbps ondersteunt, een verbetering van 33% ten opzichte van LPDDR5-geheugen. De Synopsys LPDDR5X/5/4X-controller is op silicium bewezen en klaar om mee te ontwerpen.

Logicabibliotheken en herinneringen

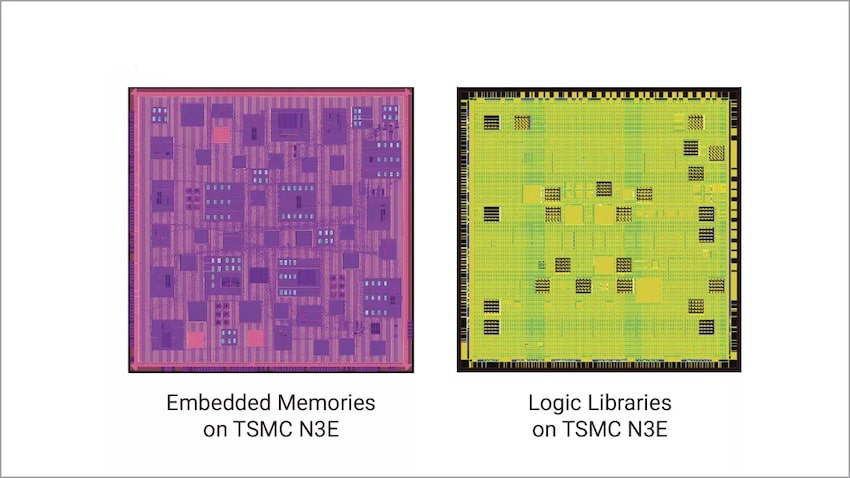

Tot de helft van de oppervlakte van een SoC kan uit herinneringen bestaan, dus het goede nieuws is dat de Stichting Synopsys IP Hiermee kunt u snel geheugens en logicabibliotheekcellen toevoegen aan een nieuw ontwerp. Hier zijn de testchipdiagrammen van Synopsys op het TSMC N3E-knooppunt voor geheugens en logische bibliotheken.

Samengevat

TSMC en Synopsys hebben door de jaren heen behoorlijk goed samengewerkt, en dat partnerschap strekt zich nu uit tot het N3E-knooppunt waar SoC-ontwerpers op silicium geteste IP kunnen vinden voor interfaces, geheugens en logica. Vermogen, prestaties en rendement zien er aantrekkelijk uit voor N3E, dus de technologie is klaar voor uw meest veeleisende ontwerpen. Het starten van een ontwerp met N3E biedt u ook een sneller pad om naar het N3P-proces te migreren.

In plaats van al uw eigen IP helemaal opnieuw te creëren, waardoor uw planning langer wordt, meer technische middelen nodig zijn en de risico's toenemen, kunt u eens kijken naar wat Synopsys te bieden heeft in een breed scala aan IP-blokken die zich op silicium hebben bewezen.

Gerelateerde blogs

Deel dit bericht via:

- Door SEO aangedreven content en PR-distributie. Word vandaag nog versterkt.

- PlatoData.Network Verticale generatieve AI. Versterk jezelf. Toegang hier.

- PlatoAiStream. Web3-intelligentie. Kennis versterkt. Toegang hier.

- PlatoESG. carbon, CleanTech, Energie, Milieu, Zonne, Afvalbeheer. Toegang hier.

- Plato Gezondheid. Intelligentie op het gebied van biotech en klinische proeven. Toegang hier.

- Bron: https://semiwiki.com/ip/336595-tsmc-n3e-is-ready-for-designs-thanks-to-ip-from-synopsys/

- : heeft

- :is

- :niet

- :waar

- $UP

- 1

- 2022

- 2023

- 8k

- a

- Bereiken

- het bereiken van

- toevoegen

- geleden

- AI

- Alles

- toestaat

- ook

- an

- en

- android

- goedgekeurd

- ZIJN

- GEBIED

- AS

- At

- aantrekkelijk

- Augustus

- terug

- BE

- geweest

- wezen

- Blok

- Blokken

- zowel

- bouw

- by

- Dit betekent dat we onszelf en onze geliefden praktisch vergiftigen.

- camera's

- CAN

- voorzichtig

- Cellen

- uitdagen

- Kanaal

- gekarakteriseerde

- spaander

- duidelijk

- Cloud

- cloud computing

- samengewerkt

- combineren

- komt

- Communicatie

- Bedrijven

- nakoming

- computergebruik

- Verbinden

- permanent

- inzender

- controleur

- deksel

- Wij creëren

- gegevens

- debuteerde

- definitie

- veeleisende

- eisen

- Design

- ontworpen

- ontwerpers

- ontwerpen

- diagrammen

- displays

- nagesynchroniseerde

- doeltreffendheid

- doeltreffend

- Engineering

- Ingenieurs

- verbeterde

- verzekeren

- Alle

- uitdrukkelijk

- strekt

- oog

- VIND DE PLEK DIE PERFECT VOOR JOU IS

- Voornaam*

- Voor

- Foundation

- Gieterij

- oppompen van

- functies

- goed

- Groeiend

- HAD

- Helft

- Hebben

- hier

- Hoge

- HTML

- HTTPS

- IEEE

- verbetering

- in

- Laat uw omzet

- Interface

- interfaces

- in

- IP

- iPad

- IT

- jpg

- Rijstrook

- Groot

- laatste

- gelanceerd

- niveaus

- bibliotheken

- Bibliotheek

- als

- logica

- Kijk

- op zoek

- Mac

- macbook

- gemaakt

- marges

- max-width

- Maak kennis met

- lid

- Memories

- Geheugen

- voldaan

- trekken

- Min

- Modules

- meer

- meest

- Dan moet je

- my

- netwerk

- New

- nieuws

- knooppunt

- nu

- of

- bieden

- het aanbieden van

- on

- open

- besturen

- werkzaam

- uit

- over

- het te bezitten.

- Samenwerking

- voorbij

- pad

- PCs

- voor

- prestatie

- phone

- PHP

- Plato

- Plato gegevensintelligentie

- PlatoData

- Spelen

- Post

- energie

- Pro

- protocol

- biedt

- sneller

- snel

- heel

- reeks

- Tarieven

- klaar

- vereisen

- vereist

- Resources

- Resultaten

- Risen

- Risico

- veilig

- schaalbare

- rooster

- krassen

- zien

- Diensten

- vertoonde

- tonen

- Silicium

- sinds

- So

- specificaties

- snelheid

- snelheden

- standaard

- normen

- gestart

- Start

- mediaopslag

- succes

- Ondersteuning

- steunen

- overtroffen

- Nemen

- team

- Technologie

- proef

- Testen

- bedankt

- dat

- De

- De omgeving

- hun

- harte

- Er.

- ze

- dit

- naar

- samen

- overdracht

- trio

- TSMC

- Ultra

- bijgewerkt

- usb

- USB-C

- .

- gebruikt

- gebruikers

- gebruik

- gevalideerd

- via

- was

- Manier..

- GOED

- Wat

- welke

- en

- Waarom

- breed

- Grote range

- wil

- Met

- jaar

- Opbrengst

- u

- Your

- zephyrnet