Chiplets hebben één ontwerpgebied vereenvoudigd, maar op een ander front de doos van Pandora geopend. De simulatiecomplexiteit van elk chipje is lager, maar nu is de chiplet-naar-chiplet-verbinding complex geworden. Mensen experimenteren met verschillende verbindingsprotocollen, variaties op UCIe, het wijzigen van UCIe-instellingen, interfacesnelheden, aantal fysieke lagen, enzovoort. Voeg nu oudere standaarden zoals AXI, nieuwe protocollen zoals PICe6.0 en cache-coherentie toe aan de mix.

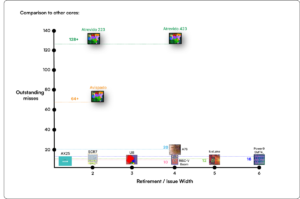

Al met al ontstaat hierdoor een compleet nieuwe reeks experimenten. Eén waarvoor de traditionele emulatie en RTL-modellering niet zullen werken. U moet eerst aandacht besteden aan de afweging tussen architectuur en niet alleen aan het selecteren van componenten. Dit betekent dat u verkeersanalyses, applicatiepartitionering, systeemgrootte en impact van verschillende soorten fysieke lagen moet uitvoeren. Bovendien zal de benchmark, afhankelijk van de toepassing, heel anders zijn.

De UCIe-specificatie is nieuw en er zijn geen duidelijke benchmarks. Bovendien biedt de UCIe-specificatie alleen richtlijnen voor latentie en vermogen. Beide zijn strenge eisen. Dit betekent dat een Power-Performance-Area-onderzoek onvermijdelijk is. Omdat u protocol-protocol-protocol-conversie hebt, zoals PCIe 6.0 naar UCIe naar AXI, is de modelleringsconfiguratie complex.

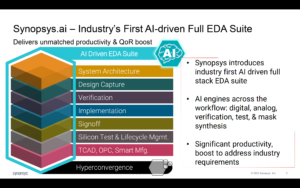

Eén oplossing is om naar systeemmodellering te kijken met behulp van Visuele Sim oppompen van mirabilis Ontwerp. Ze hebben onlangs een IP-model op UCIe-systeemniveau gelanceerd en zullen een aantal gebruiksscenario's van de interconnect demonstreren op de Chiplet-top. Om ontwerpers op weg te helpen, hebben ze een gids gepubliceerd met veel gebruiksscenario's, verwachte resultaten op het gebied van energieprestaties en opties voor optimalisatie. Ze hebben zowel een paperpresentatie als een stand op de Summit. Ik hoop dat ik je daar zie!

Hier is ook de link voor een artikel dat mensen kunnen krijgen: Prestatiemodellering van een heterogeen computersysteem gebaseerd op de UCIe Interconnect Architecture

Abstract:

De huidige complexe chipontwerpen op geavanceerde knooppunten bestaan doorgaans uit meerdere dies (of chiplets). De aanpak maakt matrijzen van verschillende fabrikanten of processen mogelijk, evenals herbruikbare IP. Ontwerpers hebben een model op systeemniveau nodig om verschillende implementaties van dergelijke complexe situaties te evalueren.

Een voorbeeldsysteem bestaat uit een I/O-chiplet, kernchiplet met laag vermogen, krachtige kernchiplet, audio-video-chiplet en analoge chiplet, onderling verbonden via de Universal Chiplet Interconnect Express (UCIe)-standaard.

Ons team heeft verschillende scenario's en configuraties overwogen, waaronder geavanceerde en standaardpakketten, gevarieerde verkeersprofielen en bronnen, en een retimer om het bereik te vergroten en gebeurtenissen op time-out te evalueren. Door de sterke en zwakke punten van de UCIe-interconnect voor missietoepassingen te identificeren, konden we voor elk subsysteem de optimale configuratie verkrijgen om te voldoen aan de prestatie-, kracht- en functionele vereisten.

Over Mirabilis Design Inc.

Mirabilis Design is een softwarebedrijf uit Silicon Valley dat software- en trainingsoplossingen levert om risico's in de productspecificaties te identificeren en te elimineren, nauwkeurig de menselijke en tijdbronnen te voorspellen die nodig zijn om het product te ontwikkelen, en de communicatie tussen diverse ingenieurs te verbeteren.

teams.

VisualSim Architect combineert intellectueel eigendom, modellering op systeemniveau, simulatie, omgevingsanalyse en applicatiesjablonen om de modelconstructie, simulatie, analyse en RTL-verificatie aanzienlijk te verbeteren. De omgeving stelt ontwerpers in staat snel te convergeren naar een ontwerp dat voldoet aan een gevarieerde reeks onderling afhankelijke tijd- en stroomvereisten. Het wordt al heel vroeg in het ontwerpproces gebruikt, parallel met (en als hulpmiddel bij) de schriftelijke specificatie en vóór een implementatie (bijvoorbeeld RTL, softwarecode of schema) van het product.

Lees ook:

WEBINAR: Hoe u meer dan 95% nauwkeurige vermogensmeting kunt bereiken tijdens architectuurverkenning

SysML toewijzen aan hardware-architectuur

Modelgebaseerde ontwerpcursussen voor studenten

Deel dit bericht via:

- Door SEO aangedreven content en PR-distributie. Word vandaag nog versterkt.

- PlatoData.Network Verticale generatieve AI. Versterk jezelf. Toegang hier.

- PlatoAiStream. Web3-intelligentie. Kennis versterkt. Toegang hier.

- PlatoESG. carbon, CleanTech, Energie, Milieu, Zonne, Afvalbeheer. Toegang hier.

- Plato Gezondheid. Intelligentie op het gebied van biotech en klinische proeven. Toegang hier.

- Bron: https://semiwiki.com/ip/mirabilis-design-ip/341339-chiplets-open-pandoras-box/

- : heeft

- :is

- :niet

- a

- accuraat

- nauwkeurig

- Bereiken

- toevoegen

- vergevorderd

- Steun

- toestaat

- langs

- ook

- an

- analyse

- en

- Nog een

- Aanvraag

- toepassingen

- nadering

- architectuur

- ZIJN

- GEBIED

- AS

- At

- gebaseerde

- BE

- worden

- vaardigheden

- criterium

- benchmarks

- tussen

- zowel

- Box camera's

- maar

- cache

- CAN

- Kan krijgen

- gevallen

- spaander

- duidelijk

- code

- combines

- Communicatie

- afstand

- compleet

- complex

- ingewikkeldheid

- componenten

- computergebruik

- Gedrag

- Configuratie

- beschouwd

- bestaat uit

- bouw

- convergeren

- Camper ombouw

- Kern

- cursussen

- creëert

- demonstrating

- Afhankelijk

- Design

- ontwerpproces

- ontwerpers

- ontwerpen

- ontwikkelen

- anders

- diversen

- gedurende

- elk

- Vroeg

- inspanning

- elimineren

- wedijver

- maakt

- Milieu

- schatten

- EVENTS

- voorbeeld

- verwacht

- experimenteren

- experimenten

- uitdrukkelijk

- verlengen

- Voornaam*

- Voor

- oppompen van

- voor

- functioneel

- algemeen

- krijgen

- Kopen Google Reviews

- leiding

- gids

- Hardware

- Hebben

- geholpen

- hier

- hoge performantie

- hoop

- Hoe

- How To

- HTTPS

- menselijk

- i

- identificeren

- het identificeren van

- Impact

- uitvoering

- implementaties

- verbeteren

- in

- Inclusief

- intellectueel

- intellectueel eigendom

- met elkaar verbonden

- Interface

- IP

- IT

- jpg

- voor slechts

- Wachttijd

- gelanceerd

- lagen

- Legkippen

- Nalatenschap

- Niveau

- als

- LINK

- Kijk

- veel

- Laag

- te verlagen

- Fabrikanten

- max-width

- gemiddelde

- middel

- maat

- Maak kennis met

- Meets

- Missie

- mengen

- model

- modellering

- modellering

- meervoudig

- Noodzaak

- New

- geen

- knooppunten

- nu

- aantal

- verkrijgen

- of

- on

- EEN

- Slechts

- open

- geopend

- optimale

- optimalisatie

- Opties

- or

- Paketten

- Papier

- Parallel

- prestatie

- Fysiek

- Plato

- Plato gegevensintelligentie

- PlatoData

- Post

- energie

- het voorspellen van

- presentatie

- processen

- Product

- Profielen

- eigendom

- protocollen

- biedt

- het verstrekken van

- gepubliceerde

- snel

- bereiken

- Lees

- onlangs

- nodig

- Voorwaarden

- Resources

- Resultaten

- herbruikbare

- Risico

- scenario's

- zien

- selecteren

- reeks

- settings

- setup

- verscheidene

- aanzienlijk

- Silicium

- Silicon Valley

- vereenvoudigd

- simulatie

- situaties

- So

- Software

- oplossing

- Oplossingen

- specificatie

- snelheden

- besteden

- standaard

- normen

- sterke punten

- streng

- Studie

- dergelijk

- Top

- system

- team

- templates

- dat

- De

- Er.

- ze

- dit

- niet de tijd of

- naar

- traditioneel

- verkeer

- Trainingen

- types

- Universeel

- us

- .

- gebruikt

- gebruik

- Vallei

- variaties

- Verificatie

- zeer

- via

- zwakke punten

- GOED

- welke

- wil

- Met

- Mijn werk

- geschreven

- u

- zephyrnet