SPIE Advanced Lithography Conference가 XNUMX월에 개최되었습니다. 나는 최근에 imec의 첨단 패터닝 공정 및 재료 담당 부사장인 Steven Scheer를 인터뷰하고 imec이 발표한 선별된 논문을 검토할 기회를 가졌습니다.

저는 Steve에게 올해 SPIE에서 가장 중요한 메시지가 무엇인지 물었습니다. 그는 High NA에 대한 준비가 핵심이라고 말했습니다. 그는 세 가지 주요 생태계 영역을 확인했습니다.

- 마스크 및 해상도 향상 기술(RET) 인프라.

- 재료, 포토레지스트 및 하층.

- 도량형

물론 노출 도구도 핵심이지만 Steve가 이야기하는 것은 아닙니다. 작성자 참고 사항 – ASML의 SPIE 프레젠테이션에 대한 글도 작성할 예정입니다.

마스크

Steve는 계속해서 마스크 관련 문제를 나열했습니다.

- 초점 이동 및 대비 손실과 같은 마스크 3D 효과 – 높은 NA는 3D 효과를 더 문제로 만드는 낮은 각도 노출입니다.

- 저결함 마스크 블랭크 및 조도 및 CD 변동이 적은 마스크

- 더 높은 콘트라스트를 활성화하고 마스크 3D 효과를 줄이려면 저 n 마스크가 필요합니다.

- 광학적 근접성 보정 기술.

- 마스크 쓰기, 멀티빔.

- 마스크 스티칭 – 스캐너 필드의 작은 크기는 다이를 함께 스티칭해야 합니다.

- 4x 한 방향, 8x 다른 방향은 스티칭을 가능하게 하는 새로운 유형의 마스크 디자인이 필요합니다.

- 더 높은 소스 에너지를 위한 펠리클.

In “CNT 펠리클: 최근 최적화 및 노출 결과,” Joost Bekaert 등은 탄소 나노튜브 펠리클(CNT)을 탐구했습니다.

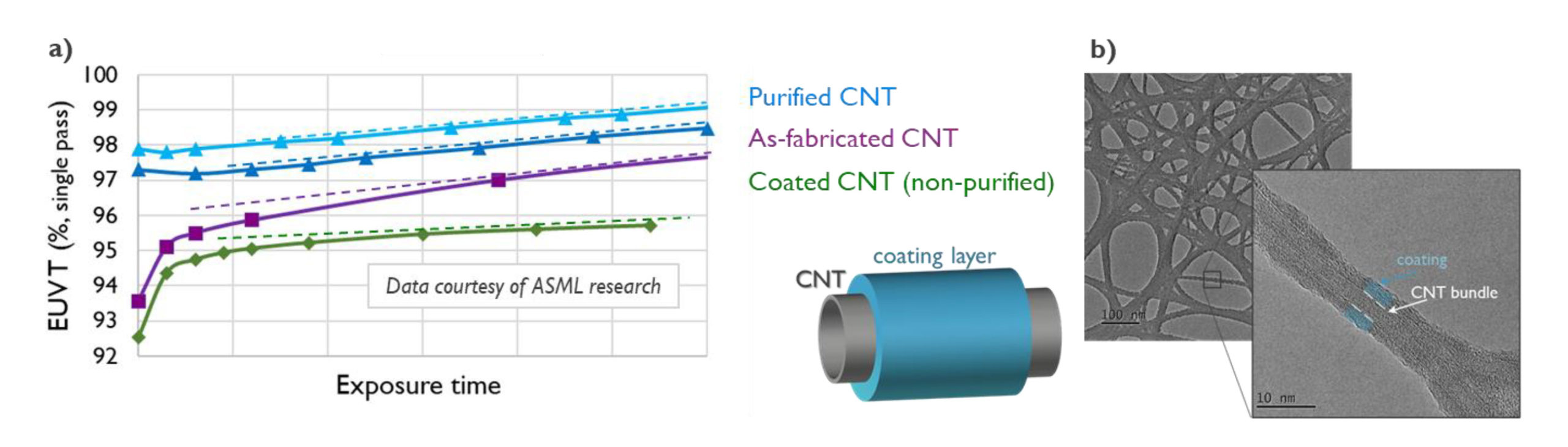

ASML은 로드맵에 600와트 소스 시스템을 보유하고 있으며 금속 실리사이드를 기반으로 하는 현재 펠리클은 최대 약 400와트까지만 실행 가능합니다. 펠리클은 입자 차단, 높은 투과율, 약 110mm x 140mm 영역에 매달릴 수 있는 충분한 기계적 강도, 내구성이 있어야 합니다. CNT는 98%의 투과율을 보였다. EUV 방사선은 매우 에너지가 넘치므로 펠리클을 에칭하는 수소 플라즈마를 생성하여 궁극적으로 펠리클의 기계적 무결성 손실을 초래합니다. imec은 식각 속도와 펠리클을 안정화하는 방법을 평가해 왔습니다.

에칭율은 투과율을 보면 평가할 수 있는데, 펠리클이 에칭에 의해 얇아지면 투과율이 증가하기 때문입니다. 그림 1은 다양한 조건에서 Pellicle의 시간 경과에 따른 전송을 보여줍니다.

ASML은 오프라인 플라즈마 노출 도구를 사용하여 펠리클 전송 대 노출 시간을 평가하고 이 작업에서 imec은 최대 3,000개 웨이퍼(웨이퍼당 96mJ/cm²에서 30개 다이)까지 CNT 펠리클 노출을 시연했으며 실제 스캐너 노출에서 얻은 결과 간의 상관 관계를 보여주었습니다. 오프라인 도구에서 가져온 것입니다.

펠리클은 초기에 EUV 에너지를 흡수하여 소진될 때까지 제조 공정에서 발생하는 휘발성 유기 불순물을 가지고 있습니다. 녹색 및 보라색 곡선을 참조하십시오. 고온에서 펠리클을 굽는 것은 오염 물질을 태워 펠리클을 "정화"하여 식각률이 지배적인 투과율 변화를 초래합니다. 두 개의 파란색 곡선의 기울기는 식각률 때문입니다. 녹색 곡선은 더 낮은 에칭 속도를 나타내는 "코팅된" 펠리클을 나타내지만 코팅은 전송을 감소시키고 매우 높은 전력 수준과 호환되지 않을 수 있습니다.

포토 레지스트

그런 다음 Steve는 포토레지스트에 대해 논의했습니다.

포토레지스트의 경우 24nm ~ 20nm 피치는 16nm 피치가 궁극적인 해상도인 높은 NA 삽입을 위한 스위트 스팟입니다. CAR(Chemically Amplified Resist)는 24nm 이하에서 성능이 좋지 않습니다. MOR(Metal Oxide Resist)은 17nm 또는 16nm까지 유망해 보입니다. 결함은 여전히 문제입니다. 24nm 피치에 대한 선량은 67mJ/cm2 MOR 및 77mJ/cm2 자동차용. MOR에는 몇 가지 안정성 문제가 있으며 도즈가 낮을수록 레지스트의 반응성이 높거나 덜 안정적입니다. 이것들은 쇼스토퍼가 아니라 도전입니다.

In "극자외선 리소그래피를 위한 축소된 증착 밑층" Gupta 등은 포토레지스트 하층을 탐구했습니다. 피치가 줄어들면 동일한 포토레지스트 층에 대해 종횡비가 증가하고 패턴 붕괴로 이어질 수 있습니다. 개선된 하층 접착력으로 이 문제를 해결할 수 있습니다. 또는 더 얇은 포토레지스트를 사용하여 종횡비를 관리할 수 있지만 이는 레이어 아래에서 높은 식각 선택성이 발견되지 않는 한 식각 문제를 유발할 수 있습니다.

imec은 증착된 하부층의 표면 에너지가 개선된 접착력을 달성하기 위해 포토레지스트와 일치될 수 있음을 발견했습니다. 증착된 하부층의 밀도 조정은 개선된 에칭 선택도를 제공하기 위해 이용될 수 있다.

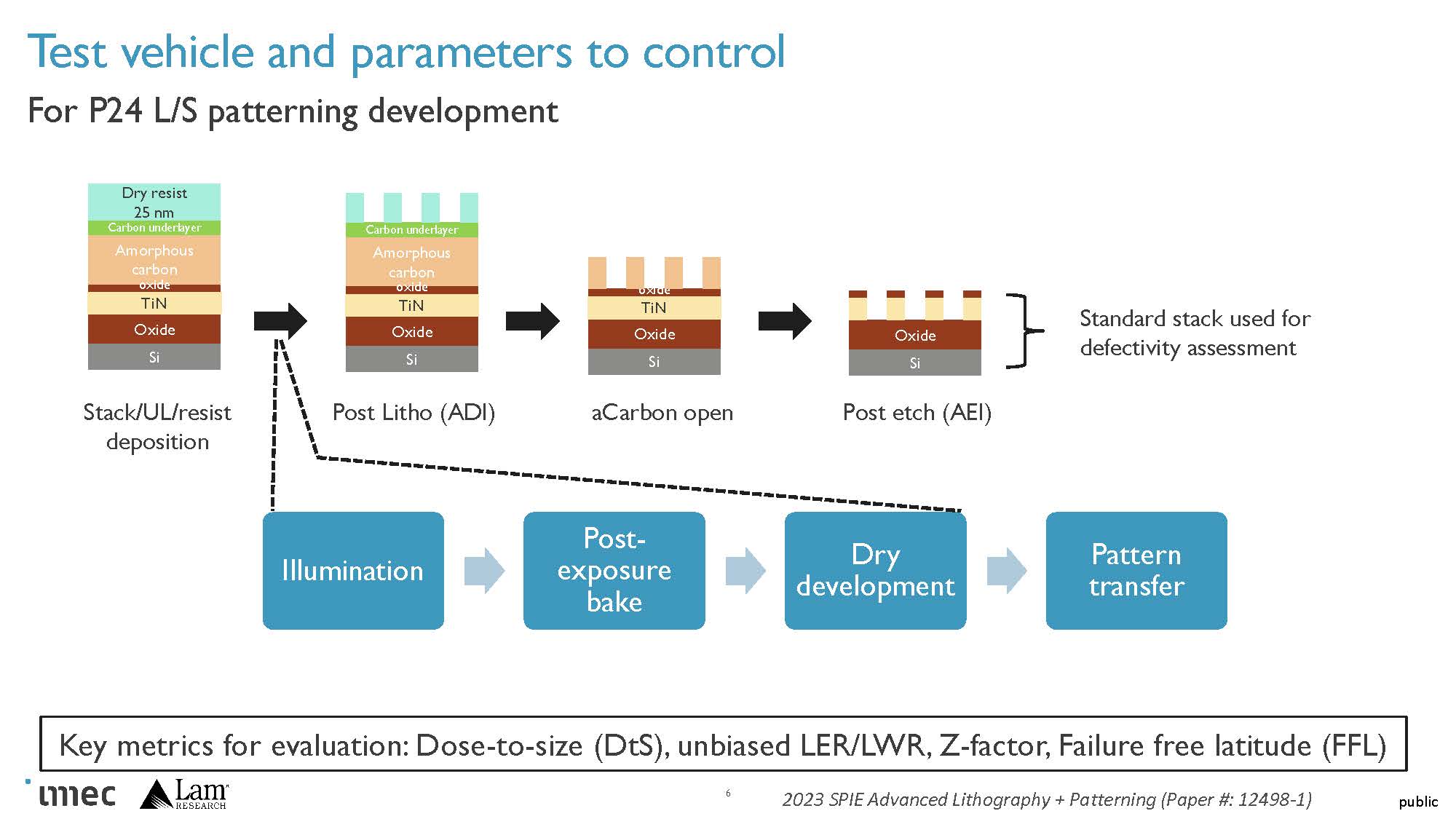

In "높은 NA EUV 리소그래피를 향한 건식 레지스트 패터닝 준비" imec과 Lam의 Hyo Sean Suh 등은 Lam의 건식 포토레지스트 공정을 조사했습니다. N2+ 및 A14 공정의 경우 금속 2 피치(M2P)는 24nm T15T(tip-to-tip)로 ~2nm가 될 것으로 예상되며 A10에서 M2P는 <22nm T15T로 ~2nm가 될 것으로 예상됩니다.

램 드라이 레지스트 프로세스는 그림 2에 설명되어 있습니다.

PEB(Post Exposure Bake)는 선량 감소를 강력하게 유도하는 것으로 밝혀졌지만 브리지와 거칠기에 영향을 미쳤습니다. 공동 최적화 개발 및 식각은 브리지와 거칠기를 완화하고 24nm 피치 L/S 패터닝을 위한 강력한 공정 창을 보여주었습니다.

In “0.55NA EUV 싱글 패터닝으로 로직 메탈 스케일링 실현 가능성” Dongbo Xu et.al. High-NA(0.55NA) 시스템이 단일 패터닝으로 달성할 수 있는 것에 대한 평가를 설명했습니다.

그들은 24nm 피치가 달성 가능해 보인다고 결론지었습니다. 20nm는 수평 방향에서 유망해 보이지만 수직 방향에서는 더 많은 작업이 필요합니다. 18nm 피치는 추가 작업이 필요합니다.

EUV는 선 거칠기 및 확률론적 결함 관점에서 매우 어려운 기술임이 입증되었습니다. DSA(Directed Self Assembly)는 오랫동안 사용되어 왔지만 많은 주목을 받지 못한 기술입니다. DSA는 이제 EUV에 대한 라인 러프니스 및 확률적 결함을 해결하는 기술로 주목받고 있습니다.

In “EUV 리소그래피 선 공간 패턴 정류를 사용한 블록 공중합체 방향 자기 조립: 조도 및 결함 연구,” Julie Van Bel 외. DSA와 EUV를 결합하는 것이 선폭 거칠기가 낮고 전위 결함이 없는 침지 리소그래피 기반 DSA 프로세스보다 우수하다는 것을 발견했습니다.

In "지시적 자기 조립에 의한 EUV 리소그래피의 확률론 완화", Lander Verstraete et.al. EUV 처리에서 확률적 결함을 완화하기 위해 DSA를 사용하여 탐색했습니다.

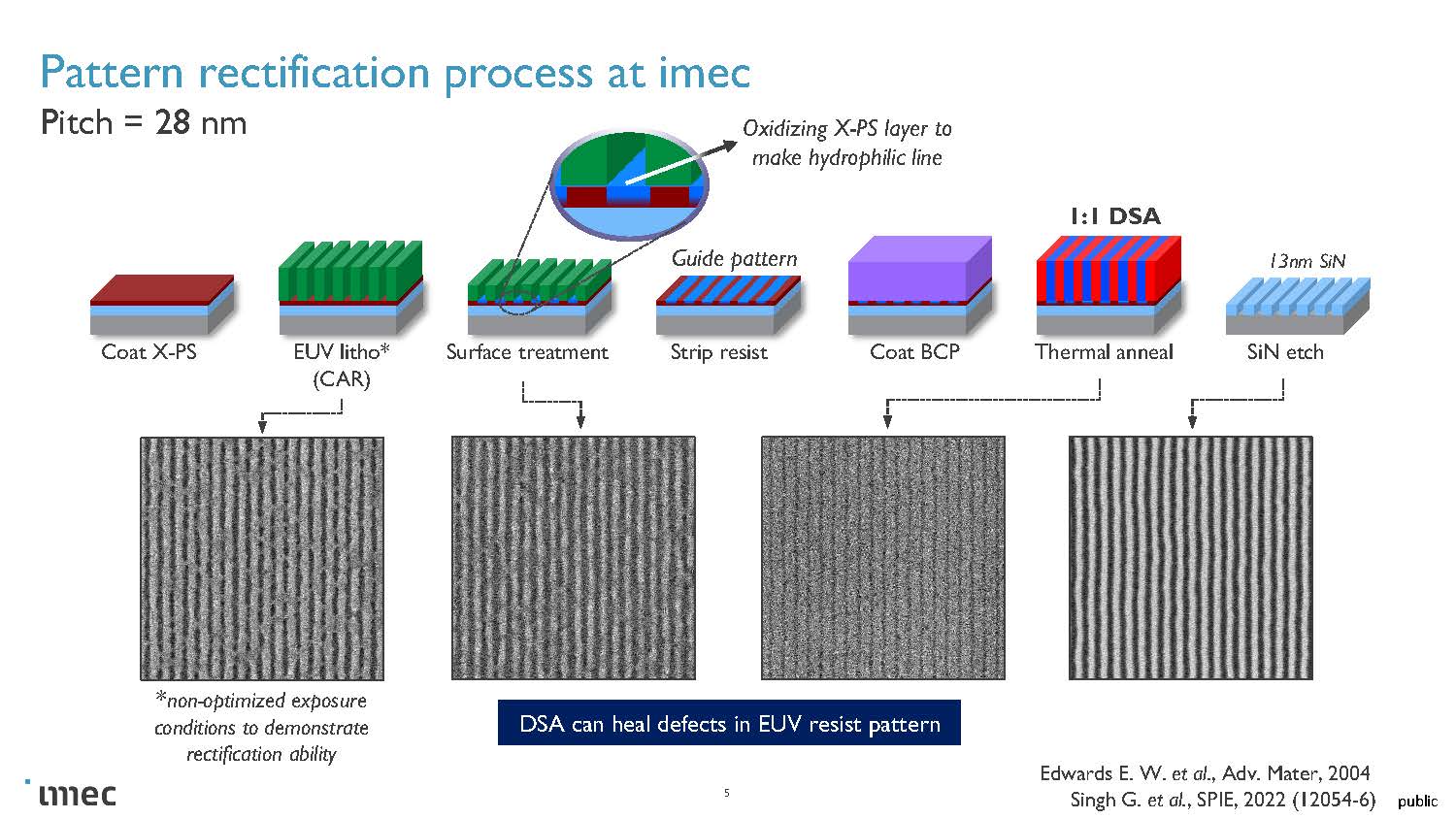

라인/스페이스 EUV 결함을 수정하기 위한 imec 프로세스는 그림 3에 설명되어 있습니다.

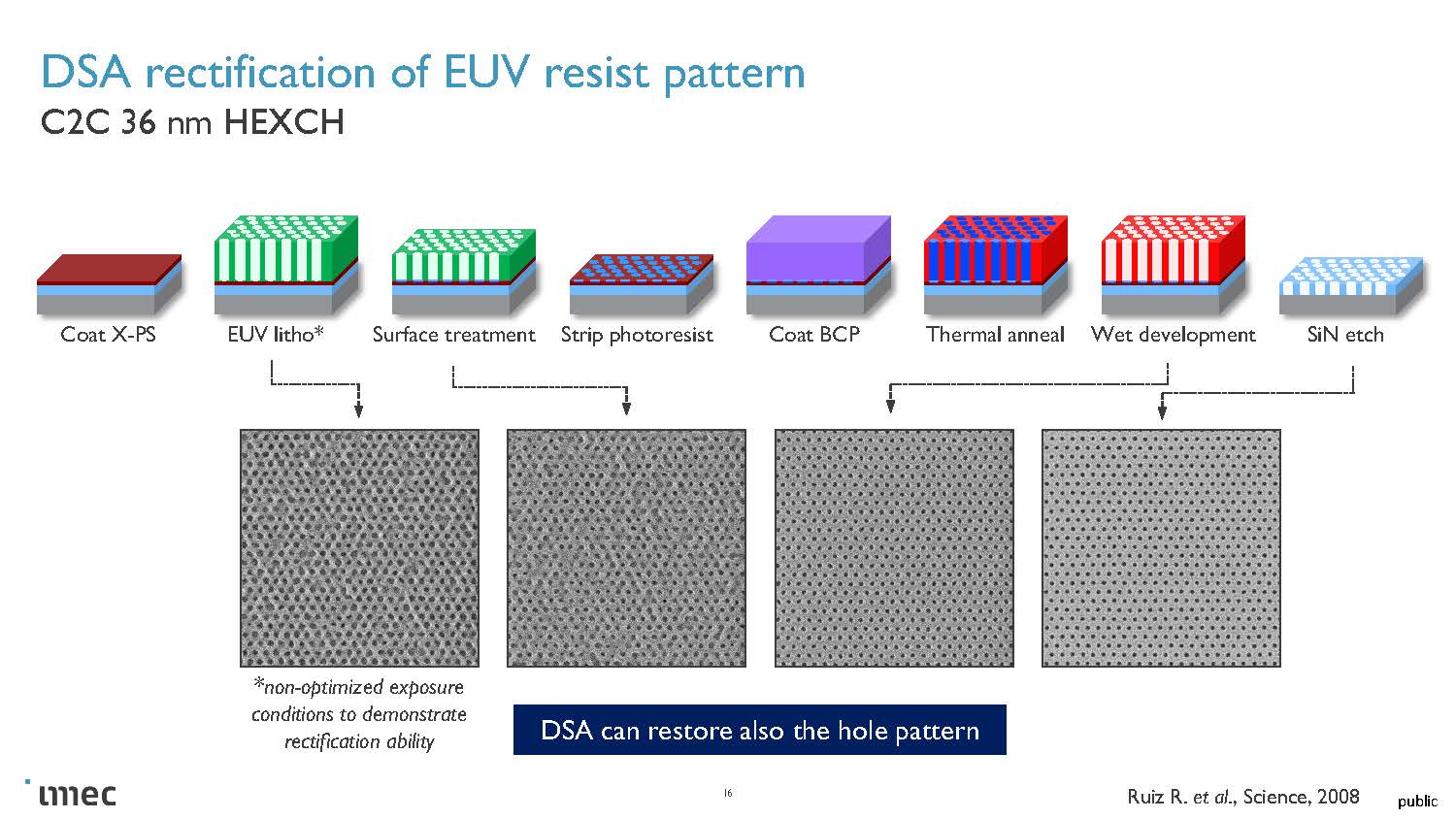

접촉 어레이의 결함을 수정하기 위한 imec 프로세스가 그림 4에 설명되어 있습니다.

EUV와 DSA는 28nm 피치에서 라인/스페이스에 매우 유망해 보이며 주요 결함은 브리지입니다. 24nm 피치에서는 브리지 결함이 너무 많아 개선이 필요합니다. 결함은 블록 공중합체 배합 및 어닐링 시간과 관련이 있습니다.

접점 어레이의 경우 EUV + DSA는 로컬 임계 치수 균일성(LCDU) 및 패턴 배치 오류를 개선하고 더 낮은 선량을 가능하게 합니다.

도량형

필름 두께가 감소함에 따라 계측 신호 대 노이즈 비율이 문제가 됩니다.

EUV는 결함 프로세스 윈도우가 있는데, 한쪽에는 패턴의 단절이 문제가 되는 벼랑이 있고 다른 한쪽에는 패턴 사이의 브리지가 문제가 되는 벼랑이 있습니다.

새로운 피치를 시도할 때 시간이 지남에 따라 많은 결함이 발생합니다.

충분한 감도로 충분히 넓은 영역을 측정하는 것은 어렵습니다. E 빔 검사는 민감하지만 느리고 광학 검사는 빠르지만 민감하지 않습니다. CFET와 같은 새로운 3D 프로세스는 추가적인 문제를 야기합니다.

In "높은 NA EUVL을 위한 건식 레지스트 계측 준비" Gian Francesco Lorusso 등은 매우 얇은 포토레지스트의 특성화를 위해 원자력 현미경(AFM), E 빔 검사 및 CD SEM을 조사합니다.

Lam dry 포토레지스트 공정 사용< CD SEM은 5nm 두께의 포토레지스트까지 실행 가능한 것으로 나타났습니다. 레지스트 두께가 감소함에 따라 선 거칠기가 증가했고, 브릿지 결함의 인쇄성은 감소했지만 절단 결함은 동일하게 유지되었습니다. 패턴 붕괴는 두꺼운 필름에서만 나타났습니다. AFM 측정 결과 필름 두께가 감소하는 것으로 나타났습니다. E Beam은 매우 얇은 필름에서도 결함을 잘 포착했습니다.

In “3D 시대를 위한 반도체 계측” J. Bogdanowicz 등은 3D 구조에 대한 계측의 과제를 탐구합니다.

3D 시대에 Z 방향은 새로운 X/Y 스케일링이 되었습니다. 논리 장치의 경우 CFET 및 Semi damascene이 과제를 제시하고 메모리에서 3D DRAM은 미래의 과제이며 STCO(System Technology Co Optimization)를 위한 3D 상호 연결은 또 다른 과제입니다.

수평 나노시트 및 CFET 공정의 경우 측면 리세스 및 필 특성화와 다층 스택의 잔류물 및 기타 결함 감지가 중요합니다. 3D 메모리에서는 고종횡비(HAR) 홀/스플릿 프로파일링 및 다층 필름의 묻힌 결함 및 잔류물을 감지하는 로직과 유사한 것이 중요합니다. STCO 애플리케이션의 경우 결합 인터페이스 및 정렬의 무결성이 핵심입니다.

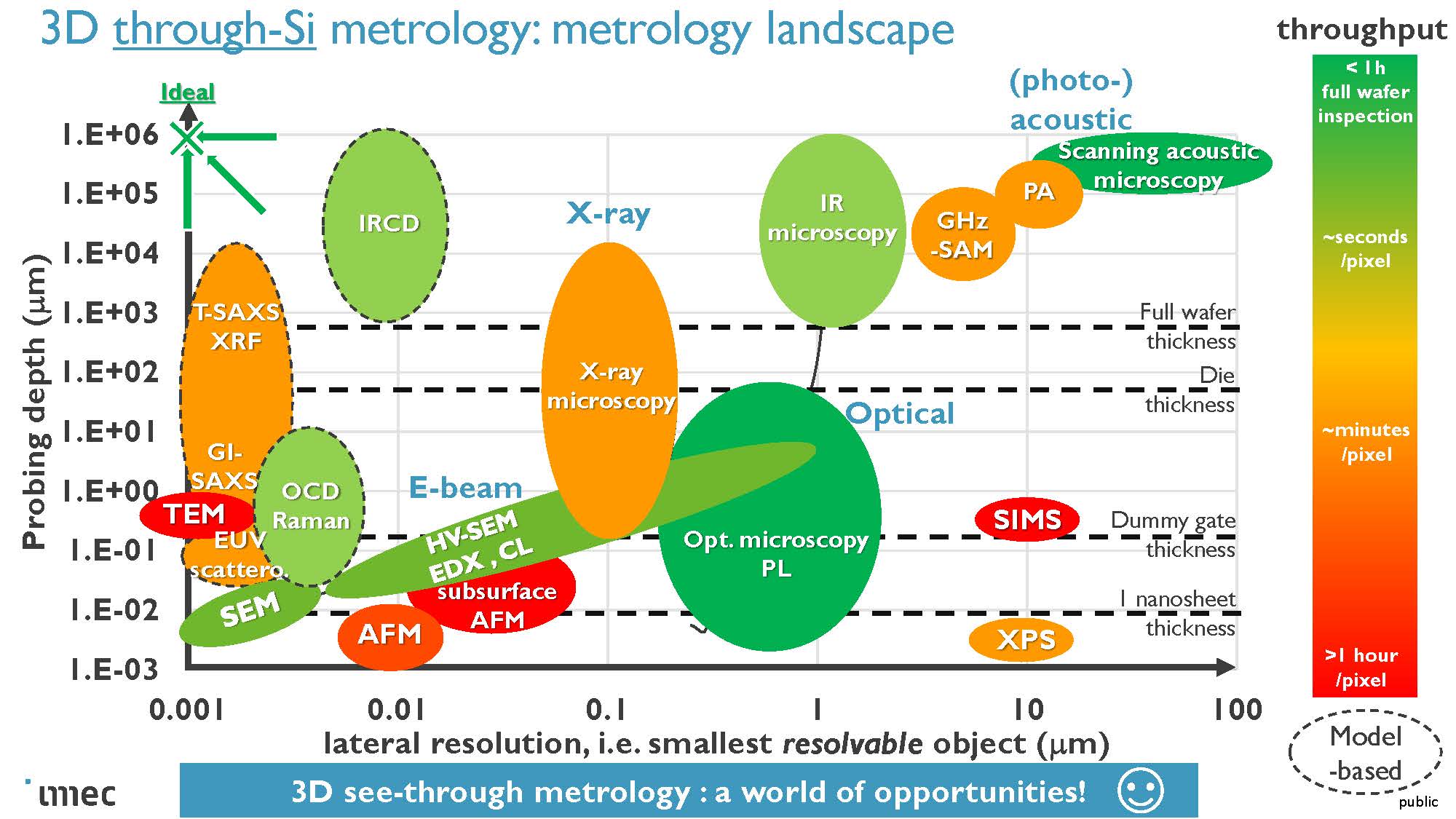

전통적인 표면 계측의 경우 이미 감도와 속도 사이에 트레이드 오프가 있습니다. 이제 검사 깊이 대 측면 해상도가 핵심 트레이드 오프입니다. 그림 5는 다양한 계측 기술에 대한 프로빙 깊이 대 측면 분해능 및 처리량을 나타냅니다.

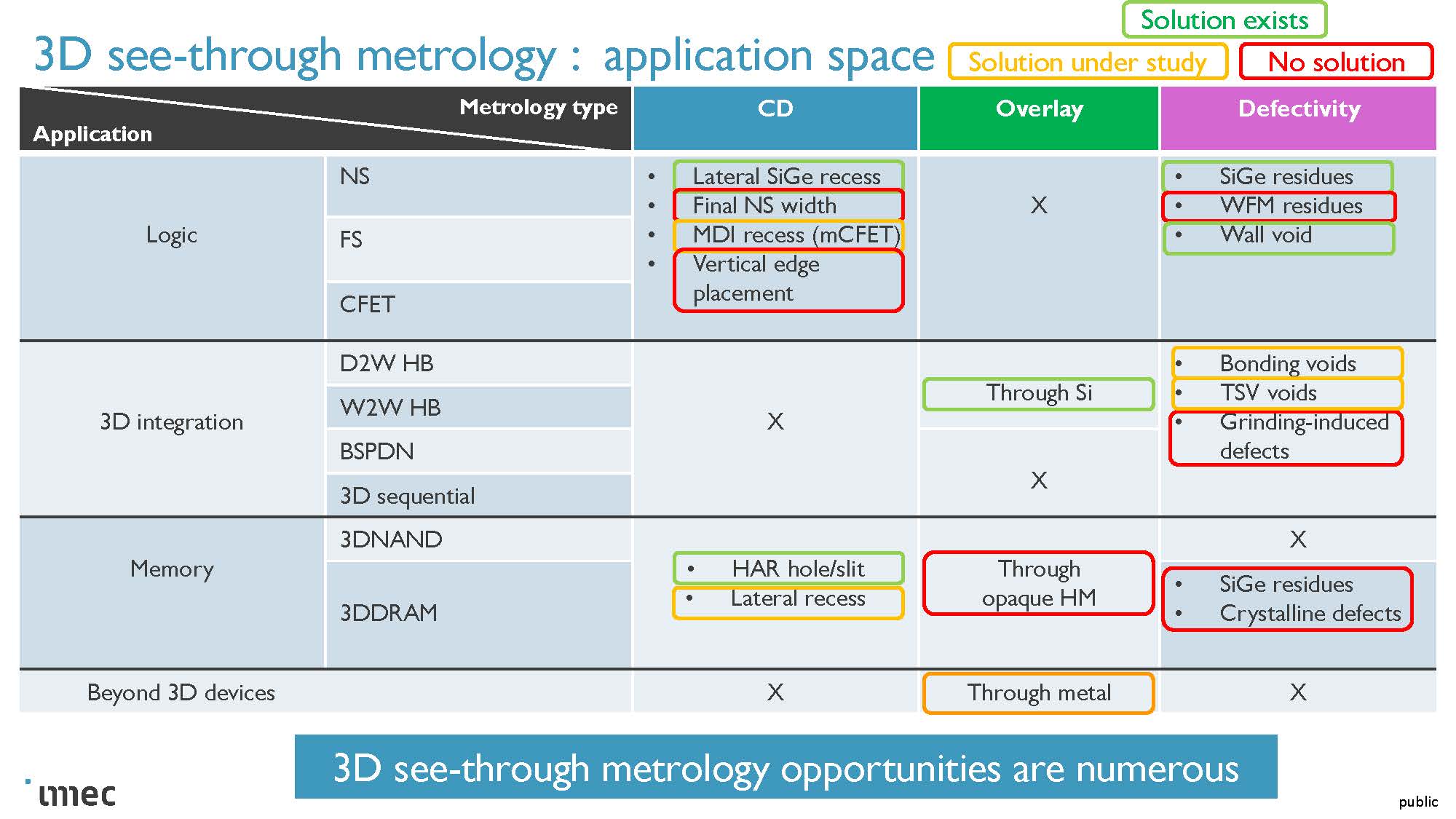

그림 6은 다양한 요구 사항을 해결하기 위한 3D 계측의 현재 준비 상태를 요약한 것입니다.

그림 6에서 포괄적인 계측 프로그램을 달성하기 위해 극복해야 할 과제가 여전히 많이 있습니다.

결론

High NA EUV 시대가 다가오고 있습니다. 펠리클, 포토레지스트, 계측학에서 좋은 발전이 이루어지고 있으며 imec은 추가 발전을 위해 세 가지 영역 모두에서 계속 작업하고 있습니다.

또한 읽기 :

TSMC는 당신이 생각하는 것보다 300mm에 더 많은 돈을 썼습니다

SPIE 고급 리소그래피 컨퍼런스 2023 - AMAT Sculpta® 발표

IEDM 2023 – 2D 재료 – Intel 및 TSMC

다음을 통해이 게시물 공유 :

- SEO 기반 콘텐츠 및 PR 배포. 오늘 증폭하십시오.

- PlatoAiStream. Web3 데이터 인텔리전스. 지식 증폭. 여기에서 액세스하십시오.

- 미래 만들기 w Adryenn Ashley. 여기에서 액세스하십시오.

- PREIPO®로 PRE-IPO 회사의 주식을 사고 팔 수 있습니다. 여기에서 액세스하십시오.

- 출처: https://semiwiki.com/lithography/329278-spie-2023-imec-preparing-for-high-na-euv/

- :있다

- :이다

- :아니

- :어디

- $UP

- 000

- 1

- 2022

- 2023

- 2D

- 2D 재료

- 30

- 3d

- a

- 달성

- 실제

- 추가

- 주소

- 많은

- 고급 리소그래피

- AL

- All

- 이미

- 또한

- 증폭

- an

- 및

- 다른

- 어플리케이션

- 접근하는

- 대략

- 있군요

- 지역

- 지역

- 약

- AS

- 양상

- 조립

- At

- 시도하다

- 주의

- 작성자

- 빵 굽기

- 기반으로

- BE

- 빔

- 가

- 된

- 존재

- 이하

- 사이에

- 블록

- 파란색

- 흩어져

- 휴식

- 다리

- 다리

- 화상

- 비자 면제 프로그램에 해당하는 국가의 시민권을 가지고 있지만

- by

- CAN

- 포착

- 자동차

- 탄소

- CD

- 도전

- 과제

- 도전

- 변경

- CO

- 축소

- 결합

- 호환

- 포괄적 인

- 결론

- 조건

- 컨퍼런스

- CONTACT

- 오염 물질

- 계속

- 대조

- 상관 관계

- 코스

- 생성

- 임계

- Current

- 곡선

- 감소하다

- 시연

- density

- 기탁 된

- 깊이

- 기술 된

- 디자인

- 개발

- 디바이스

- Mourir

- 외형 치수

- 방향

- 논의 된

- 탈구

- 하기

- 아래 (down)

- 드라이브

- 구동

- 건조

- 두

- e

- E & T

- 생태계

- 효과

- 가능

- 수

- 에너지

- 상승

- 충분히

- 대

- 오류

- 평가

- 평가

- 평가

- 조차

- 있을뿐만 아니라

- 전시

- 기대하는

- 탐험

- 탐험 한

- 노출 시간

- FAST

- Feb

- 들

- 그림

- 채우기

- Film

- 영화

- 초점

- 럭셔리

- 힘

- 공식화

- 발견

- 에

- 추가

- 미래

- 점점

- 좋은

- 초록색

- 했다

- 하드

- 있다

- he

- 개최

- 높은

- 더 높은

- 수평

- 방법

- How To

- 그러나

- HTTPS

- 수소

- i

- 확인

- 설명하다

- 담금

- 개선하는

- 개량

- 향상

- in

- 증가

- 증가

- 표시된

- 인프라

- 처음에는

- 보전

- 인텔

- 상호 연결

- 인터페이스

- 인터뷰

- 소개합니다

- 조사

- 발행물

- 문제

- IT

- JPG

- 키

- 도주

- 경치

- 넓은

- 층

- 레이어

- 리드

- 지도

- 레벨

- 처럼

- 라인

- 명부

- 지방의

- 논리

- 긴

- 장기

- 보기

- 찾고

- 봐라.

- 오프

- 롯

- 낮은

- 만든

- 유튜브 영상을 만드는 것은

- 관리

- 제조

- .

- 마스크

- 마스크

- 일치하는

- 재료

- 최대 폭

- XNUMX월..

- 측정

- 측정 시간 상관관계

- 기계적인

- 메모리

- 메시지

- 금속

- 도량형

- 현미경

- 완화

- 돈

- 배우기

- 많은

- 멀티

- 필요

- 필요

- 요구

- 신제품

- 아니

- 노이즈

- 지금

- 획득

- of

- 오프

- 오프라인

- on

- ONE

- 만

- 기회

- 최적화

- or

- 유기적인

- 기타

- 아웃

- 위에

- 극복하다

- 서류

- 무늬

- 패턴

- 성능

- 관점

- 피치

- 혈장

- 플라톤

- 플라톤 데이터 인텔리전스

- 플라토데이터

- ...을 더한

- 가난한

- 게시하다

- 준비

- 프리젠 테이션

- 제시

- 선물

- 대통령

- 일차

- 문제

- 방법

- 프로세스

- 처리

- 프로파일 링

- 프로그램

- 진행

- 장래가 촉망되는

- 증명 된

- 제공

- 방사

- 율

- 거주비용

- 비율

- 읽기

- 준비

- 최근

- 최근에

- 감소

- 감소

- 감소

- 축소

- 관련

- 남은

- 필요

- 분해능

- 결과

- 결과

- 리뷰

- 로드맵

- 강력한

- 말했다

- 같은

- 스케일링

- 션

- 참조

- 본

- 선택된

- 본인

- SEM

- 반

- 민감한

- 감도

- 변화

- 보여

- 표시

- 측면

- 신호

- 비슷한

- 단일

- 크기

- 경사

- 느리게

- 작은

- So

- 일부

- 출처

- 스페이스 버튼

- 속도

- 지출

- Spot

- 안정

- 안정

- 안정된

- 스택

- 스티브

- 아직도

- 힘

- 강하게

- 교육과정

- 제목

- 이러한

- 충분한

- 우수한

- 표면

- 정지

- 달콤한

- 체계

- 시스템은

- 회담

- 기법

- Technology

- 보다

- 그

- XNUMXD덴탈의

- 블록

- 그들의

- 그때

- 그곳에.

- Bowman의

- 그들

- 맡은 일

- 이

- 올해

- 그

- 세

- 처리량

- 시간

- 에

- 함께

- 너무

- 수단

- 검색을

- 에 대한

- 선로

- 견인

- 교환

- 전통적인

- 두

- 유형

- 궁극의

- 아래에

- 까지

- 사용

- 사용

- 활용

- 여러

- 대

- 수직선

- 대단히

- 를 통해

- 존립 할 수있는

- 부통령

- 휘발성의

- 였다

- 잘

- 갔다

- 뭐

- 동안

- 의지

- 창

- 과

- 작업

- 쓰다

- 쓰기

- year

- 당신

- 제퍼 넷