맞춤 하드웨어가 필요한 트위스트와 함께 시뮬레이션을 가속화하기 위해 하드웨어 지원 예측 병렬 처리를 사용하는 흥미로운 아이디어입니다. Paul Cunningham(Senior VP/GM, Verification at Cadence), Raúl Camposano(Silicon Catalyst, 기업가, 전 Synopsys CTO, 현재 Silvaco CTO)와 저는 연구 아이디어 시리즈를 계속합니다. 언제나처럼 피드백 환영합니다.

혁신

이번 달의 선택은 Chronos: 가속기를 위한 효율적인 추측 병렬 처리. 저자는 프로그래밍 언어 및 운영 체제에 대한 아키텍처 지원에 관한 2020 컨퍼런스에서 논문을 발표했으며 MIT 출신입니다.

멀티코어 프로세서를 사용하여 병렬성을 활용하는 것은 병렬성이 자명한 애플리케이션을 위한 한 가지 옵션입니다. 다른 알고리즘은 그렇게 쉽게 분할되지 않을 수 있지만 본질적인 병렬성을 활용하는 예측 실행의 이점을 얻을 수 있습니다. 일반적으로 예측 실행은 특히 시뮬레이션의 경우 높은 오버헤드인 캐시 일관성에 따라 달라집니다. 이 방법은 일관성에 대한 필요성을 우회하고 대상 읽기-쓰기 개체별로 타일을 계산하기 위해 작업 실행을 물리적으로 지역화하여 글로벌 일관성 관리 없이 로컬에서 충돌 감지를 감지할 수 있도록 합니다. 작업은 추측에 따라 병렬로 실행할 수 있습니다. 감지된 모든 충돌은 하위 작업을 통해 작업에서 풀린 다음 다른 스레드를 중단할 필요 없이 다시 실행할 수 있습니다.

여기서 또 하나 주목할 점. 이 방법은 대부분의 하드웨어 가속 기술과 달리 지연 기반 시뮬레이션을 지원합니다.

바울의 견해

와우, MIT의 멋진 고옥탄가 논문입니다! 병렬 계산에 대해 물으면 즉시 스레드, 뮤텍스 및 메모리 일관성에 대해 생각합니다. 이것은 물론 최신 멀티코어 CPU가 설계되는 방식입니다. 그러나 하드웨어에서 병렬화를 지원하는 유일한 방법은 아닙니다.

이 백서에서는 정렬된 작업 대기열을 기반으로 하는 Chronos라는 병렬화를 위한 대안 아키텍처를 제안합니다. 런타임 시 작업은 타임스탬프 순서로 실행되며 각 작업은 대기열에 동적으로 추가되는 새 하위 작업을 생성할 수 있습니다. 실행은 일부 초기 작업을 대기열에 넣는 것으로 시작하여 대기열에 더 이상 작업이 없으면 종료됩니다.

대기열의 작업은 병렬로 여러 처리 요소(PE)로 파밍됩니다. 즉, Chronos는 현재 작업이 완료되기 전에 추측에 따라 향후 작업을 실행합니다. 현재 작업이 예측적으로 실행된 미래 작업을 무효화하면 해당 미래 작업의 작업이 "실행 취소"되고 대기열에 다시 추가됩니다. 하드웨어에서 이 개념을 올바르게 구현하는 것은 쉽지 않지만 외부 사용자에게는 아름답습니다. 작업 대기열이 단일 PE에서 직렬로 실행되는 것처럼 알고리즘을 코딩하기만 하면 됩니다. 뮤텍스를 코딩하거나 교착 상태에 대해 걱정할 필요가 없습니다.

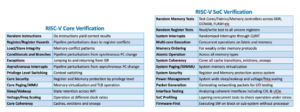

저자는 SystemVerilog에서 Chronos를 구현하고 FPGA로 컴파일합니다. 문서의 대부분은 효율성을 극대화하기 위해 하드웨어에서 작업 대기열과 필요한 언롤링을 구현한 방법을 설명하는 데 할애됩니다. Chronos는 작업 대기열 기반 아키텍처에 적합한 네 가지 알고리즘에 대해 벤치마킹되었습니다. 각 알고리즘은 두 가지 방식으로 구현됩니다. 첫 번째는 전용 알고리즘별 PE를 사용하고 두 번째는 기성 오픈 소스 32비트 임베디드 RISC-V CPU를 PE로 사용하는 것입니다. 그런 다음 Chronos 성능은 Chronos에 사용되는 FPGA와 비슷한 가격표를 가진 Intel Xeon 서버에서 실행되는 알고리즘의 다중 스레드 소프트웨어 구현과 비교됩니다. 결과는 인상적입니다. Chronos는 Xeon 서버를 사용하는 것보다 3배에서 15배 더 잘 확장됩니다. 그러나 표 3을 그림 14와 비교하면 이러한 이득의 대부분이 Chronos 아키텍처 자체가 아니라 알고리즘별 PE에서 나온 것이 아닌지 약간 걱정됩니다.

이것이 검증 블로그라는 점을 감안하여 자연스럽게 게이트 레벨 시뮬레이션 벤치마크를 확대했습니다. EDA 업계는 로직 시뮬레이션을 시도하고 병렬화하기 위해 막대한 투자를 했으며 몇 가지 특정 사용 사례를 넘어서는 큰 이득을 보기 어렵다는 것이 입증되었습니다. 이것은 주로 대부분의 실제 시뮬레이션 성능이 L3 캐시에서 누락되어 DRAM으로 나가는 로드/저장 명령에 의해 지배되기 때문입니다. 이 백서에서 벤치마킹한 테스트 사례는 단 하나이며 작은 32비트 캐리 세이브 가산기입니다. 이 블로그를 읽고 있고 좀 더 철저한 벤치마킹에 관심이 있다면 알려주세요. Chronos가 실제 시뮬레이션에서 진정으로 잘 확장될 수 있다면 엄청난 상업적 가치가 있을 것입니다!

라울의 견해

이 논문의 주요 기여는 공간적으로 위치한 순서가 지정된 작업(SLOT) 실행 모델 이는 병렬성과 추측을 활용하는 하드웨어 가속기와 런타임 시 동적으로 작업을 생성하는 애플리케이션에 효율적입니다. 동적 병렬 처리 지원은 시뮬레이션에 필수적이며 추론적 동기화는 매력적인 옵션이지만 일관성 오버헤드가 너무 높습니다.

SLOT은 각 작업이 단일 개체에서 작동(쓰기)하도록 제한하여 일관성의 필요성을 피하고 다중 개체 원자성을 활성화하기 위해 정렬된 작업을 지원합니다. SLOT 애플리케이션은 타임스탬프와 개체 ID로 특징지어지는 순서대로 동적으로 생성된 작업입니다. 타임스탬프는 주문 제약을 지정합니다. 개체 ID는 데이터 종속성을 지정합니다. 즉, 작업이 동일한 개체 ID를 갖는 경우에만 데이터 종속적입니다. (읽기 종속성이 있는 경우 작업을 예측적으로 실행할 수 있습니다). 충돌 감지는 개체 ID를 코어 또는 타일에 매핑하고 개체 ID가 매핑된 위치로 각 작업을 전송하여 로컬(복잡한 추적 구조 없이)이 됩니다.

XNUMXD덴탈의 Chronos 시스템은 각각 16MHz에서 실행되는 4개의 애플리케이션별 처리 요소(PE)가 있는 125개의 타일이 있는 시스템으로 AWS FPGA 프레임워크에서 구현되었습니다. 이 시스템은 20코어/40스레드 2.4GHz Intel Xeon E5-2676v3으로 구성된 기준선과 비교됩니다. 가격이 FPGA 시스템(시간당 약 $2)과 비슷하기 때문에 특별히 선택되었습니다. 하나의 PE에서 단일 작업을 실행하는 Chronos는 기준선보다 2.45배 빠릅니다. 동시 작업 수가 증가함에 따라 Chronos 구현은 44.9타일에서 8x의 자체 상대적 속도 향상으로 확장되며, 이는 CPU 구현에 비해 15.3x 속도 향상에 해당합니다. 그들은 또한 애플리케이션별 PE가 아닌 범용 RISC-V를 기반으로 한 구현을 비교했습니다. PE는 RISC-V보다 5배 더 빠릅니다.

이 논문은 개념부터 SLOT 실행 모델의 정의, 하드웨어 구현 및 4가지 애플리케이션에 대한 기존 Xeon CPU와의 세부적인 비교에 이르기까지 모든 것을 다루고 있기 때문에 인상적이었습니다. 노력은 상당합니다. Chronos는 SystemVerilog의 20,000줄이 넘습니다. 그 결과 더 많은 병렬 처리와 더 많은 예측 실행 사용으로 인해 소프트웨어 병렬 버전에 비해 평균 5.4배(4개 애플리케이션의) 속도가 향상되었습니다. 이 논문은 시뮬레이션이 아닌 작업에 적용하기 위해 읽을 가치가 있습니다. 이 논문에는 세 가지 예가 포함되어 있습니다.

다음을 통해이 게시물 공유 :

- SEO 기반 콘텐츠 및 PR 배포. 오늘 증폭하십시오.

- 플라토 블록체인. Web3 메타버스 인텔리전스. 지식 증폭. 여기에서 액세스하십시오.

- 출처: https://semiwiki.com/eda/326261-speculation-for-simulation-innovation-in-verification/

- :이다

- 000

- 2020

- 8

- a

- 소개

- 가속

- 가속

- 가속기

- ACM

- 행위

- 추가

- 연산

- 알고리즘

- 대안

- 항상

- 및

- 정치

- 어플리케이션

- 특정 응용 프로그램

- 어플리케이션

- 건축

- 아키텍처

- 있군요

- AS

- At

- 작성자

- AWS

- 기반으로

- 기준

- BE

- 아름다운

- 때문에

- 된다

- 전에

- 존재

- 기준

- 벤치마킹

- 이익

- 더 나은

- 그 너머

- 큰

- 비트

- 블로그

- by

- 캐시

- 운율

- 라는

- CAN

- 나르다

- 가지 경우

- 촉매

- 특징

- 아이

- 선택

- 암호

- 상업

- 유사한

- 비교

- 비교

- 비교

- 진행완료

- 복잡한

- 계산

- 계산

- 개념

- 병발 사정

- 컨퍼런스

- 갈등

- 구성

- 제약

- 계속

- 기부

- 동

- 코스

- 커버

- CPU

- 만들

- 만든

- CTO (최고 기술 담당자)

- Current

- 관습

- 데이터

- 전용

- 의존

- 따라

- 설계

- 상세한

- 탐지 된

- Detection System

- 어려운

- 동적

- 역동적 인

- e

- 마다

- 용이하게

- 효율성

- 효율적인

- 노력

- 요소

- 임베디드

- 가능

- 종료

- 보장

- 기업가

- 특히

- 모두

- 예

- 실행

- 실행

- 실행

- 설명

- 공적

- 빠른

- 피드백

- 를

- 그림

- 먼저,

- 럭셔리

- 이전

- 발견

- FPGA를

- 뼈대

- 에

- 미래

- 이익

- 일반

- 생성

- GHz 인텔

- 글로벌

- 가는

- 하드웨어

- 있다

- 무겁게

- 여기에서 지금 확인해 보세요.

- 높은

- 방법

- 그러나

- HTTPS

- 거대한

- i

- ID

- 생각

- 아이디어

- 바로

- 구현

- 이행

- 구현

- 구현

- 인상

- in

- 포함

- 증가

- 산업

- 피할 수없는

- 처음에는

- 혁신

- 명령

- 인텔

- 관심있는

- 흥미있는

- 본래 갖추어 진

- 투자

- IT

- 그

- 그 자체

- 알아

- 언어

- 라인

- 지방의

- 장소 상에서

- 위치한

- 본관

- 제작

- 구축

- 매핑

- 최대 폭

- 최고

- 방법

- 메모리

- 방법

- 수도

- 누락

- MIT

- 모델

- 현대

- 배우기

- 가장

- 여러

- 필요한

- 필요

- 신제품

- 번호

- 대상

- of

- on

- ONE

- 열 수

- 오픈 소스

- 운영

- 운영

- 운영체제

- 선택권

- 주문

- 기타

- 외부

- 체육

- 서

- 평행

- 폴

- 성능

- 육체적으로

- 선택

- 플라톤

- 플라톤 데이터 인텔리전스

- 플라토데이터

- 부디

- 포인트 적립

- 게시하다

- 제시

- 가격

- 처리

- 가공업자

- 프로그램 작성

- 프로그래밍 언어

- 제안하다

- 증명 된

- 목적

- 입고

- 차라리

- 읽기

- 읽기

- 현실

- 현실 세계

- 연구

- 제한

- 결과

- 결과

- 달리는

- 같은

- 찜하기

- 규모

- 저울

- 둘째

- 전송

- 연장자

- 연속

- 선반

- 규소

- 비슷한

- 시뮬레이션

- 단일

- So

- 소프트웨어

- 일부

- 출처

- 구체적인

- 구체적으로

- 추측

- 실질적인

- SUPPORT

- 지원

- 동기화

- 체계

- 시스템은

- 테이블

- TAG

- 목표

- 태스크

- 작업

- 기법

- 그

- XNUMXD덴탈의

- Bowman의

- 세

- 을 통하여

- 따라서 오른쪽 하단에

- 에

- 너무

- 추적

- 전통적인

- 트위스트

- 사용

- 사용자

- 보통

- 확인

- 를 통해

- 방법..

- 방법

- 환영

- 잘

- 뭐

- 어느

- 과

- 없이

- 훌륭한

- 세계

- 가치

- 겠지

- 쓰다

- 너의

- 제퍼 넷