최근 RISC-V Summit에서 가장 마지막 세션은 '칩렛'에 관한 패널이었습니다. RISC-V 생태계의 칩렛. RISC-V International의 CEO인 Calista Redmond가 사회를 맡았습니다. 패널리스트는 다음과 같습니다.

- Arteris의 COO, Laurent Moll

- Aniket Saha, Tenstorrent 제품 관리 부사장

- Dale Greenley, Ventana Microsystems 엔지니어링 부사장

- Synopsys의 저명한 건축가 Rob Aitken

이것은 나에게 약간 이상한 주제 조합입니다. 분명히 RISC-V 프로세서를 칩렛에 탑재할 수 있지만 문제는 다른 프로세서와 크게 다르지 않습니다. 그러나 RISC-V는 인기가 있고 칩렛도 마찬가지이며 Ventana와 같은 회사는 이를 결합하고 있습니다.

맥락에 맞게 회사에 대한 약간의 배경 지식을 제공하겠습니다.

- 아시다시피 Arteris는 NoC(Network-On-Chip)를 만듭니다. 칩렛 벤더(및 IP 벤더) 사이에서는 중립적인 회사입니다.

- Tenstorrent는 고성능 멀티코어 RISC-V 칩 포트폴리오를 설계하고 있습니다.

- Ventana는 RISC-V IP를 보유하고 있지만 이를 칩렛으로도 제공합니다.

- Synopsys는 분명히 EDA 회사이지만 정상회담 초반에 RISC-V 코어를 발표했습니다.

]

실제 토론

Calista의 첫 번째 질문은 칩렛의 가치를 묻는 소프트볼이었습니다.

Dale은 칩렛용 RISC-V에 대한 구체적인 내용은 없지만 대규모 모놀리식 작업이나 칩렛을 수행하는 시기는 시장이 결정한다고 말했습니다. 이는 고객이 귀하에게 지불할 비용에 따라 다릅니다. "우리는 IP와 칩렛을 모두 제공합니다. 두 가지 모두를 위한 공간이 있습니다."

아니켓은 "칩렛을 만드는 것은 저렴하지 않지만 칩렛과 RISC-V를 하는 것은 유연하고 제품을 빨리 만들 수 있다"고 말했습니다.

Laurent는 제작 비용을 지불했습니다. NRE는 100억 개의 부품을 만드는 사람이 많지 않기 때문에 통제하는 것이 매우 중요합니다. 따라서 더 많은 공급업체가 참여하고 공급망이 복잡해집니다. SoC는 복잡하지만 칩렛은 더 나쁩니다.

Rob은 RF 및 아날로그용 칩렛 추가, 선택적 가속기 보유 등과 같은 이질성을 지적했습니다. 이는 잠재적으로 새로운 시장을 열어줍니다.

Calista는 계속해서 우리가 자동차 분야에서 어디에 있는지 물었습니다.

Aniket은 자동차 분야가 매우 보수적이며 이제는 저가형 자동차에서 고급형 자동차로 확장할 수 있는 플랫폼에 대해 공격적이라고 지적했습니다. 칩렛을 사용하면 누구도 실제로 기능적 안전성을 고려하지 않았습니다.

Rob은 항공우주(자동차는 아님)에 가서 수십 년 전에 일반적으로 정의된 고정된 물리적 볼륨이 어떻게 존재하는지 논의했습니다. 물건을 맞추는 것이 어렵습니다.

Laurent: 자동차 회사는 최고의 카탈로그 구매자이며 칩렛을 사용하면 AI, 레이더, 인포테인먼트 등에서 최고의 이점을 얻을 수 있습니다.

소프트웨어를 실행하려면 어떻게 해야 합니까?

Rob: 시스템을 작게 만들면 괜찮습니다. 그러나 자동차 카탈로그 쇼핑은 더욱 어렵습니다.

Aniket: "만약 당신이 그것을 추가한다면 우리는 그것을 사용하지 않을 것입니다"라는 진술과 관련이 있습니다. 자동차 소프트웨어 스택은 5년 안에 RISC-V를 지원할 예정이며 이는 매우 빠른 속도입니다. Arm이 거기에 도달하는 데 15년이 걸렸습니다.

Q: 연결을 위해서는 무엇이 필요합니까?

Laurent: 특히 칩렛을 쇼핑하는 사람들에게는 매우 복잡합니다. 다양한 공급업체의 PHY가 상호 운용될 수 있습니다. 모두가 UCIe에 열광하고 있습니다. 사람들은 칩렛을 더 잘 맞추는 표준을 원합니다.

Aniket은 칩렛에 대한 표준 설계 흐름이 없다고 불평했습니다. 표준이 크게 부족합니다.

Rob은 우리가 표준 흐름을 생각해낼 수 있다고 생각하지만 서로 다른 칩렛을 사용하면 N개의 서로 다른 설계 흐름을 원하지 않습니다.

Q: 3~5년 후의 상황을 어떻게 보시나요?

Rob: 우리는 다른 사람들과 함께 더 나아갈 것입니다

“카탈로그 쇼핑은 자동차 OEM에 따라 달라질 수 있습니다. 업계의 많은 노력이 필요할 것입니다. 이질적인 것들은 더 오래 걸릴 것입니다.

Aniket은 칩렛이 먼저 데이터 센터에 배치되고 그 다음에는 자동차에 배치될 것이라고 말했습니다. 그러나 첫 번째 물결은 단일 공급업체가 될 것입니다.

요약

이는 참가자들의 발언과 저의 의견을 종합한 것입니다.

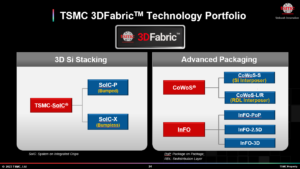

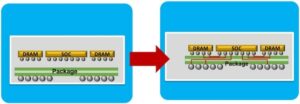

당분간 칩렛 기반 RISC-V 설계는 단일 회사의 노력이 될 것이라고 생각합니다(아마 고대역폭 메모리(HBM)는 제외). 서로 다른 회사, 인터포저의 여러 칩렛으로 디자인을 구축하기에는 너무 복잡합니다. , 그리고 이를 모두 연결하는 네트워크(일반적으로 RDL이라고 함)입니다.

가까운 미래에 설계는 진정한 2.5D(다이가 서로 겹쳐져 있고 실리콘 관통 비아 또는 TSV와 통신하는 곳)가 아닌 3D가 될 것입니다.

자동차에는 고유한 과제가 있습니다. 특히 진동이 많은 환경에서 칩렛 기반 설계의 신뢰성을 보장하는 것이 중요합니다. 이를 위해서는 광범위한 테스트가 필요합니다. 또 다른 문제는 멀티 다이 환경에서 기능적 안전성을 보장하는 것입니다.

UCIe는 유망하며 어느 정도 PCIe를 기반으로 합니다. PCIe 회사는 플러그페스트를 통해 신뢰성을 확보했습니다. 비슷한 메커니즘을 통해 어떻게 칩렛에서 UCIe 상호 운용성을 경제적으로 보장할 수 있는지 모르겠습니다.

마지막으로, 기성품인 칩렛을 구매하여 합리적인 비용으로 시스템에 조립할 수 있는 열반에 도달하려면 기술적 과제 외에도 상업적 과제가 있습니다. 가장 큰 과제는 누가 칩렛 재고를 지불하고 보유할 것인가입니다. 모든 칩렛을 주문형으로 제조해야 한다면 빠른 사이클 시간의 많은 이점이 손실됩니다.

그러나 RISC-V 칩렛은 단일 회사에서 제작한 2.5D 인터포저의 멀티 다이 설계 형태로 확실히 빠르게 발전하고 있습니다.

또한 읽기 :

NoC는 설계자에게 시스템 내 RISC-V 설계에 유연성을 제공합니다.

RISC-V 코어를 NoC와 페어링하면 SoC 프로토콜이 하나로 연결됩니다.

다음을 통해이 게시물 공유 :

- SEO 기반 콘텐츠 및 PR 배포. 오늘 증폭하십시오.

- PlatoData.Network 수직 생성 Ai. 자신에게 권한을 부여하십시오. 여기에서 액세스하십시오.

- PlatoAiStream. 웹3 인텔리전스. 지식 증폭. 여기에서 액세스하십시오.

- 플라톤ESG. 탄소, 클린테크, 에너지, 환경, 태양광, 폐기물 관리. 여기에서 액세스하십시오.

- PlatoHealth. 생명 공학 및 임상 시험 인텔리전스. 여기에서 액세스하십시오.

- 출처: https://semiwiki.com/ip/arteris/338888-risc-v-and-chiplets-a-panel-discussion/

- :있다

- :이다

- :아니

- :어디

- $UP

- 100M

- 15년

- 15%

- 167

- 200

- 300

- 3d

- a

- 할 수 있는

- 소개

- 가속 자

- 실제

- 더하다

- 첨가

- 또한

- 장점

- 항공우주

- 적극적인

- ...전에

- AI

- All

- 따라

- 또한

- 중

- an

- 및

- 발표

- 다른

- 어떤

- 건축가

- 있군요

- ARM

- 약

- AS

- 문의

- 질문

- At

- 자동차

- 배경

- 기반으로

- BE

- 존재

- BEST

- 더 나은

- 큰

- 가장 큰

- 비트

- 두

- 빌드

- 건물

- 내장

- 비자 면제 프로그램에 해당하는 국가의 시민권을 가지고 있지만

- by

- 라는

- CAN

- 자동차

- 목록

- 대표 이사

- 확실히

- 체인

- 도전

- 과제

- 싼

- 색

- 결합

- 결합

- 왔다

- 오는

- 상업

- 소통

- 기업

- 회사

- 복잡한

- 복잡한

- 연결하기

- 입/출력 라인

- 보수적인

- 고려

- 문맥

- 제어

- 구구

- 비용

- 비용

- 고객

- 주기

- 데이터 센터

- 수십 년

- 한정된

- 제공

- 의존

- 따라

- 디자인

- 설계

- 디자인

- Mourir

- 다른

- 논의 된

- 토론

- 저명한

- do

- 하기

- 말라

- 마다

- 이전

- 노력

- end

- 엔지니어링

- 확인

- 보장

- 보장

- 환경

- 특히

- 사람

- 외

- 광대 한

- FAST

- 끝

- 먼저,

- 맞게

- 고정

- 유연성

- 융통성있는

- 흐름

- 흐름

- 럭셔리

- 예측

- 형태

- 에

- 기능의

- 추가

- 미래

- 얻을

- 주기

- 하드

- 열심히

- 있다

- 데

- 높은

- 고성능

- 보유

- 뜨거운

- 방법

- HTTPS

- i

- if

- 중대한

- in

- 산업

- 국제 노동자 동맹

- 상호 운용성

- 상호 운용 가능한

- 으로

- 목록

- 참여

- IP

- 발행물

- IT

- 그

- JPG

- 날카로운

- 유지

- 알아

- 알려진

- 결핍

- 성

- 하자

- 처럼

- 이상

- 잃어버린

- 롯

- 낮은

- 확인

- 제작

- 구축

- 제조 한

- .

- 많은 사람

- 시장

- 시장

- 최대 폭

- XNUMX월..

- 아마도

- me

- 기구

- 단단히 짜여 하나로 되어 있는

- 배우기

- 여러

- my

- 필요

- 네트워크

- 중립의

- 신제품

- 아니

- 아무것도

- 지금

- of

- on

- 온디맨드

- ONE

- 열립니다

- 의견

- or

- 기타

- 아웃

- 자신의

- 패널

- 패널 토론

- 참가자

- 특별한

- 부품

- 지불

- 사람들

- 혹시

- 물리적

- 플랫폼

- 플라톤

- 플라톤 데이터 인텔리전스

- 플라토데이터

- 유가 증권

- 게시하다

- 잠재적으로

- 아마

- 프로세서

- 프로덕트

- 제품 관리

- 생산

- 제품

- 장래가 촉망되는

- 프로토콜

- 제공

- 매수

- 놓다

- 문제

- 아주

- 레이더

- 읽기

- 정말

- 합리적인

- 최근

- 관련

- 신뢰성

- 신뢰할 수있는

- 필요

- 방

- 달리기

- 안전

- 말했다

- 규모

- 참조

- 세션

- 세트

- 쇼핑객

- 쇼핑

- 비슷한

- 이후

- 단일

- 작은

- So

- 소프트웨어

- 약간

- 구체적인

- 쌓인

- 스택

- 표준

- 기준

- 성명서

- 정상 회담

- 공급

- 공급망

- SUPPORT

- 체계

- 시스템은

- 받아

- 말하는

- 테크니컬

- 지원

- 그

- XNUMXD덴탈의

- 그들

- 그때

- 그곳에.

- 그들

- 일

- 생각

- 생각

- 이

- 을 통하여

- 넥타이

- 시간

- 에

- 너무

- 했다

- 상단

- 이상의 주제

- 참된

- 궁극의

- 아래에

- 업데이트

- 사용

- 보통

- 가치

- 공급 업체

- 공급 업체

- 대단히

- 를 통해

- 음량

- vp

- 필요

- 였다

- 웨이브

- we

- 갔다

- 했다

- 뭐

- 언제

- 어느

- 누구

- 의지

- 과

- 악화되는

- 년

- 당신

- 제퍼 넷