수년에 걸쳐 DRC 도구는 IC 설계 크기의 엄청난 성장에 보조를 맞추는 훌륭한 작업을 수행해 왔습니다. 그러나 DRC는 파운드리 규칙 데크를 사용하여 전체 설계를 승인하기 위해 실행되며 완료하는 데 많은 시간이 걸립니다. 이러한 긴 실행 시간은 최종 승인에는 허용되지만, 후반 단계 문제를 해결하기 위해 설계를 약간 변경하는 경우 DRC 결과가 빠르게 필요한 상황이 많이 있습니다. MaxLinear와 함께 Siemens EDA는 Calibre RealTime Digital 설계 내 DRC가 설계에 작은 변경이 있을 때 DRC 결과를 신속하게 제공할 수 있는 방법을 보여주는 백서를 작성했습니다. 국부적인 변경 사항에 대한 DRC 처리 속도가 빨라지면 테이프아웃에 도달하는 데 종종 필요한 반복 오류 수정 속도가 빨라질 수 있습니다.

"MaxLinear 및 Calibre RealTime Digital: 보다 빠른 사인오프 DRC 컨버전스 및 제조 가능성을 위한 설계 최적화"라는 제목의 백서에서 MaxLinear와 Siemens는 전체 파운드리 규칙 데크를 사용하여 설계의 작은 영역에서 DRC를 실행할 수 있는 능력이 있는 상황에 대해 이야기합니다. 많은 시간과 고통스러운 느린 반복을 절약할 수 있습니다.

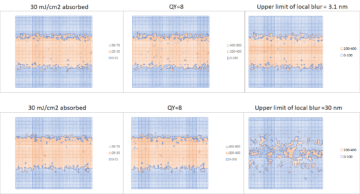

최신 P&R 도구는 DRC에 맞는 레이아웃을 생성하는 데 탁월한 역할을 합니다. 그러나 위반 원인이 더 복잡하고 P&R 중에 누락되는 경우가 항상 있습니다. 일반적으로 복잡한 설계 규칙을 고려하여 수동으로 수정해야 합니다. 이러한 수동 수정 중에 새로운 오류가 발생할 가능성도 있습니다. Siemens는 Calibre RealTime Digital이 P&R 도구와 어떻게 인터페이스하여 수동 수정 사항을 신속하게 구현하고 검증할 수 있는지 강조하는 MaxLinear의 정보를 백서에 제시합니다. 대안은 작은 영역의 변경 사항이 올바른지 확인하기 위해 전체 DRC 실행을 수행하는 것입니다.

MaxLinear는 아날로그 및 디지털 블록으로 칩을 만듭니다. 아날로그 블록에는 더 적은 수의 금속 레이어가 필요하므로 제조 비용을 줄이기 위해 전체 설계에서 라우팅 레이어를 줄이는 방법을 모색합니다. 이로 인해 높은 DFM 순위를 유지하는 것과 종종 충돌하는 라우팅 밀도 문제가 발생합니다. 단일 컷 비아는 공간을 가장 적게 사용하지만 DFM 순위가 낮습니다. 압박이 가해지면 MaxLinear 설계자는 라우팅 가능성과 DFM 절충점을 처리하기 위해 유형을 통해 수동으로 전환할 수 있습니다. 그러나 다중 패턴 위반과 같은 사항을 확인하려면 포괄적인 DRC를 통해 후속 조치를 취해야 합니다. Calibre RealTime Digital을 사용하면 디자이너가 유형을 통해 교체한 다음 DRC 오류가 있는지 빠르게 확인할 수 있습니다.

비아는 해결하는 데 시간과 노력이 필요한 DRC 문제로 이어질 수 있는 유일한 문제는 아닙니다. 백서에서는 수동 작업이 필요한 여러 상황을 설명하며 이러한 문제를 최종적으로 해결하는 유일한 방법은 깨끗한 DRC를 실행하는 것입니다. 프로세스 후반에 발생하는 상황 중 하나는 ECO가 기존 마스크와 호환되는지 확인하기 위해 RTO(재테이프아웃) 검사가 필요한 경우입니다. RTO 규칙은 본질적으로 원래 DRC 규칙보다 더 제한적입니다.

또한 백서는 부적절한 비아 사용으로 인해 발생할 수 있는 일렉트로마이그레이션 문제에 대해서도 다루고 있습니다. 여기서도 Calibre ReatTime Digital은 MaxLinear가 교체를 통해 DRC 수정을 구현하는 데 중요한 역할을 했습니다. 종합적으로 보면, 설계의 기능 또는 제조 가능성 문제를 수정하기 위해 작은 변경이 이루어진 후 DRC 검사가 필요한 많은 상황이 있습니다. 전체 DRC 실행 시 하루 이상 소요되는 시간을 기다리는 대신 즉각적인 결과를 얻을 수 있으면 프로젝트 기간을 며칠 또는 몇 주 단축할 수 있습니다. 대규모 DRC 실행 후 놀라움을 찾는 것은 좋지 않습니다. P&R 도구에 대한 Siemens Calibre RealTime Digital 인터페이스는 이에 이상적인 것으로 보입니다. 본 Siemens 백서는 Siemens EDA 웹사이트에서 확인할 수 있습니다.

다음을 통해이 게시물 공유 :

출처: https://semiwiki.com/eda/299770-realtime-digital-drc-can-save-time-close-to-tapeout/