Synopsys는 Intel Graphics의 Theo Drane 박사가 진행한 흥미로운 강연을 SolvNet 사이트에 게시했습니다. 주제는 데이터 경로 동등성 검사입니다. 또 다른 Synopsys VC 공식 DPV 보증처럼 들릴 수도 있지만 어쨌든 시청해야 합니다. 이것은 일상적인 사용자 가이드 유형의 피치를 넘어 더 흥미로운 영역으로 여러분을 안내할 공식적인 사용 및 고려 사항에 대한 마음을 넓히는 토론입니다.

지적 이해와 샘플 테스트

모든 형태의 테스트 기반 시뮬레이션은 설계 사양이나 구현의 정확성을 검증하는 데 탁월하며 대체할 수 없는 경우가 많습니다. 시작하는 것도 쉽습니다. 테스트 프로그램을 작성하고 시뮬레이션을 시작하면 됩니다. 하지만 그 단순함의 이면은 우리가 그럴 필요가 없다는 것입니다. 충분히 시작하기 위해 무엇을 테스트하고 있는지 이해하세요. 우리는 사양을 주의 깊게 읽고 모든 특수 사례를 이해했다고 스스로 확신하지만, 우리의 이해를 압도하기 위해 복잡한 복잡성이 필요하지는 않습니다.

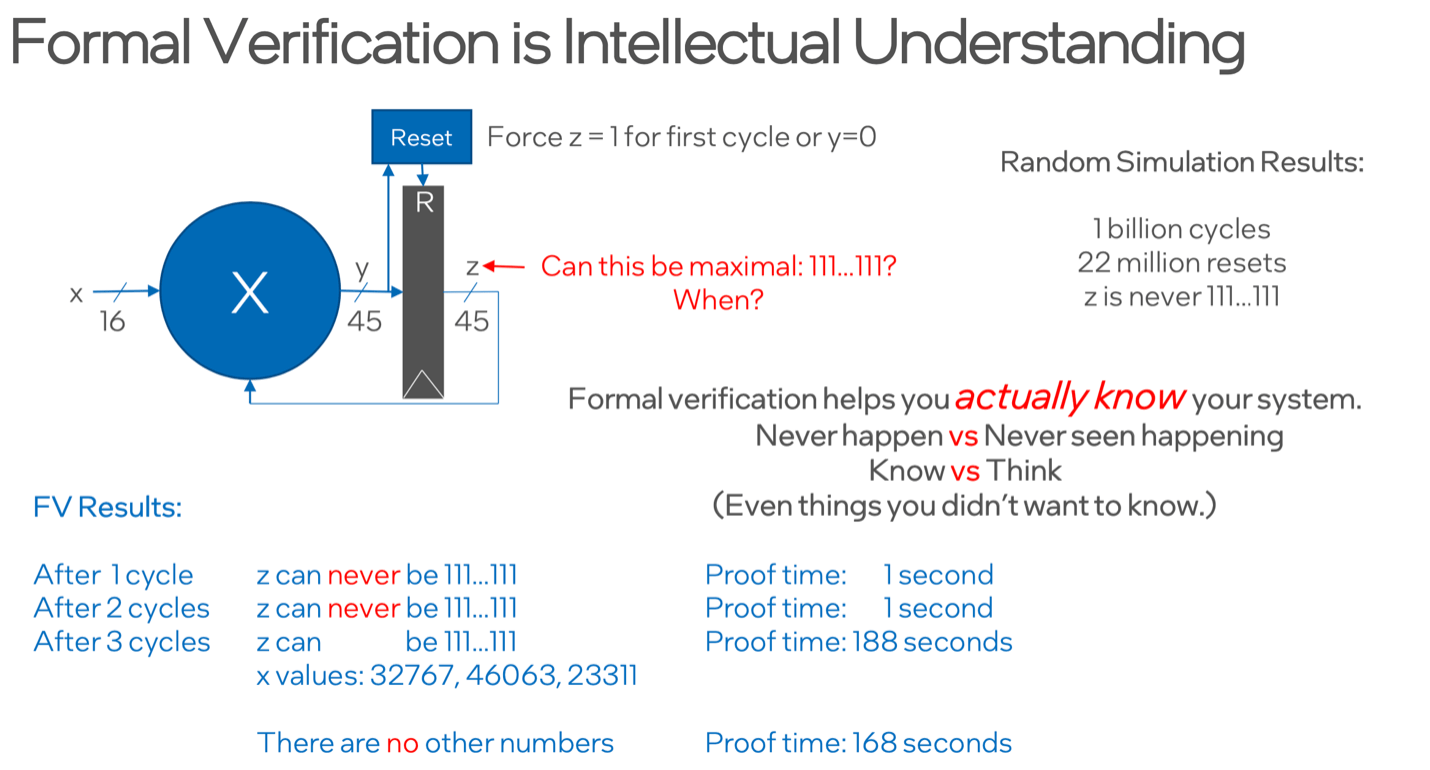

Formal은 (적어도 가치 있는 결과를 제공하려는 경우) 심층적인 수준에서 기능을 이해하도록 권장합니다. 위의 예에서 간단한 질문(z가 모두 1이 될 수 있습니까?)은 시뮬레이터에서 188억 주기의 예를 보여주지 못합니다. 이는 극단적인 경우이기 때문에 놀라운 일은 아닙니다. 공식 테스트는 XNUMX초 안에 구체적이고 매우 명확하지 않은 예를 제공하며 이것이 약간 더 짧은 시간 내에 유일한 사례임을 증명할 수 있습니다.

OK 형식은 동적 테스트가 할 수 없는 일을 해냈지만 더 중요한 것은 시뮬레이터가 결코 말하지 않았을 수도 있는 것을 배웠다는 것입니다. 그런 상황이 일어날 수 있는 경우는 딱 한 가지뿐이었다. Formal은 유한한 테스트 케이스 세트에 대한 확률적 요약이 아닌 지적 수준에서 디자인을 더 잘 이해하는 데 도움이 되었습니다.

사양 문제

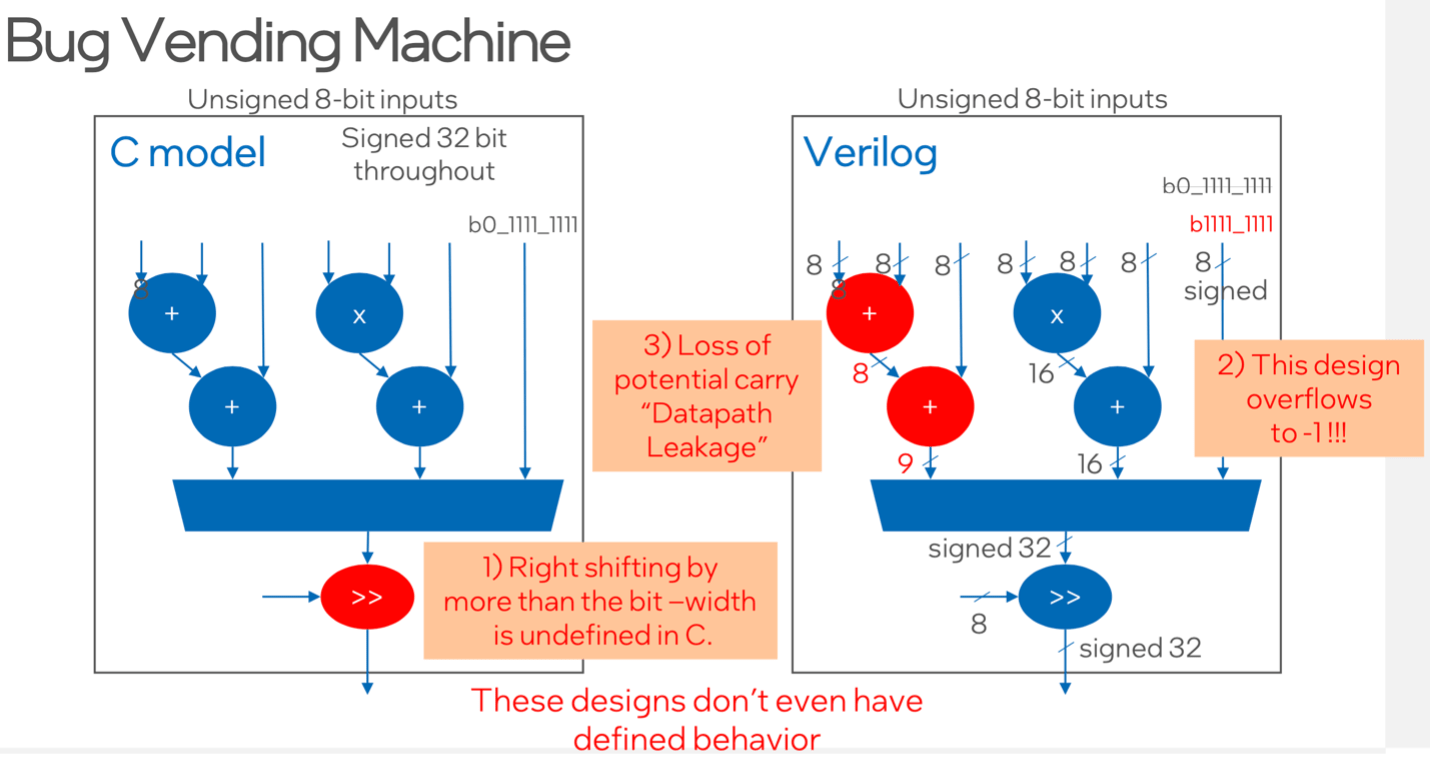

Theo의 다음 예는 버그 자동 판매기를 기반으로 합니다(버튼을 누르면 버그가 발생하기 때문에 소위 불림). 이는 매우 간단한 C 대 RTL 동등성 확인 문제처럼 보입니다. 왼쪽은 C 모델, 오른쪽은 RTL 모델입니다. 공식 분야 초기에 Theo가 놀랐던 점 중 하나는 gcc가 합리적으로 작동하더라도 C 모델의 오른쪽 시프트 동작이 C 표준에서 완전히 정의되지 않았다는 것입니다. 그러나 DPV는 RTL과의 비교에서 불일치에 대해 불평할 것입니다. 정의되지 않은 동작은 의존하기 위험한 것입니다.

C와 RTL 간의 사양 비교에는 특히 비트 폭과 관련된 다른 위험이 있습니다. 중간 신호(위의 #3)에서 캐리 비트의 잘림이나 손실이 좋은 예입니다. 이게 사양 문제인가요? 사양과 구현 선택 사이의 회색 영역일 수도 있습니다.

동등성 검사를 넘어

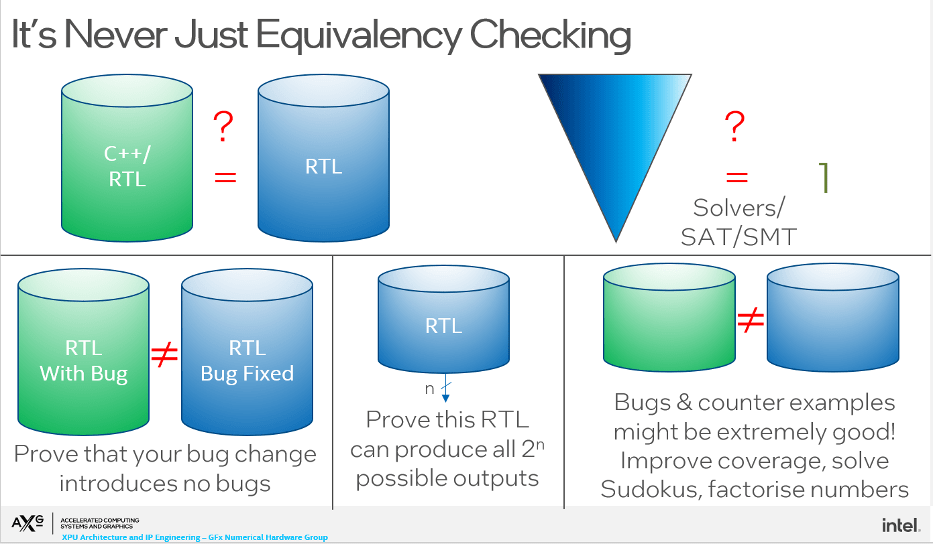

DPV의 주요 목적은 C 또는 RTL 참조와 RTL 구현 간의 동등성을 확인하는 것 같습니다. 그러나 그러한 필요성은 상대적으로 드물며, 약간만 벗어나면 그러한 기술을 적용할 수 있는 다른 유용한 방법이 있습니다. 첫 번째는 구현 세계의 고전입니다. 변경하고 버그를 수정했습니다. 결과적으로 새로운 버그가 생겼습니까? 클럭 게이팅을 추가한 후 SEQ를 확인하는 것과 비슷합니다. 블록 출력의 도달 가능성 분석은 경우에 따라 또 다른 유용한 애플리케이션이 될 수 있습니다.

테오는 더욱 창의적이 되어 훈련생들에게 디자인을 더 잘 이해하기 위해 반대 사례를 사용하도록 요청하고, 스도쿠 풀기 or 정수 인수분해. 그는 DPV가 그러한 문제에 접근하는 이상한 방법이라는 것을 인정하지만 그의 의도는 DPV가 동등성 확인에만 사용된다는 환상을 깨는 것임을 지적합니다. 흥미로운 아이디어이며 그러한 도전을 통해 생각하는 것은 확실히 두뇌 확장입니다. (그가 스도쿠 문제를 언급하자마자 나는 즉시 스도쿠 문제에 대해 생각하기 시작했다고 고백합니다.)

시공 종합

Theo는 제약 조건, 회귀 및 레거시 RTL 모델과의 비교를 중심으로 생산 사용에 중요한 방법론에 대한 논의로 결론을 내립니다. 또한 확인하고 있는 내용이 실제로 최상위 자연어 사양과 일치하는지 여부를 아는 데 어려움이 있습니다.

매우 활력이 넘치는 강연, 볼만한 가치가 있습니다 여기 SolvNet에서!

다음을 통해이 게시물 공유 :

- SEO 기반 콘텐츠 및 PR 배포. 오늘 증폭하십시오.

- 플라토 블록체인. Web3 메타버스 인텔리전스. 지식 증폭. 여기에서 액세스하십시오.

- 출처: https://semiwiki.com/eda/325878-intel-keynote-on-formal-a-mind-stretcher/

- :이다

- a

- 소개

- 위의

- 가로질러

- 실제로

- 후

- All

- 분석

- 및

- 다른

- 어플리케이션

- 적용된

- 접근

- 있군요

- 지역

- 약

- AS

- At

- 기반으로

- BE

- 때문에

- 더 나은

- 사이에

- 그 너머

- 억원

- 비트

- 블록

- 보물상자

- 흩어져

- 곤충

- 버그

- 단추

- by

- 라는

- CAN

- 면밀히

- 나르다

- 케이스

- 가지 경우

- 확실히

- 과제

- 이전 단계로 돌아가기

- 검사

- 확인

- 선택

- 고전적인

- 시계

- 비교

- 완전히

- 복잡성

- 조건

- 고려 사항

- 제약

- 납득시키다

- 모서리

- 수

- 계수기

- 창조적 인

- 주기

- 위험한

- 일

- 깊은

- 한정된

- 배달하다

- 보여

- 디자인

- DID

- 토론

- 하지 않습니다

- 말라

- 동적

- 초기의

- 격려하다

- 특히

- 조차

- EVER

- 예

- 예

- 우수한

- 극단

- 실패

- 매혹적인

- 먼저,

- 고정

- 플립

- 럭셔리

- 형식적인

- 양식

- 기능

- GCC

- 얻을

- 주어진

- 좋은

- 그래픽

- 회색

- 회색 영역

- 발생

- 있다

- 도움

- 그러나

- HTTPS

- i

- 생각

- 바로

- 이행

- 중대한

- in

- 인텔

- 지적인

- 의지

- 흥미있는

- 중간의

- 소개

- 문제

- IT

- 그

- 기조

- 종류

- 아는

- 언어

- 배운

- 유산

- 레벨

- 처럼

- 작은

- 봐라.

- 오프

- 기계

- 만든

- 확인

- 최대 폭

- 말하는

- 방법론

- 수도

- 모델

- 모델

- 배우기

- 자연의

- 자연어

- 필요

- 신제품

- 다음 것

- of

- on

- ONE

- 기타

- 피치

- 플라톤

- 플라톤 데이터 인텔리전스

- 플라토데이터

- 전철기

- 가능한

- 게시하다

- 게시

- 키를 눌러

- 예쁜

- 일차

- 문제

- 문제

- 생산

- 프로그램

- 증명

- 제공

- 목적

- 문제

- 읽기

- 상대적으로

- 결과

- 초

- 세트

- 영상을

- 신호

- 단순, 간단, 편리

- 간단

- 시뮬레이션

- 시뮬레이터

- 이후

- 대지

- So

- 일부

- 무언가

- 예정입니다.

- 소리

- 구체적인

- 명세서

- 표준

- 스타트

- 시작

- 똑 바른

- 이러한

- 개요

- 놀람

- 놀라운

- 받아

- 이야기

- Technology

- test

- 지원

- 그

- XNUMXD덴탈의

- Bowman의

- 맡은 일

- 사고력

- 을 통하여

- 시간

- 에

- 최고 수준

- 화제

- 잘림

- 이해

- 이해

- 용법

- 사용

- 가치 있는

- VC

- 확인하는

- 대

- 를 통해

- 손목 시계

- 시청

- 방법..

- 방법

- 잘

- 뭐

- 여부

- 어느

- 의지

- 과

- 세계

- 가치

- 겠지

- 쓰다

- 제퍼 넷