Columbia University의 연구원들은 "EigenEdge: Real-Time Software Execution at the Edge with RISC-V and Hardware Accelerators"라는 제목의 새로운 기술 문서를 발표했습니다.

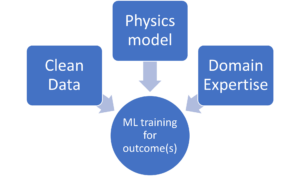

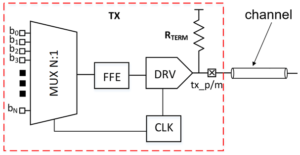

“우리는 선형 대수 워크로드를 추상화하는 강력한 오픈 소스 C++ 라이브러리인 Eigen으로 설계된 소프트웨어 애플리케이션과 이기종 SoC(System-on-Chip) 아키텍처에서 실시간 실행을 결합하는 하드웨어/소프트웨어 공동 설계 접근 방식을 소개합니다. 우리는 CVA6 RISC-V 프로세서와 맞춤형 하드웨어 가속기를 통합할 수 있는 오픈 소스 SoC 설계 플랫폼인 ESP를 사용합니다.

찾기 여기에 기술 문서. 2023년 XNUMX월 게시.

Kuan-Lin Chiu, Guy Eichler, Biruk Seyoum, Luca Carloni. 2023. EigenEdge: RISC-V 및 하드웨어 가속기로 에지에서 실시간 소프트웨어 실행. Cyber-Physical Systems and Internet of Things Week 2023(CPS-IoT Week '23) 절차에서. 컴퓨팅 기계 협회, 뉴욕, 뉴욕, 미국, 209–214. https://doi.org/10.1145/3576914.3587510

- SEO 기반 콘텐츠 및 PR 배포. 오늘 증폭하십시오.

- PlatoAiStream. Web3 데이터 인텔리전스. 지식 증폭. 여기에서 액세스하십시오.

- 미래 만들기 w Adryenn Ashley. 여기에서 액세스하십시오.

- PREIPO®로 PRE-IPO 회사의 주식을 사고 팔 수 있습니다. 여기에서 액세스하십시오.

- 출처: https://semiengineering.com/edge-hw-sw-co-design-platform-integrating-risc-v-and-hw-accelerators/