アナログ IC の設計者は、回路設計に古くて使い慣れた手動の反復手法を再利用することに多大な時間と労力を費やす可能性があります。 回路の最適化は、PVT コーナーとプロセスのバリエーション全体で SPICE シミュレーションを実行することにより、セル内のすべてのトランジスタのサイズを自動的に決定できる EDA アプローチであり、アナログおよび混合信号の設計要件を満たします。 有望ですね。

では、どの回路オプティマイザーの使用を検討すべきでしょうか?

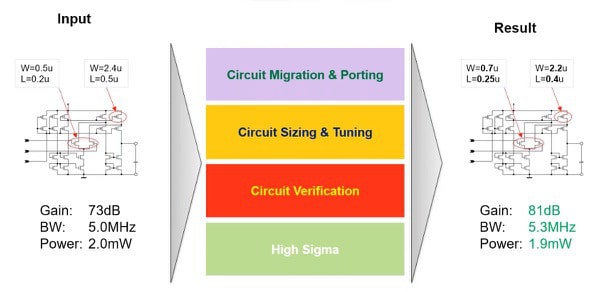

その質問に答えるために、ウェビナーが開催されます。 むねだ、2001年に設立されたEDA会社であり、それはすべて、 邪悪な. 入力は、ゲイン、帯域幅、消費電力などの設計要件に沿った SPICE ネットリストです。 出力は、設計要件を満たすか超えるサイズのネットリストです。

WiCkeD の秘密のソースは、機械学習 (ML) モデルを構築して実験計画法 (DOE) を実行し、最悪のケースの PVT コーナーを計算し、トランジスタのジオメトリの感度を見つけ、オンチップ変動 (OCV) を計算する方法です。 ) 感度。 このアプローチでは、シミュレートされたデータから非線形の高次元 ML モデルを作成および更新します。

ML モデルを使用すると、ツールで最適化の課題を解決し、SPICE シミュレーションを実行して最終検証を行うことができます。 すべての要件が満たされるまで、自動反復があります。 今では、古い手動の反復方法よりもはるかに高速に聞こえます。 ML モデルのトレーニングはすべて自動的に行われ、非常に効率的です。

回路設計者は次のことも学びます。

- 回路最適化を使用する場所

- 最適化に適した回路の種類

- 回路の最適化が設計フローにもたらす価値

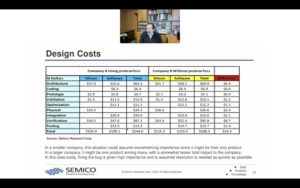

STMicroelectronics のエンジニアは WiCkeD で回路最適化を使用しており、MunEDA は時間の節約と要件を満たすための改善における具体的な結果について語っています。 パワー アンプの会社である Inplay Technologies は、DAC 2018 カンファレンスの回路最適化の結果を示しました。

ウェビナーの詳細

11 月 10 日午前 XNUMX 時 (PDT) のウェビナーをご覧ください。 オンライン登録.

関連ブログ

この投稿を共有する:- SEO を活用したコンテンツと PR 配信。 今日増幅されます。

- Platoblockchain。 Web3メタバースインテリジェンス。 知識の増幅。 こちらからアクセスしてください。

- 情報源: https://semiwiki.com/eda/326047-webinar-enhance-productivity-with-machine-learning-in-the-analog-front-end-design-flow/

- :は

- $UP

- 2001

- 2018

- a

- 私たちについて

- 越えて

- すべて

- 常に

- &

- 回答

- アプローチ

- 4月

- です

- At

- 自動化

- オートマチック

- 自動的に

- バック

- 帯域幅

- なぜなら

- もたらす

- 構築します

- by

- 計算する

- 缶

- 挑戦する

- チップ

- 到来

- 会社

- 講演

- 検討

- 消費

- コーナー

- コーナー

- 作成します。

- データ

- 設計

- デザイナー

- DOE

- 効率的な

- 努力

- 可能

- さらに

- 超えます

- おなじみの

- 速いです

- ファイナル

- もう完成させ、ワークスペースに掲示しましたか?

- フロー

- から

- 利得

- 良い

- 持ってる

- 主催

- 認定条件

- HTTPS

- i

- 改善

- in

- IT

- 繰り返し

- 繰り返し

- JPG

- LEARN

- 学習

- ような

- 機械

- 機械学習

- マニュアル

- 最大幅

- 大会

- ご相談

- ミーツ

- メソッド

- ML

- 名前付き

- of

- 古い

- on

- 最適化

- プラトン

- プラトンデータインテリジェンス

- プラトデータ

- ポスト

- 電力

- プロセス

- 生産性

- 有望

- 質問

- 要件

- 結果

- ラン

- ランニング

- 貯蓄

- 秘密

- すべき

- サイズ

- 特定の

- 過ごす

- スパイス

- 開始

- トーク

- テクノロジー

- それ

- アプリ環境に合わせて

- 時間

- 〜へ

- あまりに

- ツール

- トレーニング

- 更新版

- つかいます

- 値

- Verification

- 、

- 仕方..

- which

- 意志

- ゼファーネット