設計者には、RISC-V ソリューションを差別化するための多くの方法があります。 XNUMX つのパスは、仕様に応じたさまざまな RISC-V コアのカスタマイズと拡張につながります。 もう XNUMX つは、XNUMX つ以上の RISC-V コアを中心とした完全なシステムオンチップ (SoC) 設計における IP ブロックの選択と組み立てに焦点を当てています。 XNUMX 番目の方法は、RISC-V コアと他の IP ブロックを、単純なバス構造ではなくネットワーク オン チップ (NoC) で相互接続する方法です。 それはハイエンドだけではありません。RISC-V コアと NoC を組み合わせることで、オンチップ プロトコルを使用してあらゆるワークロードでデータを効率的に流す必要がある多くの SoC 設計の課題に答えられます。

高度な相互接続スキームにより変化するパフォーマンス層

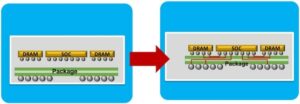

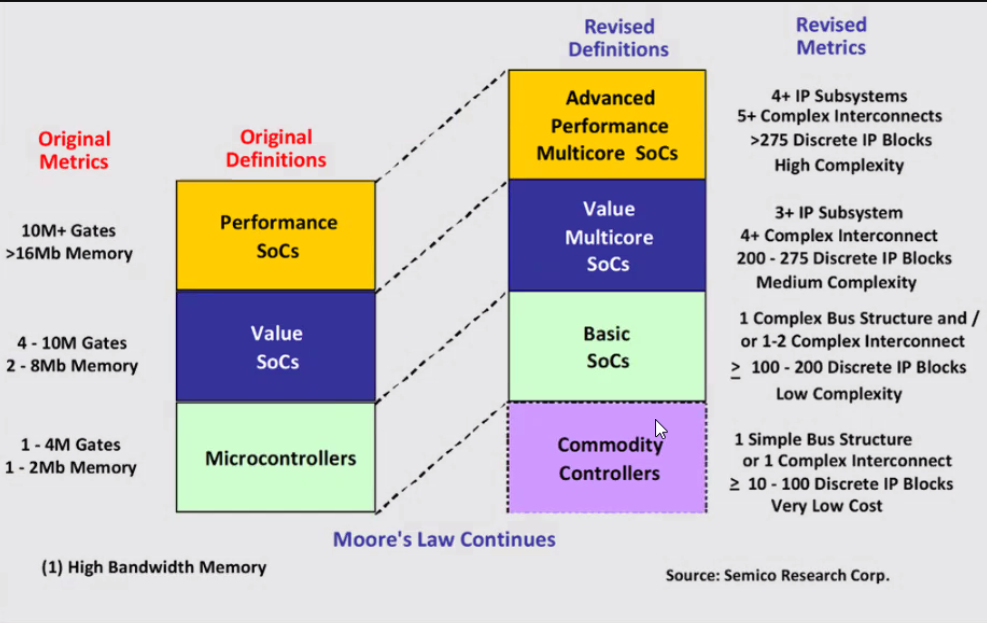

ゲート、コア、ペリフェラル ブロックの数を単純に数えるだけでは、SoC 設計の潜在的なパフォーマンスを説明できなくなります。 Semico Research によると、現在では相互接続スキームによって SoC パフォーマンス層間の境界線が定義されており、相互接続が単純なバス構造からより洗練されたスキームに変化する新しい層が開かれています。

Semico の更新された定義では、マルチコア設計の普及、複雑な設計とみなされるもののより高い基準、そしてその後の「マイクロコントローラー」と「SoC」の間の曖昧な境界という XNUMX つの力が働いていることが認識されています。 Semico の最新の見解では、XNUMX つの最新のプロセッサ コアが多くのゲートを引きずる可能性があるため、メトリクスとしてのゲート数の概念は消滅します。 複雑さは相互接続の関数となり、サブシステムやさまざまな IP ブロックによって異なります。

SoC パフォーマンス層、画像提供: Semico Research Corp.

単一のプロセッサコアとバスを巡って継続的に競合しない低デューティサイクルの周辺機器を備えた部品など、単純なバスで十分な場合、セミコはコモディティコントローラ層を検討しています。 それ以上のものはすべて SoC になり、おそらく少なくともいくつかのペリフェラルがオンチップの帯域幅とプロセッサ コアからの注目を争うようになります。 上位の SoC 層には複数のコアと複数の IP サブシステムがあり、それぞれが調整された相互接続テクノロジーを備えています。

NoC はより多くのプロトコルとサブシステムを採用します

RISC-V は、より強力なコアが登場するにつれて、これらのパフォーマンス層を急速に引き上げてきましたが、Semico スケールの下限でも同様に適用可能です。 ただし、RISC-V 設計者は、上位層に見られる複雑な相互接続スキームの経験が少ない場合があります。 「RISC-V 相互接続として TileLink が真っ先に思い浮かぶかもしれませんが、より複雑なシナリオでは使用が難しい場合があります」と Arteris のソリューションおよびビジネス開発担当副社長の Frank Schirmeister 氏は述べています。

NoC の優れた点は、異なるプロトコルを使用してサブシステムを接続できることです。SoC 設計者は、中程度の複雑さでも複数のプロトコルに遭遇する可能性があります。 AXI は、シンプルな IP ブロック接続の競争の場を平準化しました。 共同処理ブロックを備えたマルチコア ソリューションにはキャッシュ コヒーレンスが必要であり、CHI プロトコルが誕生します。 I/O メモリの共有は、より高速な CXL 相互接続の形成に役立ちました。 「さまざまなサブシステムやプロトコルを使用してコンピューティングとトランスポートを共同最適化するときは、NoC の方が優れたソリューションです」とシルマイスター氏は続けます。

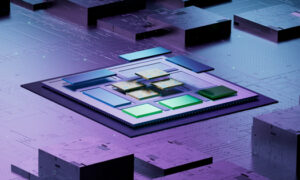

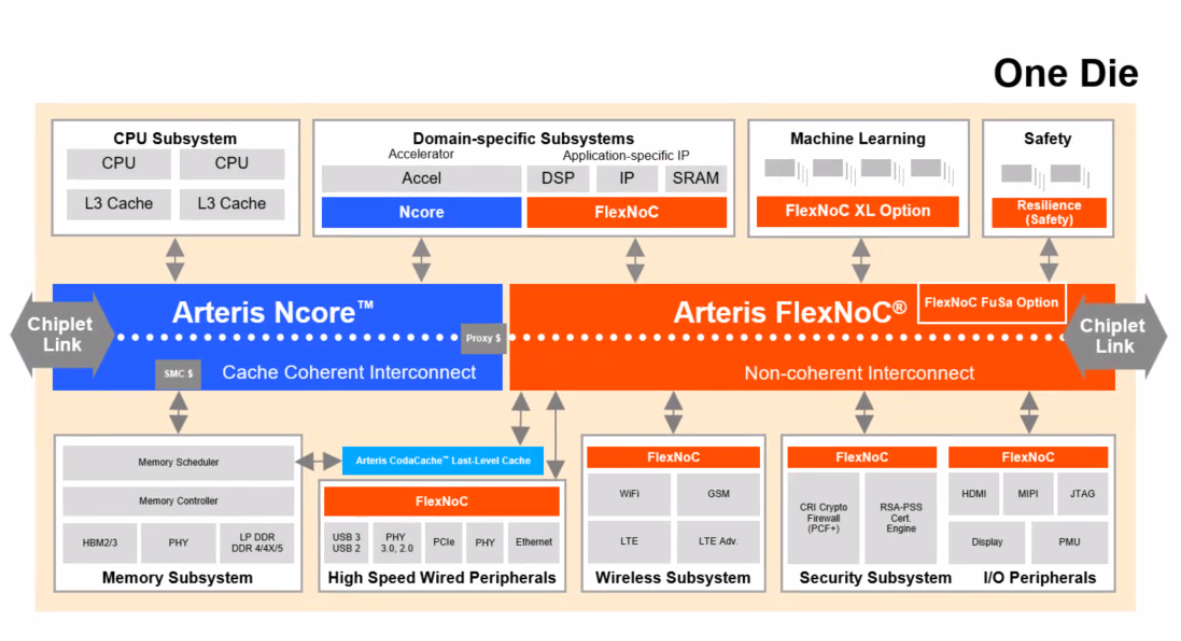

RISC-V コアと NoC の組み合わせはどのようなものになるでしょうか? Arteris の顧客である Tenstorrent は、その可能性を垣間見ることができます。 彼らの最近の焦点は、RISC-V コア、機械学習アクセラレーション IP、および多くのエッジ AI アプリケーションで使用される標準ペリフェラルを組み合わせた再利用可能なチップレットの作成です。 大規模なシングル ダイ実装は、Arteris Ncore キャッシュ コヒーレント インターコネクトと Arteris FlexNoC 非コヒーレント インターコネクトのいくつかのセグメントを使用して、次の図のようになります。

画像提供:アルテリス

スマート メモリ コントローラー (SMC) は、メモリを大量に使用するアプリケーションに高性能のサーバー グレードのメモリ接続を提供します。 名前のない「チップレット リンク」は、より緊密なチップレット統合のために最適化された比較的新しい仕様である UCIe である可能性があります。 新しいサブシステム相互接続が出現した場合、NoC のセクションを適応させる方が、チップ全体の構造全体を解体するよりも管理しやすくなります。

RISC-V コアと NoC を組み合わせることで、リスクと市場投入までの時間が短縮されます

この図が複雑に見えるのは当然ですが、おそらくほとんどの RISC-V アプリケーションは現時点ではそれほど複雑ではないので、次のことを考慮してください。チップレットはすでに統合をさらに高度に推進しています。 現在の高度な RISC-V マルチコア部分は、イノベーションが加速するにつれて、来年のバリュー SoC となるでしょう。

Arteris Ncore および Arteris FlexNoC 開発ツールは実装用に RTL を出力するため、いくつかの利点があります。 物理的な NoC の推定は、EDA ワークフローでは簡単です。 パイプラインのステージ数などの NoC パラメーターの調整も、EDA ツールで数回クリックするだけで行えます。 サブシステム プロトコルを追加するための上記の変更も簡単に実行できます。 「ハイエンドでは、ユーザーは当社の NoC 専門知識にすぐにアクセスできます」とシルマイスター氏は言います。 「ローエンドでは、当社のツールはファーストパスの成功に向けて使いやすく、複雑な相互接続を伴うより野心的な将来のプロジェクトに成長の道筋を提供します。」

RISC-V コアと NoC を組み合わせると、もう XNUMX つの IP ブロックが設計に入り込み、チップ全体に相互接続の再設計の波紋を引き起こすリスクが軽減されます。 また、DIY の相互接続構造と比較して、複雑な SoC 設計の市場投入までの時間を短縮します。 ここでは、帯域幅や電力管理など、NoC の他の利点については説明していませんが、RISC-V 設計における NoC の利点は、多様なプロトコルの組み合わせを考慮するだけでも強力です。

アルテリスのウェブサイトにアクセスしてください NoC の詳細については、 およびその他の製品。

この投稿を共有する:

- SEO を活用したコンテンツと PR 配信。 今日増幅されます。

- PlatoData.Network 垂直生成 Ai。 自分自身に力を与えましょう。 こちらからアクセスしてください。

- プラトアイストリーム。 Web3 インテリジェンス。 知識増幅。 こちらからアクセスしてください。

- プラトンESG。 カーボン、 クリーンテック、 エネルギー、 環境、 太陽、 廃棄物管理。 こちらからアクセスしてください。

- プラトンヘルス。 バイオテクノロジーと臨床試験のインテリジェンス。 こちらからアクセスしてください。

- 情報源: https://semiwiki.com/ip/arteris/336086-pairing-risc-v-cores-with-nocs-ties-soc-protocols-together/

- :持っている

- :は

- :not

- :どこ

- $UP

- a

- 能力

- 上記の.

- 加速

- アクセス

- 熟達した

- 従った

- 越えて

- 追加

- 調整

- 高度な

- 利点

- AI

- 既に

- また

- 野心的な

- an

- および

- 別の

- 回答

- どれか

- 何でも

- 現れる

- です

- 周りに

- AS

- At

- 注意

- 離れて

- 帯域幅

- バー

- BE

- になる

- 利点

- より良いです

- の間に

- ブロック

- ブロック

- バス

- ビジネス

- 事業開発

- 焙煎が極度に未発達や過発達のコーヒーにて、クロロゲン酸の味わいへの影響は強くなり、金属を思わせる味わいと乾いたマウスフィールを感じさせます。

- 缶

- 場合

- 課題

- 変化する

- 変化

- チップ

- 結合

- 商品

- 比べ

- コンプリート

- 複雑な

- 複雑さ

- 計算

- お問合せ

- 接続

- Connections

- 検討

- 見なさ

- 考えると

- 続ける

- 連続的に

- コントローラ

- 基本

- コープ

- 可能性

- カウント

- 作成

- 顧客

- データ

- 定義します

- 定義

- 需要

- 設計

- デザイナー

- デザイン

- 開発

- 開発ツール

- 異なります

- 難しい

- 議論する

- 異なる

- do

- 運転

- 各

- 簡単に

- エッジ(Edge)

- 効率良く

- 出てくる

- 新興の

- end

- 入る

- 全体

- さらに

- 体験

- 専門知識

- エクステンション

- 速いです

- 少数の

- フィールド

- 戦闘

- 名

- フロー

- フォーカス

- 焦点を当てて

- フォロー中

- 軍隊

- 発見

- 率直な

- から

- function

- 未来

- 利得

- ゲイツ

- 与え

- 垣間見ます

- 付与された

- 成長性

- 持ってる

- 助けました

- こちら

- ハイ

- ハイパフォーマンス

- より高い

- しかしながら

- HTTPS

- 画像

- 即時の

- 実装

- in

- 情報

- 革新的手法

- を取得する必要がある者

- 統合

- 相互接続

- 相互接続

- に

- IP

- IT

- ITS

- ただ

- 最新の

- 起動

- 最低

- less

- ような

- 可能性が高い

- LINE

- ライン

- より長いです

- 見て

- のように見える

- LOOKS

- ロー

- 下側

- 管理

- 多くの

- 最大幅

- 五月..

- 多分

- メモリ

- 言及した

- メトリック

- ミックス

- 適度な

- モダン

- 修正

- 他には?

- 最も

- 移動

- ずっと

- の試合に

- しなければなりません

- 新作

- 次の

- いいえ

- 概念

- 今

- 数

- of

- on

- ONE

- 開かれた

- 最適化

- or

- その他

- 私たちの

- 出力

- 平和

- ペアリング

- パラメーター

- 部

- path

- 以下のために

- パフォーマンス

- 周辺

- 周辺機器

- 物理的な

- 選ぶ

- ピック

- パイプライン

- プラトン

- プラトンデータインテリジェンス

- プラトデータ

- プレイ

- 再生

- の可能性

- ポスト

- 潜在的な

- 電力

- 強力な

- プロセッサ

- 製品

- プロジェクト(実績作品)

- プロトコル

- 提供します

- は、大阪で

- 提供

- すぐに

- すぐに

- 最近

- 認識

- 再設計

- 軽減

- 相対的に

- 研究

- 再利用可能な

- 右

- Ripple

- 上昇

- リスク

- ラン

- s

- 言う

- 規模

- シナリオ

- スキーム

- セクション

- 見て

- 見て

- セグメント

- 選択

- いくつかの

- 形状

- シェアリング

- 簡単な拡張で

- から

- スマート

- 溶液

- ソリューション

- 一部

- 洗練された

- 仕様

- ステージ

- 標準

- 簡単な

- 強い

- 構造

- 構造

- それに続きます

- 成功

- そのような

- 超大国

- テクノロジー

- より

- それ

- アプリ環境に合わせて

- ボーマン

- 三番

- この

- 考え

- 三

- 層

- ネクタイ

- タイト

- 時間

- 〜へ

- 今日の

- 一緒に

- 豊富なツール群

- 輸送

- トリガー

- 名前なし

- 更新しました

- つかいます

- users

- 値

- さまざまな

- 変化する

- 、

- 詳しく見る

- vp

- we

- ウェブサイト

- この試験は

- 何ですか

- いつ

- 意志

- 仕事

- ワークフロー

- ゼファーネット