マルチダイ システムは、完全なシステムを作成するために同じパッケージ内に組み立てられたいくつかの特殊な機能ダイ (またはチップレット) で構成されています。マルチダイ システムは、良好な歩留まりで製造可能な方法でパッケージ化されたチップの機能をスケーリングする手段を提供することで、ムーアの法則の減速を克服するソリューションとして最近登場しました。

さらに、マルチダイ システムにより、さまざまな市場セグメントのニーズに合わせたパフォーマンス スケーリング、同じ製品内でさまざまなプロセス ノードを組み合わせて適合させることによる機能ごとのプロセス ノードの最適化、市場投入までの時間の短縮、リスクの低減という点で、製品 SKU の柔軟性が可能になります。

ダイ間の配線密度を高め、ダイ間の高帯域幅トラフィックをサポートするために、パッケージ技術は進化して、シリコン インターポーザー (TSV 付き) またはシリコン ブリッジ、そして最近では再配布層 (RDL) に基づいた新しい高度なパッケージを作成しています。 、ファンアウトおよび HD 基板。

マルチダイ システムを成功させるための重要な側面は、現場での信頼性の高い動作を保証するだけでなく、製造および組み立てのさまざまな段階でシステムのテスト可能性を確保できることです。追加の組み立てステップと、より複雑なバンピングおよびパッケージング技術を使用することにより、マルチダイ システムでは、モノリシック設計の最先端のものを超えるテストおよび信頼性の手順が必要になります。

裸のダイとパッケージ自体は、パッケージに組み立てられる前に、すべての欠陥のあるダイまたはパッケージが検出されていることを確認するために事前テストする必要があります。欠陥のあるダイが組み立て後にのみ検出された場合は、完全なマルチダイ システムを廃棄する必要があり、コストに重大な影響を及ぼします。ネイキッド ダイをテストするプロセスは、Known Good Die (KGD) テストと呼ばれます。

組み立てプロセス自体は、選択したパッケージング技術によって異なります。たとえば、ダイを最初に配置し、その上に相互接続を構築するチップ ファースト テクノロジでは、「正常なパッケージ」のテストができず、相互接続に欠陥がある場合に正常なダイが廃棄される可能性があります。一方、チップラスト技術では、相互接続が個別に構築され、その上にダイが組み立てられるため、組み立て前にパッケージの事前テストが可能になり、良品のダイが廃棄される可能性が低くなります。

マルチダイ システムのテスト容易性ソリューションは、いくつかの側面に分けることができます。

- ダイ内の個々のブロックのテストカバレッジ

- 個々のダイ (裸のダイ) のテスト カバレッジ

- 組み立てられたシステムのテスト (ダイツーダイをカバー)

- ネイキッドダイ内のテストファブリックへのアクセス

- 組み立て後のテストファブリックへの階層的アクセス

この記事では、UCIe IP を活用してマルチダイ システムの信頼性を確保する包括的なテスト容易性ソリューションの利点について説明します。

UCIeインターフェイスのDFT

UCIe インターフェイスの高いテスト カバレッジ ソリューションは、UCIe IP に広範なテスト容易性機能を実装して、ネイキッド ダイ テスト段階で欠陥のあるダイをルートアウトすることによって実現されます。機能には次のようなものがあります。

- すべての合成デジタル回路をカバーするスキャンチェーン

- 専用ブロック固有の BIST 機能

- IO ピンまでの完全な信号チェーンをカバーするループバック組み込み自己テスト (BIST) 機能

- プログラム可能な擬似ランダム バイナリ シーケンス (PRBS) およびユーザー定義のテスト パターン ジェネレーターおよびチェッカー

- 誤ったパスを排除するためのエラー挿入

さらに、パッケージの組み立て後にカバレッジをダイツーダイリンクまで拡張する機能により、次のような高レベルのテストカバレッジを達成できます。

- ファーサイド (ダイツーダイ) BIST ループバック機能

- ダイツーダイリンク BIST

- 境界を分析するための 2D アイ マージン

- レーンごとのテストおよび修復機能

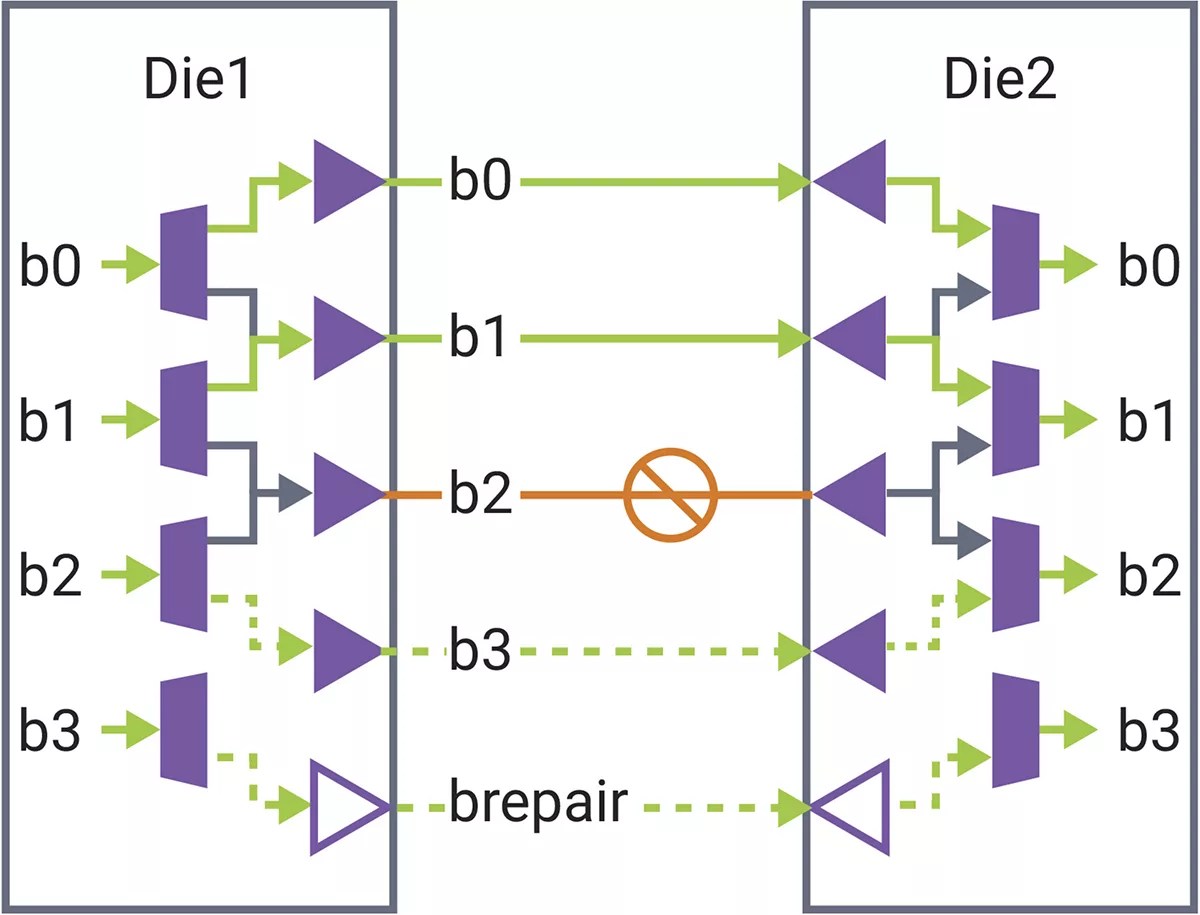

UCIeのテストと修理

高度なパッケージにより、ファインピッチのマイクロバンピングによる高密度配線と、シリコンまたは RDL インターポーザー上の配線が可能になります。組み立てプロセス中に、一部のマイクロバンプ接続が適切に形成されず、破損する可能性があります。 UCIe は、潜在的な歩留り損失を回復する方法で、組み立て後にこれらの接続をテストおよび修復する機能を提供します。

UCIe のテストと修復は、実稼働テスト中およびリンクの初期化時に実行されます。テスト段階では、個々のリンクに欠陥がないか低速でチェックされます。欠陥のあるリンクは、UCIe 標準によって事前に定義された予備リンクにデータを再ルーティングすることによって修復されます。

高度なパッケージを対象とした UCIe 構成には、すべての機能リンクの修復を可能にするために、方向 (TX および RX) ごとに最大 8 つのスペア ピンが含まれています。

- データピン修理用に 2 本の予備ピン、32 本のデータピンの各グループに XNUMX 本のピン

- クロック、クロック、トラックピンの修理用の予備ピン 1 本

- 3 つのスペア ピン、それぞれ有効ピン、サイドバンド データ ピン、クロック データ ピンの修復用

テストと修復の実行は、ダイツーダイ リンク上に有効なトラフィックがない場合に行われます。修復が完了し、リンクが初期化されると、リンクは良好であり、トラフィックは問題なく通過できると想定されます。結果として得られる PHY 構成は PHY 修復署名と呼ばれ、リンクの両端の内部レジスタに保存されます。

経年劣化などによる動作中のマイクロバンプ特性の劣化は、リンクのパフォーマンスに影響を与える可能性があります。これは、ビット誤り率 (BER) の増加、または最悪の場合はデータの損失によってプロトコル レベルで検出されます。その場合、リンクは中断され、新しいテストと修復の手順が実行されることが予想されます。

ただし、一部のアプリケーションでは、ダイツーダイ リンク上のトラフィックの継続性に関して厳しい要件があり、動作中のトラフィックの中断を許容できません。このような場合、テスト容易性ソリューションは、各 UCIe レシーバー ピンにシグナル インテグリティ モニター (SIM) を追加します。

図 1: 内蔵のスペアリンクを使用したリンク修復。

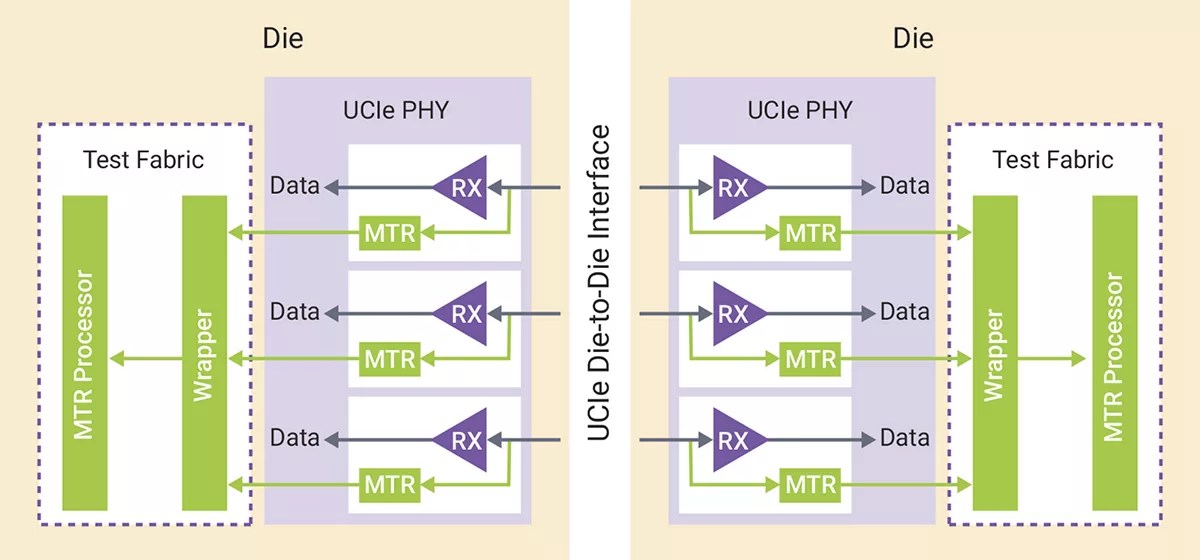

シグナルインテグリティモニター

SIM モニターは、受信機に埋め込まれた小さなブロックです。これらは、通常動作中にレシーバピンの信号を常に感知し、リンクのパフォーマンスに影響を与える可能性のある信号特性の変動を特定したり、リンクがもはや健全ではなく、近い将来壊れる可能性があることを示したりします。

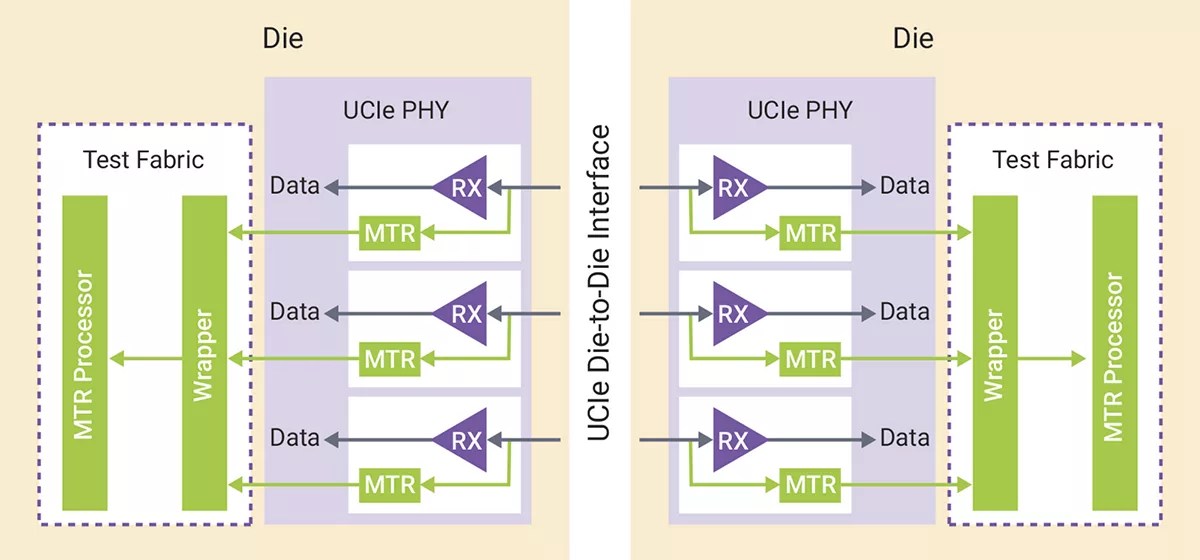

個々のセンサーによって収集されたデータは、インターフェイスの外側にある監視、テスト、修復 (MTR) コントローラーに収集され、さらに処理されます。複数の UCIe リンクからのデータを集約すると、マルチダイ システムの状態を即座に把握でき、リンクの予測メンテナンスが可能になります。

この手順によって特定のリンクが誤動作の危険にさらされていると予測された場合は、トラフィックが中断されなくても、UCIe PHY 修復メカニズムを利用して、そのリンクを無効にし、データを予備リンクの 1 つに再ルーティングできます。

図 2: UCIe リンクのヘルス監視ソリューション。

起床時間の短縮

サーバーの分割やスケーリングなど、ほとんどのダイツーダイ インターフェイスのユースケースのトラフィック パターンは運用中に安定していると想定されていますが、一部のユースケースではトラフィックがバースト的な動作を示す場合があります。このような場合、トラフィックがないときにインターフェイスを低電力モードにして電力を節約することが望ましいです。リンクの再初期化は、テストおよび修復プロセスを回避し、前回の PHY 初期化中に作成された UCIe PHY 修復署名に依存することで高速化できます。

この概念は、ダイの電源が完全にオフになっている状況にもさらに拡張できます。このような場合、PHY 修復署名は PHY から取得され、オンダイの永久メモリ (eFuse またはフラッシュ) に保存されます。メモリには、さまざまな使用例や条件をカバーする複数の署名を保存できる可能性があり、ユーザーの柔軟性がさらに高まります。

UCIe によるダイテストの加速

テスト時間は高価なものです。テスト戦略を階層的に分割して異なるダイのテストを並行して実行することにより、テスト時間を短縮できます。 2 つのダイのテスト インフラストラクチャを階層的に接続することにより、マルチ ダイ システム内の複数のダイにわたって階層を拡張できます。このようなアプローチにより、メイン ダイの単一の JTAG (または同様の) テスト インターフェイスからマルチ ダイ システム内のすべてのダイにアクセスできるようになります。

多くの場合、テスト時間の制限は、テスト ベクトルをダイにロードまたは読み取る時間です。 JTAG インターフェイスは速度のボトルネックになる可能性があります。この制限を克服するために、設計者は、PCI Express (PCIe) や USB などの既存の高速インターフェイスをテスト機器へのインターフェイスとして使用できます。テスト ベクトルとコマンドは、そのインターフェイス用にパケット化され、実稼働テスト フェーズ中にダイ上でパケット化解除されます。

多くのダイには高速インターフェイスがありませんが、テスト中に UCIe ダイツーダイ インターフェイスを使用すると、ダイ間で大規模なテスト ベクトルとコマンドを高速に転送できます。 UCI ダイツーダイ インターフェイスは、ピンの数を増やすことなく、完全なマルチダイ システム全体に高速 DFT アクセスを拡張します。これは、IO および面積が制限されたダイにとって特に重要です。

まとめ

UCIe ダイツーダイ インターフェイスに加えて、これらすべてのテストおよび信頼性向上機能を可能にする共通の分母は、すべての内部ブロックを接続できるテスト、修復、および監視ファブリックです。テスト、修復、およびモニタリングのファブリックは、マルチ ダイ システム内のさまざまなダイにまたがり、次の重要な機能を実現する構造化された階層インフラストラクチャを提供します。

- マルチダイシステム内の個々のダイのテストを管理します

- テストスケジュールを最適化してテスト時間を短縮します

- UCIeインターフェースを介してダイ全体の高速テストアクセスをサポート

- UCIeインターフェイスに組み込まれたヘルスモニタリングインターフェイスから情報を収集し、さらなるシステムレベルの処理を可能にします

- 不揮発性メモリ内の PHY 修復署名の保存を管理します

- もっと見る

シノプシスは、迅速な異種統合のため、EDA や IP を含む、包括的でスケーラブルなマルチダイ システム ソリューションを提供します。安全で信頼性の高いダイツーダイ接続を実現するために、シノプシスは完全な UCIe コントローラー、PHY、および検証 IP ソリューションを提供します。 Synopsys SLM & Test Family の一部として、完全な UCIe モニタリング、テスト、修復 (MTR) ソリューションが STAR Hierarchical System (SHS) ソリューションとともに利用可能です。 MTR ソリューションには、UCIe レーン上の信号品質を測定するためのシグナル インテグリティ モニター、セルフテストのための BIST、冗長レーン割り当てのための修復ロジックが含まれており、SHS ソリューションは業界標準 IEEE 1687、IEEE 1149.1、および IEEE 1838 をサポートする接続ファブリックとして機能します。インターフェース。この完全なソリューションにより、シリコン ライフサイクルのすべての段階で、効率的かつコスト効率の高い UCIe の健全性モニタリングが可能になります。これは、マルチダイ システムの信頼性の高い動作に不可欠です。

<ご参考>

- SEO を活用したコンテンツと PR 配信。 今日増幅されます。

- プラトアイストリーム。 Web3 データ インテリジェンス。 知識増幅。 こちらからアクセスしてください。

- 未来を鋳造する w エイドリエン・アシュリー。 こちらからアクセスしてください。

- PREIPO® を使用して PRE-IPO 企業の株式を売買します。 こちらからアクセスしてください。

- 情報源: https://semiengineering.com/from-known-good-die-to-known-good-system-with-ucie-ip/

- :持っている

- :は

- :not

- :どこ

- $UP

- 1

- 8

- a

- 能力

- 加速する

- 加速された

- アクセス

- 達成する

- 達成

- 達成する

- 越えて

- 添加

- NEW

- 追加

- 高度な

- 後

- 高齢化

- すべて

- 配分

- 許す

- ことができます

- 沿って

- an

- 分析します

- &

- アプローチ

- です

- 記事

- AS

- 側面

- 側面

- 組み立て

- アセンブリ

- 想定される

- At

- 利用できます

- 回避

- 帯域幅

- ベース

- BE

- になる

- さ

- 利点

- の間に

- 越えて

- ブロック

- ブロック

- 両言語で

- ブレーク

- ブリッジ

- 持って来る

- 内蔵

- 内蔵

- by

- 呼ばれます

- 缶

- 場合

- 例

- チェーン

- チェーン

- 特性

- チェック済み

- チップ

- 時計

- 時計

- 商品

- コマンドと

- コンプリート

- 完全に

- 複雑な

- 包括的な

- コンセプト

- 条件

- お問合せ

- 接続する

- Connections

- 接続性

- 絶えず

- コントローラ

- 費用

- コスト効率の良い

- 可能性

- カバレッジ

- カバーする

- 作ります

- 作成した

- 重大な

- データ

- 定義済みの

- 密度

- デザイナー

- デザイン

- 検出された

- 死

- 異なります

- デジタル

- 方向

- 無効

- 分割された

- do

- ダウン

- 原因

- 間に

- 各

- 効率的な

- 排除する

- 埋め込まれた

- 登場

- enable

- 可能

- 有効にする

- 終了

- 強化

- 確保

- 確保する

- 装置

- 等

- エーテル(ETH)

- さらに

- 進化

- 例

- 実行

- 展示

- 既存の

- 予想される

- 高価な

- 表現します

- 伸ばす

- 広範囲

- 余分な

- 目

- ファブリック

- false

- 家族

- スピーディー

- 速いです

- 欠陥のある

- 特徴

- フィールド

- 終わり

- 名

- フラッシュ

- 柔軟性

- フォロー中

- 形成

- から

- function

- 機能的な

- 機能性

- 機能

- さらに

- 未来

- 集まった

- 発電機

- Go

- 良い

- グループ

- ハンド

- 持ってる

- 健康

- 健康

- 助けます

- 階層

- ハイ

- より高い

- しかしながら

- HTTPS

- 識別する

- IEEE

- if

- 影響

- 実装

- 重要

- in

- include

- 含ま

- 含めて

- 増える

- の増加

- 示す

- 個人

- 産業を変えます

- 情報

- インフラ

- 洞察

- インスタント

- 統合

- 整合性

- インタフェース

- インターフェース

- 内部

- 中断された

- に

- IP

- IT

- 自体

- キー

- 既知の

- レーン

- 大

- 法律

- 層

- レベル

- レバレッジ

- 活用

- wifecycwe

- 制限

- LINK

- リンク

- 負荷

- ロジック

- より長いです

- 損失

- 失われた

- ロー

- 製

- メイン

- メンテナンス

- 市場

- 一致

- マッチング

- 最大幅

- 五月..

- 計測

- メカニズム

- メモリ

- モード

- モニター

- モニタリング

- モニター

- 一枚岩

- 他には?

- 最も

- MTR

- の試合に

- しなければなりません

- 近く

- ニーズ

- 新作

- いいえ

- ノード

- 通常の

- 数

- of

- オファー

- on

- ONE

- の

- 操作

- 最適化

- or

- その他

- でる

- 外側

- 克服する

- パッケージ

- パッケージ化された

- パッケージ

- 包装

- 並列シミュレーションの設定

- 部

- 特に

- 渡された

- path

- パターン

- パターン

- パフォーマンス

- 恒久的な

- 相

- ピン

- ピッチ

- プラトン

- プラトンデータインテリジェンス

- プラトデータ

- 可能

- おそらく

- 潜在的な

- :

- 電力

- パワード

- 予測

- 前

- 事前の

- 確率

- 問題

- 手続き

- プロセス

- 処理

- プロダクト

- 生産

- 提供します

- は、大阪で

- 提供

- 品質

- レート

- 読む

- 最近

- 回復する

- 減らします

- 縮小

- レジスタ

- 信頼性

- 信頼性のある

- 修理

- 必要とする

- 要件

- 結果として

- リスク

- ルーティング

- ラン

- RX

- 同じ

- Save

- ド電源のデ

- スケーリング

- スケジューリング

- 安全に

- セグメント

- 選択

- センサー

- シーケンス

- 深刻な

- 仕える

- いくつかの

- すべき

- 側

- シグナル

- 署名

- シリコン

- YES

- 同様の

- 状況

- 遅く

- 減速

- 小さい

- 溶液

- 一部

- スパン

- 専門の

- 特定の

- スピード

- 安定した

- 標準

- 星

- 最先端の

- 手順

- ステップ

- ストレージ利用料

- 店舗

- 保存され

- 戦略

- 構造化された

- 成功

- そのような

- サポート

- 支援する

- システム

- ターゲット

- テクノロジー

- テクノロジー

- 条件

- test

- テスト

- テスト

- それ

- それら

- その後

- そこ。

- ボーマン

- 彼ら

- この

- 介して

- 時間

- 〜へ

- top

- 追跡する

- トラフィック

- 輸送

- 2

- TX

- USB

- つかいます

- 中古

- ユーザー

- さまざまな

- Verification

- 、

- ました

- 仕方..

- webp

- WELL

- この試験は

- いつ

- which

- while

- 意志

- 以内

- 無し

- 最悪

- 産出

- ゼファーネット