「高度に積層された GeSi ナノワイヤ電界効果トランジスタの製造と性能」というタイトルの技術論文が、国立台湾大学の研究者によって発表されました。

要約:

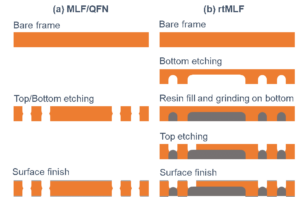

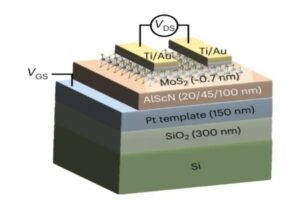

「水平ゲートオールアラウンド電界効果トランジスタ (GAAFET) は、優れた静電気特性と短チャネル制御により、FinFET の代替として使用されています。 高度に積層されたナノワイヤ チャネルは、設置面積が小さいため、これらのデバイスの駆動電流が向上し、全体のトランジスタ密度が向上すると広く考えられています。 ここでは、16 Ge を積層したナノワイヤ FET の製造と特性評価を示します。0.95Si0.05 ナノワイヤと積層型 12 Ge0.95Si0.05 寄生チャネルのないナノワイヤ。 デバイスのオン電流は高くなります (ION) オーバードライブ電圧 (V) でスタックあたり 190 μA (チャネル フットプリントあたり 9400 μA/μm)OV) = ドレイン・ソース間電圧 (VDS) = 0.5 V と高い最大相互コンダクタンス (Gm、最大) V で 490μS (24000μS/μm)DS = 報告されている Si/Ge/GeSi 0.5D nFET の間では 3 V。 トランジスタの性能は、CV/I として表される遅延によって評価できることに注意してください。 トランジスタ I がON が改善されると、スタンダードセルの遅延が低減され、回路の高速動作が可能になります。 閾値以下のスロープの減少と ION/Iオフ 改善は寄生チャネルの除去によって達成されます。 テクノロジコンピュータ支援設計 (TCAD) シミュレーションでは、ラップアラウンド接点はチャネル間の電流差を減らすのに役立ちます。 トランジスタの高さを適切に設計すれば、ゲート遅延も改善できます。」

見つける テクニカルペーパーはこちら。 2023 年 XNUMX 月に発行。

チェン、YR、劉、YC、リン、HC。 他。 高度に積層された GeSi ナノワイヤ電界効果トランジスタの製造と性能。 Commun Eng 2、77 (2023)。 https://doi.org/10.1038/s44172-023-00126-8

関連レディング

デザイナーが GAA について知っておくべきこと

ゲートオールアラウンドは finFET を置き換える予定ですが、それ自体に一連の課題と未知の点が伴います。

- SEO を活用したコンテンツと PR 配信。 今日増幅されます。

- PlatoData.Network 垂直生成 Ai。 自分自身に力を与えましょう。 こちらからアクセスしてください。

- プラトアイストリーム。 Web3 インテリジェンス。 知識増幅。 こちらからアクセスしてください。

- プラトンESG。 カーボン、 クリーンテック、 エネルギー、 環境、 太陽、 廃棄物管理。 こちらからアクセスしてください。

- プラトンヘルス。 バイオテクノロジーと臨床試験のインテリジェンス。 こちらからアクセスしてください。

- 情報源: https://semiengineering.com/highly-stacked-nanowire-fets-to-enhance-drive-current-and-transistor-density/

- :持っている

- :は

- 12

- 16

- 2023

- 3d

- 77

- 私たちについて

- 達成

- AL

- また

- 間で

- および

- です

- 周りに

- AS

- At

- BE

- 信じて

- の間に

- もたらす

- 焙煎が極度に未発達や過発達のコーヒーにて、クロロゲン酸の味わいへの影響は強くなり、金属を思わせる味わいと乾いたマウスフィールを感じさせます。

- by

- 缶

- セル

- 課題

- チャネル

- チャンネル

- コンピュータ

- コンタクト

- コントロール

- 電流プローブ

- 遅らせる

- 実証します

- 密度

- 設計

- デザイナー

- デバイス

- Devices

- 違い

- ドライブ

- 原因

- E&T

- 効果

- 高めます

- 評価

- 速いです

- フィールド

- フットプリント

- ゲート

- 良い

- 高さ

- こちら

- ハイ

- 非常に

- HTTPS

- if

- 改善します

- 改善されました

- 改善

- in

- IT

- ITS

- 知っている

- 主要な

- LIN

- 国民

- 自然

- 必要

- 注意

- 11月

- of

- on

- 操作

- 全体

- 自分の

- 紙素材

- 以下のために

- パフォーマンス

- プラトン

- プラトンデータインテリジェンス

- プラトデータ

- 適切な

- 公表

- 減らします

- 電話代などの費用を削減

- 削減

- 除去

- replace

- 報告

- 研究者

- セッションに

- ショート

- スロープ

- 小さい

- スタック

- 積み上げ

- 標準

- 台湾

- 技術的

- テクノロジー

- それ

- アプリ環境に合わせて

- ボーマン

- タイトル

- 〜へ

- 大学

- 中古

- 電圧

- ました

- we

- which

- 広く

- 無し

- ラップ

- ゼファーネット