プラズマ エッチングはおそらく半導体製造において最も重要なプロセスであり、おそらくフォトリソグラフィーに次いですべての製造作業の中で最も複雑です。 すべての製造工程のほぼ半分は、作業を行うために高エネルギーのイオン化ガスであるプラズマに依存しています。

トランジスタとメモリセルは縮小の一途をたどっていますが、エンジニアは信頼性の高いエッチングプロセスを提供し続けています。

「ナノスケールレベルの精度と適切なコスト構造を備えたチップを持続的に製造するために、ウェーハファブ装置メーカーはプラズマ物理学、材料工学、データサイエンスの限界を押し広げ、必要な装置ソリューションを提供する必要がある」と同社コーポレートバイスプレジデントのトーマス・ボンドゥル氏は述べた。エッチング製品グループのマーケティング担当者 ラムリサーチ。 これが最も顕著に表れるのは、リソグラフィーと連携してウェーハ上に正確で再現可能な形状を作成するプラズマ エッチングです。

このレポートでは、3D デバイスと低予算のバックエンド処理を展望しながら、2D NAND、DRAM、ナノシート FET、および相互接続の主要なエッチング ステップを検証します。 業界はまた、同等の CO を削減するために、より持続可能なエッチング化学を追求しています。2 工場からの排出量。

多くのツールメーカーにとって、プロセスモデリングはエッチングプロセス開発において極めて重要な役割を果たしています。 目標は、ウェーハとマスクのコストを削減しながら、市場投入までの時間を短縮することです。

ラム・リサーチ社のシニア・マーケティング・ディレクター、バレット・フィンチ氏は、「最も注意が必要なステップの一部でのエッチングプロセスの最適化は、完了するまでにXNUMX年以上かかる場合がある」と述べた。 「私たちは最近、一般的なシリコンベースのテストと開発では XNUMX か月かかると予想されていたプロセス シミュレーション作業を XNUMX 週間で完了しました。」

これは、デバイスメーカーにとってマスクとウェーハのコストだけでも数十万ドル、場合によっては数百万ドルに達する可能性があります。

エッチングの基礎

エッチングプロセスはリソグラフィーと連携して行われます。 通常、エッチングの前に膜が堆積されます(エピタキシー、化学蒸着または物理蒸着などによる)。 通常、 CVD フィルムがコーティングされている フォトレジスト そしてパターン化されたパターンを通して露光されます レチクル (マスク)を使用して 光リソグラフィー (248nm または 193nm UV、13.5nm EUV)。 レジスト現像によりパターンが明らかになります。 枚葉式のプラズマ エッチング チャンバーでは、通常、エッチング化学物質とイオンが、フォトレジストが欠けている (ポジ型レジストの) CVD 膜を衝突させて除去します。 エッチングに続いて、レジストアッシング、湿式化学洗浄、および/または湿式エッチングによって残留物が除去されます。

プラズマ エッチング プロセスは、誘電体、シリコン、または導体のエッチングとして大まかに分類できます。 二酸化シリコンや窒化シリコンなどの誘電体はフッ素系ガスを使用して最もよくエッチングされますが、シリコンと金属層は塩素化学物質と最もよく反応します。 基本的に、反応性イオン エッチング、プラズマ エッチング、スパッタ エッチング (イオン ビーム) の XNUMX つのドライ エッチング モードがあります。 エッチング プロセスはすべて、化学反応物質、プラズマ、ウェーハ材料間の複雑な相互作用に関係しています。 RF バイアスが反応性ガスに印加されると、電子と正に帯電したイオンがウェーハに衝突して材料を物理的に除去 (エッチング) し、化学種とフリーラジカルが露出した材料と反応して揮発性の副生成物を形成します。 エッチングは等方性 (垂直方向と水平方向に等しく反応する)、異方性 (垂直方向のみ)、またはその中間のいずれかになります。

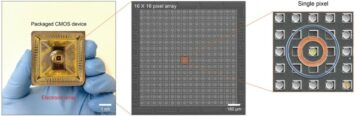

図1:finFETからGAAへの移行は、重要な等方性選択エッチング要件を推進します。 出典:ラムリサーチ

エッチング エンジニアが最も気にする指標は、エッチング速度、プロファイル制御、(ウェーハ全体の) 均一性、およびエッチング選択性です。これらは歩留まりと生産性に影響を与えるためです。 エッチング選択性は、単純に、下層に対するエッチング対象の材料 (SiO など) の除去率です。2 シリコン上で。 エッチング中、フォトレジストをあまり除去しないことも有利である。 しかしその場合、多くの場合、パターンは下層の膜に転写される前にハードマスク (二酸化シリコン、窒化シリコン、SiOC、TiN) に転写されます。

選択性の仕様は 2:1 から最大 1,000:1 (高選択性エッチング) までさまざまです。 新しいノードが登場するたびに、これらの仕様は厳しくなります。 「今後 30 年以内に高 NA EUV が通常の EUV に取って代わり始めており、焦点ははるかに低くなっているため、厚いフォトレジストを露光することはできなくなります。厚さとは 2 ナノメートルを意味します」と、同社のドライエッチング R&D エンジニア、フィリップ・ベザール氏は述べています。アイメック。 「しかし、下では同じ膜厚をパターン化する必要があります。 つまり、1:10 ではなく 1:4 に近づける必要があるという意味で、はるかに高い選択性が求められています。これは突然 5 倍から XNUMX 倍の選択性の向上です。」

概念実証 (POC) から大量生産 (HVM) まで

Bézard 氏は、エッチング プロセス開発の XNUMX つの段階について説明します。

- エッチングを実行するためにどのようなエッチャー、ガス、補助層などが必要かを決定する。

- XNUMX枚のウェーハ全体で均一なプロセスを実現し、仕様内で膜を完全に除去する性能を実証。

- HVM で数千枚のウェーハにわたってプロセスを高い歩留まりとほとんどドリフトで繰り返す方法を決定します。

通常、熟練したエッチングおよび統合エンジニアが開発の最初の XNUMX フェーズを担当します。 第 XNUMX フェーズでは再びエンジニアリングの専門知識が活用される可能性がありますが、機械学習が役立つ可能性があります。

「機械学習とデータ分析は一般的に、第 XNUMX フェーズでのみ役に立ちます」と彼は言いました。 「大量のデータにアクセスでき、相互作用する何百万もの小さくて単純なものを理解できるため、非常に強力です。 したがって、人間の脳がこれを理解しようとするのは非常に困難ですが、コンピュータプログラムにとっては容易です。 しかし、新しいアプリケーション、新しい素材のエッチング、または新しい統合の場合、人間を超える改善は見られません。」

フェーズ XNUMX では数千枚のウェーハが使用されるため、ML の使用は製造コストにも関係します。フェーズ XNUMX とフェーズ XNUMX で使用されるものより少なくとも XNUMX 桁多くなります。

Lam Research のエッチング製品グループのシニア ディレクターである Barrett Finch 氏は、新しいプロセス パスファインディングを、公称プロセス フローとレイアウトから概念実証を取得し、ウェハー上に XNUMX つ以上の動作デバイスを開発することであると説明しています。 次に、この POC は工場の製品開発チームに転送され、プロセスをスケールアップして歩留まりを向上させます。

「名目上の概念実証を実行可能な収益性の高い製品に変えるのに必要な作業量は過小評価されることが多く、これが収益性に大きなギャップを生み出します」とフィンチ氏は述べた。 「プロセスウィンドウモデリングは、研究開発経路探索の初期段階にファブのバリエーションを導入することで、このギャップを埋めようとします。」 彼は、仮想 DOE と多数のプロセス パラメーターにわたるモンテカルロ ベースの解析により、予想される変動をシミュレートすることで POC をテストすることを提案しています。

「プロセス ウィンドウ モデリングは、『デバイスのパフォーマンスと歩留まりを最小限にするにはどの CD または変動レベルを維持する必要があるか?』という質問に答えることができます。」 私たちは数日間で 1 万枚以上の仮想ウェーハを使用した仮想プロセス ウィンドウ テストを完了しましたが、これは現実には不可能です。」と彼は言いました。

複数のパラメータがエッチング速度、プロファイル、選択性に影響します。 重要なのは温度です。 「エッチング処理における熱効果の影響は、当社のお客様がエッチング速度、選択性、エッチングプロファイルを制御する際に目に見えています。 これらのパラメータはすべて、デバイスの歩留まりとファブの生産性の両方に影響を与える可能性があります」と、Lam Research の半導体プロセスおよび統合エンジニアリング担当シニア マネージャーのベンジャミン ヴィンセント氏は述べています。 同氏は、プロセスステップに複数の可能な構成がある場合(プロセス空間が大きい場合)、またはステップからの下流の結果が非常に予測不可能な場合に、シミュレーションが特に役立つ可能性があると主張しています。

「エッチングプロセスはウェーハの表面温度に依存しており、これは熱伝導、イオン衝撃エネルギー、表面反応、プラズマ放射熱流束などのいくつかの熱流束に依存します」と、エスジー・テクノロジーズの製品マーケティングマネージャー、アレックス・ゲルムーシュ氏は述べています。ラムリサーチカンパニー。 「その結果、ウェハ表面の温度変化を正確に描写するには、プラズマ モデルにこれらの物理的特徴をすべて組み込む必要があります。 プロセス シミュレーション ソフトウェアは、さまざまなエッチング属性をモデル化できるため、より良いエッチング結果をより迅速に得ることができ、お客様の生産量の増加や歩留まりの最適化の能力を加速できます。」

エッチングプロセスの正確なタイミング

より緻密な形状とより薄い膜では、他の動作パラメータをうまく制御しながらエッチング速度のバランスを取る必要があります。

「デザインルールの縮小に伴い、多くのエッチングプロセスは、電力、圧力、化学物質、温度といったすべての反応入力を高精度に制御する必要がある非常に高速なプラズマエッチングプロセスステップに移行している」とフィンチ氏は述べ、プラズマの最適化を目指す傾向もあると指摘した。パルス動作により特定のイオン対中性比を生成し、副生成物を一掃します。 「このような状況の高度なモデリングは、デバイスのさらなるスケーリングを可能にするために重要です。」

エッチング システムのメーカーは、次のノードの開発を加速したり、歩留まりを向上させたりするために、しばらくの間モデリング ソフトウェアを使用してきました。 プロセスとそのすべての変数が非常に複雑であることを考えると、これは驚くべきことではありません。

「次のノード技術を開発する際に、考えられるすべてのプロセス実験を実行するのに十分な時間やウェハがまったくありません」とフィンチ氏は述べています。 「エッチング装置の設定の組み合わせの数は数百万、あるいは数十億にも達する可能性があり、あらゆるプロセスの可能性を利用して強引にウェーハを開発することはまったく不可能です。」

もちろん、すべての良好なモデルは実際のチップ上で検証されます。 「正確なモデルは予測的である必要があり、ユーザーが解決したい対象となる問題を解決する必要があります」とフィンチ氏は述べています。 「シミュレーション作業に基づいてプロセスや設計の変更が推奨されるたびに、実際のファブのデータは推奨の結果を反映する必要があります。 私たちの場合、モデルベースの結果を使用してプロセス変更の影響を正確に予測し、プロセスや技術開発の困難な問題を迅速に解決することができました。」

ツールサプライヤーも、ラインをより緊密に統合し、かつては XNUMX マスクレベルのプロセス (XNUMX つのリソグラフィーステップ) であったプロセスを XNUMX つに変換して、プロセスの簡素化とコスト削減を図る高度なエッチングプロセスにも取り組んでいます。

「企業は既存のハードウェアを適応させてスイスアーミーナイフの装備をさらに強化するのではなく、先端から先端までの問題に対処する新しいシステムなど、用途に特化したテクノロジーを導入しています」とベザール氏は述べた。 目的は、互いに向かい合う XNUMX 本のラインを近づけることで、現在これにはライン パターニング ステップとそれに続くマスクのカットが必要です。 「アプライド マテリアルズなどが導入しているのは、水平方向に直接エッチングする方法です。」 このようなプロセスでは、ビアホールが広がる可能性もあります。

ナノシートFETのエッチングステップ

最も重要なエッチング手順は、 ナノシート プロセス フローには、ダミー ゲート エッチング、異方性ピラー エッチング、等方性スペーサー エッチング、およびチャネル解放ステップが含まれます。 [1] シリコンと SiGe の交互層によるプロファイル エッチングは異方性であり、フッ素化化学物質を使用します。 内部スペーサーのエッチング (くぼみ) とチャネルのリリースのステップは、極めて低いシリコン損失で SiGe を除去するように最適化されています。

チャネルのリリース手順は重要です。 「ナノシートの放出には、非常に高い選択性が求められます」とベザール氏は言う。 「ほとんどのナノシートはシリコンであり、次にシリコンゲルマニウム、そしてシリコンです。 交互のレイヤーがあるので、もう一方をまったく変更せずに一方を削除する必要があります。」 いくつかの出版物では、単一のエッチング ステップによって引き起こされる構造への応力を軽減するために、複数ステップの SiGe エッチングを実行することについて論じています。

プロセスの次は、自己整合コンタクトの形成です。 「ここで私たちがやろうとしているのは、基本的に二酸化シリコンをエッチングすることであり、窒化シリコンに触れたり凹ませたりすることはありません。 現在の仕様は、たとえば 3nm の凹みですが、人々は損失ゼロを求めています」とベザール氏は述べています。 「この場合、選択性という言葉さえ使っていません。 私たちはただ休み時間について話しているだけで、休み時間はゼロです。」

3D NAND

3D NAND フラッシュの増加に伴い、層の数は増加し続けており、将来的には複数のスタック層の採用が必要となり、最終的にはスタックされたデバイスの垂直ストリングが作成されます。 「また、ビット密度を増加し続けるために層の数が増えるにつれて、ワード線のピッチや層の垂直/Zピッチを拡大しようとする動きが活発になっています」と技術スタッフの上級メンバーであるロバート・クラーク氏は述べています。のテクノロジーディレクター TEL。 「プロセスの観点から見ると、継続的なスケーリングに必要な、これまで以上に高いアスペクト比とこれまでにない小さな限界寸法に対応するために、エッチングおよび堆積プロセスは継続的な改善が必要になります。」

クラーク氏は今後の変化について説明した。 「複数の層を備えたチャージトラップデバイスの高度なノードに目を向けると、ゲートスタックのエンジニアリングでは、ゲート長を短くし、セルあたりのレベルを増やし、プログラミング効率を向上させる必要があります。これには、潜在的にはHigh-k材料の採用が必要です。 将来的には、ポリ Si チャネルに代わるより高い導電率のチャネルも必要になる可能性があります。」と彼は言いました。

3D NAND で最も重要なエッチングの 100 つは、多層酸化物窒化物スタック (200 層以上) を貫通する約 10nm の穴の深いエッチングであり、深さは最大 XNUMXµm になる場合があります。 Imec の Bézard 氏は、このエッチング工程は特にコストがかかると述べた。

「差動充電効果と呼ばれる物理現象が発生します」と彼は言いました。 「プラズマには、かなり単純化するために電子、イオン、中性種が存在します。 電子はあらゆる方向に移動しますが、イオンは表面に対して垂直に加速されます。 つまり、穴の底にはプラスの電荷があり、穴の上部にはマイナスの電荷があり、入ってくるイオンを反発しようとする電場が生じます。」

その結果、トレンチを完全にエッチングするには高い電力レベルが必要となります。 「私たちはアークを発生させずに 30 ~ 50 ギガワットの電力を維持しようとしているので、チャックは非常によく磨かれ、よく製造されている必要があります。」と彼は言いました。

また、深いエッチングは応力を誘発するため、特に多層 NAND 製造ではウェーハの薄化、正確な位置合わせ、次の層へのハイブリッド ボンディングが必要になるため、この応力を最小限に抑える必要があります。

その他のプロセス

すべてのチップメーカーが EUV リソグラフィーを必要とする最先端のチップを製造しているわけではありません。 多くのファブは、193nm リソおよびエッチング プロセスを拡張しています。

「最近導入を開始した高温SOC材料は、CVD層またはマスクの下層として使用されるかどうかにかかわらず、パターニング能力を拡張し、高温に耐えることができます」と、半導体製品多様化担当ディレクターのブライアン・ウィルバー氏は述べています。 ブリューワーサイエンス.

BEOL 拡張 最も緻密な金属配線では、デュアルダマシン集積方式から銅以外の配線のサブトラクティブ堆積およびエッチングへの劇的な移行が予想されます。 ここでは、ルテニウムとモリブデンという XNUMX つの金属が最も徹底的に開発されました。 ただし、モリブデンはエッチング中に酸化する可能性が高いため、デュアルダマシン方式との互換性が高くなります。 ルテニウムは貴金属であるため、同様の腐食の問題はありませんが、より高価です。

デバイスの構造も許容できなくなってきています。 エッジ配置エラー。 TELのクラーク氏によると、層から層へ、またビアと配線の間で自己整合を実現するための新しいスキームが必要になるという。 「最初の実装は、おそらくDRAMの埋め込みワードラインや、より高い熱安定性とより低い抵抗率またはライナーレスメタルが必要とされるロジック用の狭ピッチMOLメタル層のようなものになるでしょう。」

次世代の開発

長期的には、業界はデバイスをバックエンドの相互接続層に統合するために、熱バジェットの低いバックエンド プロセス (300 ℃ より 400 ℃ に近い) に移行するのが理想的です。

TEL のクラーク氏は、「業界はデバイスをより多くのレイヤーに構築し始めることが本当に必要です」と述べています。 「つまり、BEOL の熱バジェットで BEOL 内にメモリとロジック デバイスを構築する必要があるということです。」

これまでのところ、半導体酸化物を使用して作成されたデバイスは、メモリデバイスをロジック BEOL フローに統合する場合、または DRAM のメモリ アレイ上に CMOS アレイを構築する場合の両方において、有望であるように見えます。

もう 2 つの大きな変化には XNUMXD 材料の統合が含まれており、研究機関や大手チップメーカーはすでにテストを開始しています。 二硫化タングステンや二硫化モリブデンなどの材料のエッチングプロセスが検討されています。 フィルムは材料の XNUMX つの単層で構成されているため、それらを統合する製造プロセスの開発は非常に困難です。

3つの柱

チップメーカーと材料サプライヤーは、炭素排出量を削減するために代替化学物質を追求しています。 エッチングの主な原因は、地球温暖化係数の高いフッ素系ガスです。

imecのベザール氏は、「問題となるPFOS(パーフルオロオクタンスルホン酸)が存在する理由は、分子が非常に安定しているためだ」と述べた。 「大気中の光や化学反応では分解するには不十分です。」

同氏は、酸素含有量が高い多くの代替ガス混合物は解離しやすく、GWP が低いと述べた。 「しかし、どの候補者も、スタートするには同等かそれ以上のパフォーマンスを発揮する必要があります。」

しかし、持続可能性は特にエッチングや蒸着の課題ではありません。 これは、リソグラフィーからパッケージングに至る総合的な業界の課題であり、新しい材料の影響がデバイス処理全体に影響を与えます。

参照

1. K.ダービーシャー、 「次世代トランジスタは何が違うのか」、半導体工学、20 年 2022 月 XNUMX 日。

関連ストーリー

次世代チップ向けに選択性の高いエッチングが展開

3D構造を製造するには、除去されるものとウェーハ上に残るものを原子レベルで制御する必要があります。

- SEO を活用したコンテンツと PR 配信。 今日増幅されます。

- プラトアイストリーム。 Web3 データ インテリジェンス。 知識増幅。 こちらからアクセスしてください。

- 未来を鋳造する w エイドリエン・アシュリー。 こちらからアクセスしてください。

- PREIPO® を使用して PRE-IPO 企業の株式を売買します。 こちらからアクセスしてください。

- 情報源: https://semiengineering.com/etch-processes-push-toward-higher-selectivity-cost-control/

- :持っている

- :は

- :not

- :どこ

- $UP

- 000

- 1

- 10

- 13

- 20

- 2022

- 2D

- 2Dマテリアル

- 30

- 3d

- 50

- a

- 能力

- できる

- 私たちについて

- 加速する

- 加速された

- アクセス

- 対応する

- こちらからお申し込みください。

- 従った

- 正確な

- 正確にデジタル化

- 越えて

- 実際の

- 住所

- 養子縁組

- 高度な

- 有利

- 影響を及ぼす

- 再び

- 目指す

- アレックス

- すべて

- 許可

- 既に

- また

- 代替案

- 量

- an

- 分析

- &

- 別の

- 回答

- どれか

- 現れる

- 申し込み

- 特定用途向け

- 適用された

- です

- 軍

- 配列

- AS

- 側面

- アシスト

- At

- 雰囲気

- 属性

- 離れて

- バックエンド

- ベース

- 基本的に

- BE

- ビーム

- なぜなら

- になる

- き

- 開始

- さ

- 以下

- ベンジャミン

- BEST

- より良いです

- の間に

- バイアス

- ビッグ

- 億

- ビット

- 両言語で

- ボトム

- 境界

- 脳

- ブレーク

- ブライアン

- 強引な

- 予算

- 予算

- 建物

- 内蔵

- 焙煎が極度に未発達や過発達のコーヒーにて、クロロゲン酸の味わいへの影響は強くなり、金属を思わせる味わいと乾いたマウスフィールを感じさせます。

- by

- 呼ばれます

- 缶

- 候補者

- カーボン

- 炭素排出量

- これ

- 場合

- 例

- CD

- 細胞

- 挑戦する

- 挑戦

- 室

- 変化する

- 変更

- チャネル

- チャンネル

- チャージ

- 荷担した

- 課金

- 充電

- 化学物質

- 化学品

- 化学

- チップ

- クリーニング

- 閉じる

- 密接に

- クローザー

- 組み合わせ

- 企業

- 会社

- 互換性のあります

- コンプリート

- 記入済みの

- 複雑な

- 複雑さ

- コンピュータ

- コンセプト

- 条件

- 導電率

- 導体

- 見なさ

- 定数

- コンタクト

- コンテンツ

- 続ける

- 継続します

- 続ける

- コントロール

- 銅

- 企業

- 費用

- コスト削減

- コスト

- 可能性

- ここから

- 作ります

- 作成します。

- 作成

- 重大な

- 電流プローブ

- 現在

- Customers

- カット

- データ

- データ分析

- データサイエンス

- 日

- 深いです

- 配信する

- 密度

- 依存

- 記載された

- 設計

- 発展した

- 開発

- 開発

- デバイス

- Devices

- 異なります

- 難しい

- 大きさ

- 方向

- 直接に

- 取締役

- 議論する

- 多様化

- do

- ありません

- ドル

- ダウン

- 劇的に

- ドライブ

- 間に

- 各

- 早い

- 簡単に

- 効果

- 効果

- 効率

- どちら

- 電気

- 電子

- 排出量

- 有効にする

- エンジニア

- エンジニアリング

- エンジニア

- 十分な

- 平等に

- 装置

- 装備

- 同等の

- 特に

- 本質的な

- 本質的に

- 等

- さらに

- 最終的に

- あらゆる

- 厳しい

- 試験

- 実行します

- 既存の

- 予想される

- 高価な

- 実験

- 専門知識

- 露出した

- 延伸

- 非常に

- 向い

- 遠く

- スピーディー

- 速いです

- 特徴

- 少数の

- フィールド

- フィギュア

- 膜

- 名

- フラッシュ

- フロー

- 流れ

- フォーカス

- 続いて

- フォロー中

- 強

- フォーム

- 形成

- フォワード

- 4

- 無料版

- から

- 完全に

- さらに

- 未来

- ギャップ

- GAS

- 生成する

- 取得する

- 与えられた

- グローバル

- 地球温暖化

- 目標

- 良い

- 素晴らしい

- グループ

- 成長する

- 育ちます

- 半分

- ハンドル

- ハード

- Hardware

- 持ってる

- he

- 役立つ

- こちら

- ハイ

- 高利回り

- より高い

- 非常に

- ホール

- 穴

- 包括的な

- 水平な

- 住宅

- 認定条件

- しかしながら

- HTTPS

- 人間

- 人間

- 何百

- ハイブリッド

- i

- 影響

- 不可能

- 改善します

- 改善されました

- 改善

- in

- include

- 含めて

- 入ってくる

- 組み込む

- の増加

- 産業を変えます

- 入力

- を取得する必要がある者

- 統合する

- 統合

- 統合

- 相互作用

- 相互作用

- 相互接続

- に

- 導入

- 問題

- IT

- ITS

- JPG

- ただ

- キー

- ラム

- 大

- より大きい

- 層

- 層

- レイアウト

- 主要な

- 学習

- 最低

- レベル

- レベル

- 生活

- ような

- 可能性が高い

- LINE

- ライン

- リソ

- 少し

- ロジック

- より長いです

- 見て

- 損失

- たくさん

- ロー

- 機械

- 機械学習

- 製

- メイン

- 維持する

- make

- メーカー

- 作成

- マネージャー

- 製造された

- メーカー

- 製造業

- 多くの

- 市場

- マーケティング

- マーケティング部長

- mask

- 材料

- 材料

- 最大幅

- 五月..

- 意味する

- 手段

- メンバー

- メモリ

- 金属

- 金属

- メトリック

- かもしれない

- 百万

- 何百万

- 最小

- 行方不明

- モデリング

- モデル

- モード

- 商船三井

- 分子

- ヶ月

- 他には?

- 最も

- 移動する

- ずっと

- の試合に

- ほぼ

- 必要

- 必要とされる

- ニーズ

- 負

- 普通

- 新作

- 次の

- いいえ

- ノーブル

- ノード

- 今

- 数

- 10月

- of

- 頻繁に

- on

- かつて

- ONE

- の

- オペレーティング

- 業務執行統括

- 最適化

- 最適化

- 最適化

- or

- 注文

- その他

- その他

- 私たちの

- でる

- が

- 酸素

- 包装

- パラメータ

- 特定の

- 特に

- パターン

- のワークプ

- 実行する

- パフォーマンス

- 実行

- おそらく

- 視点

- 相

- 現象

- フィリップ

- 物理的な

- 物理的に

- 物理学

- 柱

- ピッチ

- 極めて重要な

- プラズマ

- プラトン

- プラトンデータインテリジェンス

- プラトデータ

- 演劇

- PoC

- 正の

- の可能性

- 可能

- おそらく

- 潜在的な

- :

- 電力

- 強力な

- 正確な

- 精度

- 予測する

- 社長

- 圧力

- 問題

- 問題

- プロセス

- ラボレーション

- 処理

- 作り出す

- プロダクト

- 製品開発

- 生産

- 生産性

- 製品

- プロフィール

- 対応プロファイル

- 収益性

- 演奏曲目

- プログラミング

- 有望

- 証明

- 概念実証

- 出版物

- プッシュ

- 質問

- すぐに

- R&D

- ランプ

- 範囲

- レート

- 価格表

- 比

- リーチ

- 反応する

- 反応

- 反応

- リアル

- 実生活

- 理由

- 最近

- おすすめ

- 推奨される

- 減らします

- 縮小

- 削減

- 反映する

- レギュラー

- リリース

- 信頼性のある

- 頼る

- 除去

- 削除します

- 削除済み

- 除去

- 繰り返し可能

- 繰り返される

- replace

- レポート

- 必要とする

- の提出が必要です

- 要件

- 必要

- 研究

- 結果

- 結果

- 明らかに

- 右

- ROBERT

- 職種

- ロール

- 大体

- ルール

- ラン

- 前記

- 同じ

- 言う

- 規模

- スケーリング

- スキーム

- 科学

- 求める

- 見て

- 選択的

- 半導体

- シニア

- センス

- 設定

- いくつかの

- シフト

- すべき

- シリコン

- 簡単な拡張で

- 簡素化する

- 単に

- 熟練した

- 小さい

- So

- ソフトウェア

- ソリューション

- 解決する

- 一部

- どこか

- ソース

- スペース

- 特定の

- 仕様

- スペック

- スピード

- 安定性

- 安定した

- 積み上げ

- スタック

- スタッフ

- ステージ

- start

- 開始

- 手順

- ステップ

- まだ

- ストレス

- 構造

- 続いて

- かなりの

- そのような

- 突然の

- 十分な

- 提案する

- サプライヤー

- 表面

- 驚き

- 3つの柱

- 持続可能な

- スイープ

- スイス

- システム

- 取る

- 取得

- Talk

- 対象となります

- チーム

- 技術的

- テクノロジー

- テクノロジー

- 技術開発

- 期間

- test

- テスト

- テスト

- より

- それ

- 未来

- アプリ環境に合わせて

- それら

- その後

- そこ。

- サーマル

- ボーマン

- 彼ら

- 物事

- 三番

- この

- 徹底的に

- 数千

- 三

- 介して

- 層

- タイト

- 時間

- タイミング

- 〜へ

- 一緒に

- トン

- TONE

- あまりに

- top

- touch

- に向かって

- 転送

- 最適化の適用

- 遷移

- トレンド

- 試します

- 2

- 典型的な

- 一般的に

- 根本的な

- 予測できない

- に

- 上向き

- us

- つかいます

- 中古

- ユーザー

- 活用する

- 検証

- 垂直

- 垂直に

- 非常に

- 、

- 実行可能な

- 副会長

- ヴィンセント

- バーチャル

- 欲しいです

- 望んでいる

- ました

- 仕方..

- we

- ウィークス

- WELL

- この試験は

- いつ

- かどうか

- which

- while

- 全体

- なぜ

- 意志

- 以内

- 無し

- Word

- 仕事

- ワーキング

- 作品

- でしょう

- 年

- 年

- 産出

- 収穫

- 収量

- 貴社

- ゼファーネット

- ゼロ