フリップチップパッケージングにおける相互接続密度の向上を可能にする新しいバンプ構造が開発されていますが、それらは複雑で高価であり、製造がますます困難になっています。

ピン数が多い製品の場合、 フリップチップ [1] パッケージは、ダイ領域全体を相互接続に利用するため、長い間人気のある選択肢でした。 このテクノロジーは IBM の C1970 (制御コラプス チップ接続) を皮切りに 4 年代から使用されてきましたが、実際に広く使用されるようになったのは 1990 年代になってからです。

それ以来、メモリ、ハイパフォーマンス コンピューティング、およびモバイル コンピューティング デバイスに必要な電力と信号接続密度の増加に対応するために、バンプ テクノロジが進化してきました。 この需要を満たすには、より小さなバンプピッチを可能にする新しい相互接続技術が必要であり、現在生産されています。

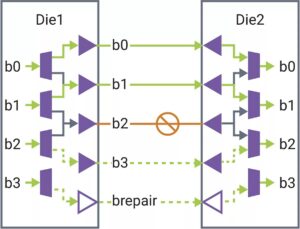

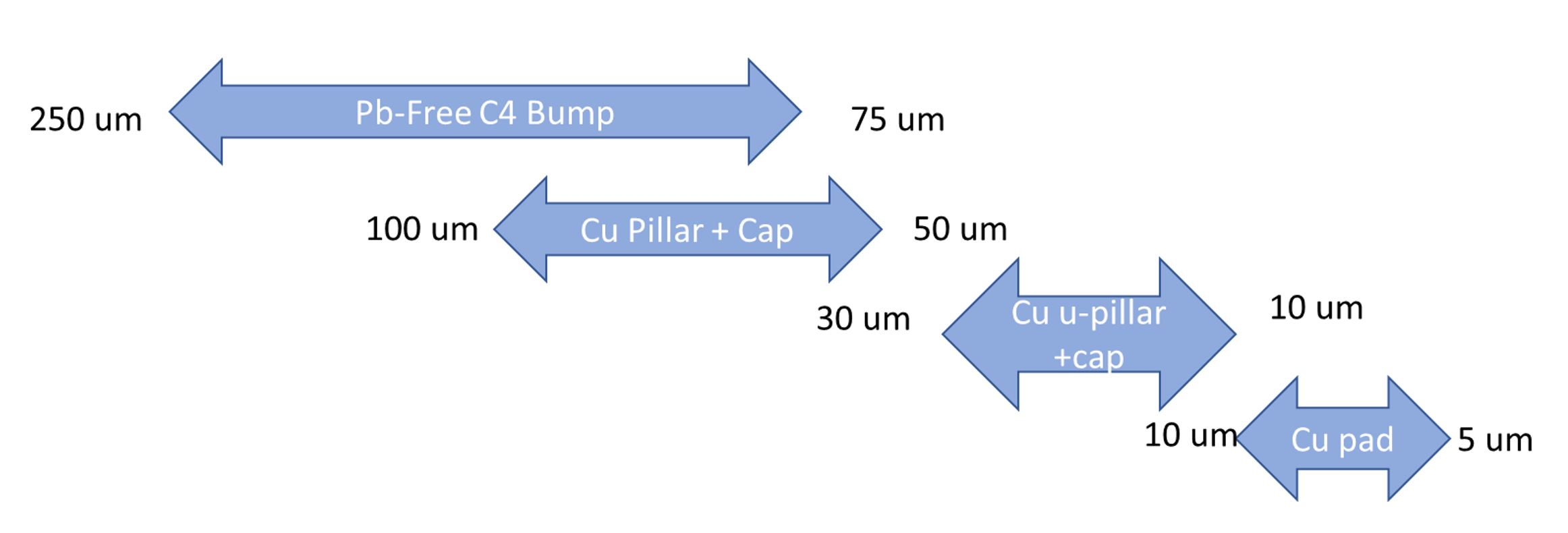

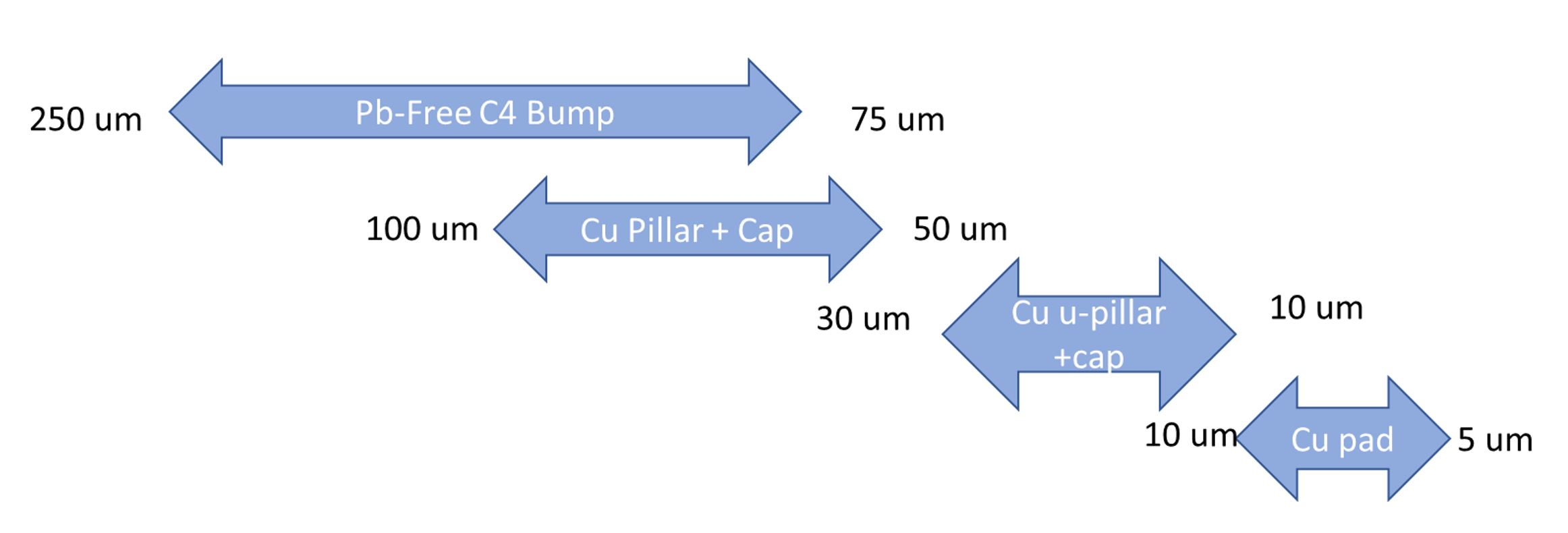

時間の経過とともにフリップチップ相互接続のロードマップは、鉛フリーバンプから銅ピラー、そして銅マイクロバンプへと進みます。 ピッチサイズは縮小し続けており、その結果、バンピングやボンディングに関して製造上の課題が生じています。

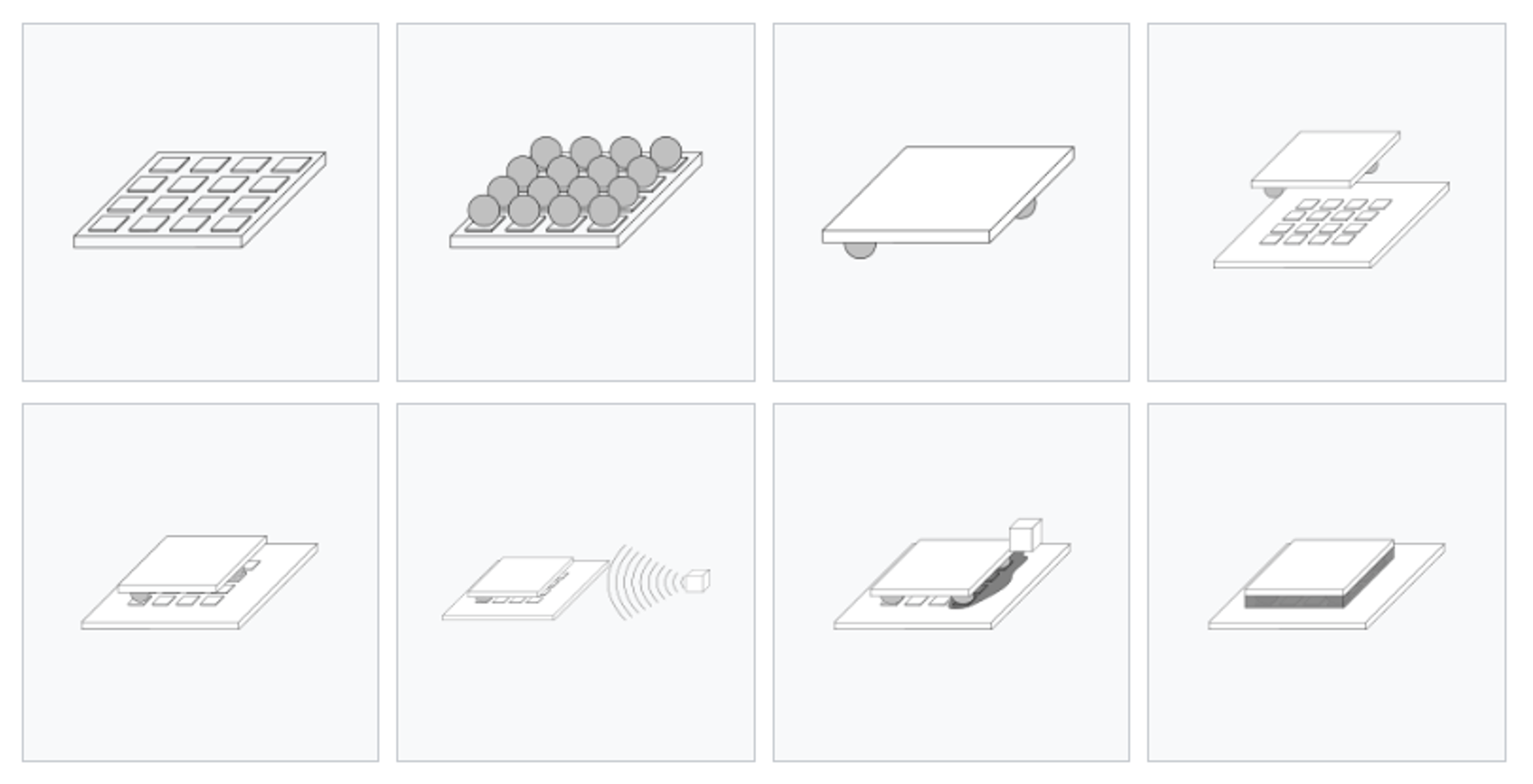

図 1: フリップチップ技術のピッチ範囲。 出典: A. Meixner/半導体工学

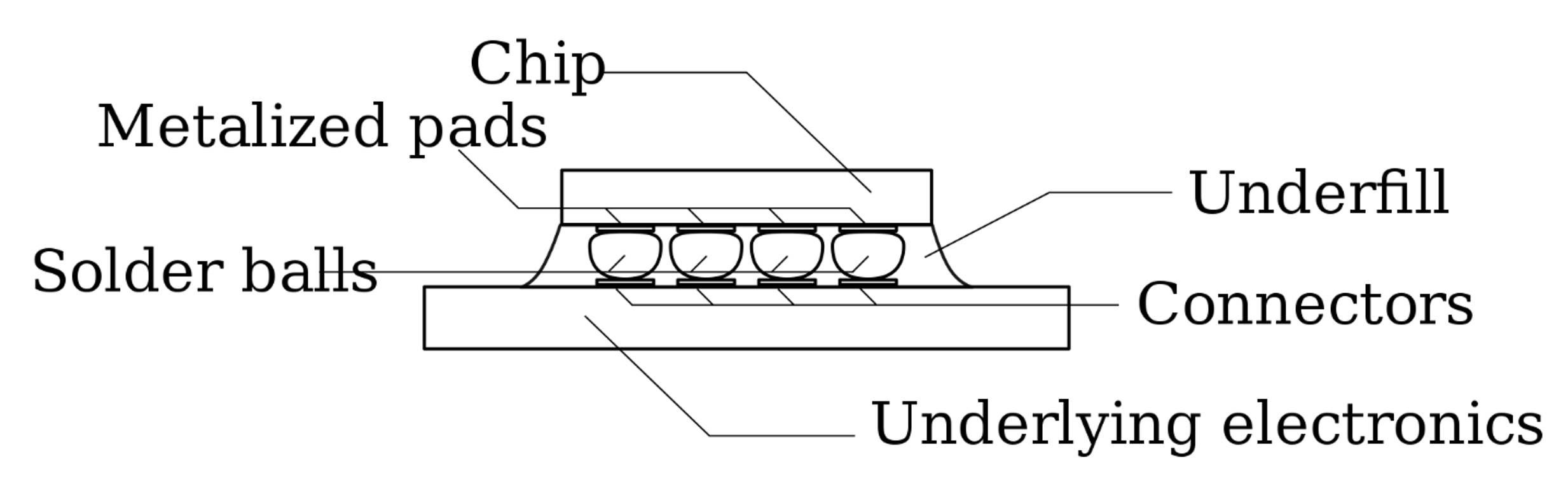

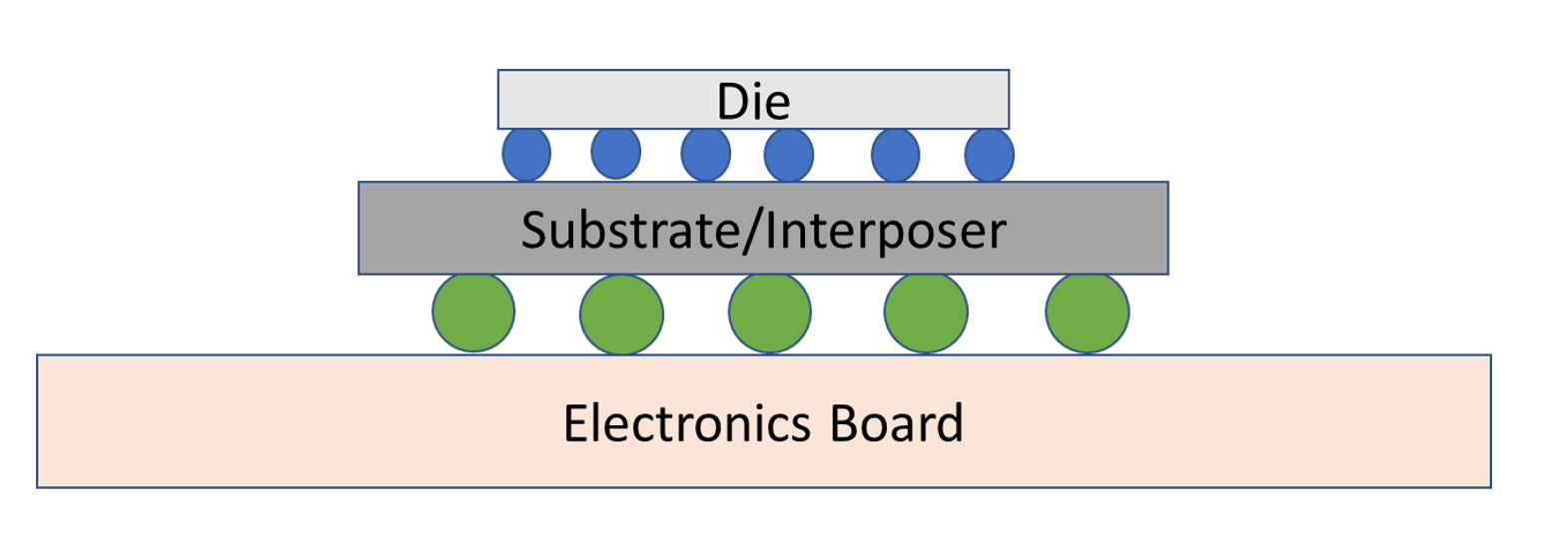

図 2: フリップチップ コンポーネント。 ソース: Wikipedia

「250ミクロンピッチ以下のフリップチップ分野では、元々は錫と鉛のバンプでしたが、大きな動きの100つは鉛フリー化でした。 しかし、250 ミクロン以下に達し始めると、より多くの銅ピラーが見られ始めますが、XNUMX ミクロンまでの銅ピラーが見られるため、重複はあります」と、同社のシニア プロセス エンジニア、ジェフ シェーファー氏は述べています。 プロメックスインダストリーズ。 「250 ミクロンのピッチでは、バンプ サイズまたは銅ピラーの直径は 130 ミクロンになります。 ピッチが 100 ミクロンになると、直径は 80 ミクロンになります。 私が見た中で最も小さいものは、ピッチが 62.5 ミクロン、ピラーが 40 ミクロンのものです。 すぐに50ミクロンのピッチが見え始めると思います。」

基本的なフリップチップ プロセスは、回路製造後に、I/O に接続するための金属パッドがダイ表面に作成されるときに始まります。 次にウェハバンピングが行われ、各パッドにはんだボールが堆積されます。 次に、ウェハをダイシングし、それらのダイを裏返して、はんだボールが基板パッドと揃うように位置決めします。 次に、通常は熱風を使用してはんだボールを溶解/リフローし、通常は毛細管現象を使用して、取り付けられたダイに電気絶縁性接着剤をアンダーフィルします。 [1]

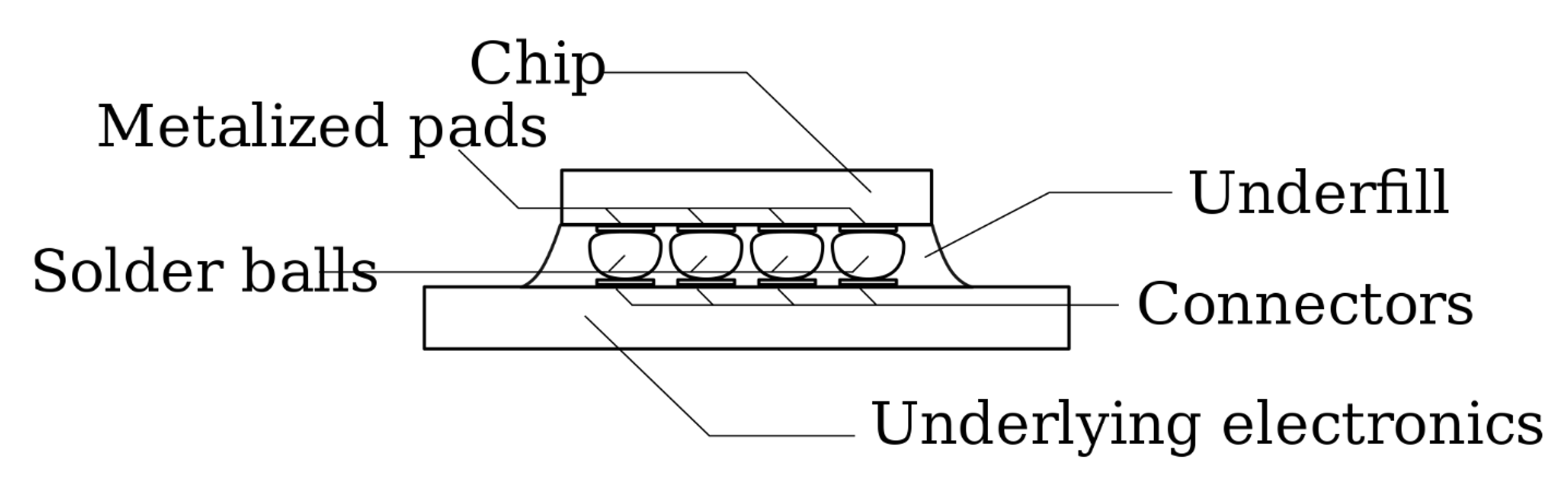

図 3: フリップチップの製造プロセス。 出典: ウィキペディア

銅ピラーまたはマイクロバンプに移行するには、これらの構造を作成するためのリソグラフィーが必要です。

「銅ピラーは通常、130μmピッチ以下で使用されます。これは、銅ピラーは、円形のはんだバンプではなく、ほとんどの場合、その上にはんだが付いたCuポストであるためです」と、同社のウェーハレベルパッケージング担当シニアバイスプレジデントのダグ・スコット氏は述べています。 Amkorテクノロジー。 「これにより、アセンブリのリフロー中にはんだが互いに接続するリスクを負うことなく、銅ピラーバンプを互いに近づけて配置することができます。一般的には、~40 μm Cu + ~25 μmです。」

テーマにもバリエーションがあります。 「マイクロバンプという用語は、シリコンとシリコン間の相互接続で使用される一般的な用語ですが、CTE (熱膨張係数) が一般に同じであるため、若干異なります」とエンジニアリング/技術マーケティング担当シニア ディレクターのマーク ガーバー氏は述べています。で ASEグループ。 「銅ピラーに使用される一般的な設計ルールの一部は同じですが、平らな表面トポグラフィーと低応力接合により、使用されるアンダーフィルの柔軟性が可能になります。 これにより、個々のバンプのピッチも変化する可能性があります。 現在では、使用されるウェーハレベルまたはファブレベルの配線について前述した配線の考慮事項により、35μm のバンプフルアレイピッチが可能です。」

ヘテロジニアス統合ロードマップ [2] では、ワイヤボンドからシリコン貫通ビアに至るまでのダイと基板の相互接続を含む、パッケージングのあらゆる側面について説明しています。 フリップチップ パッケージの場合、ダイと基板の相互接続、基板の再配線領域、および基板と基板の相互接続はすべて、製造限界に影響を及ぼします。

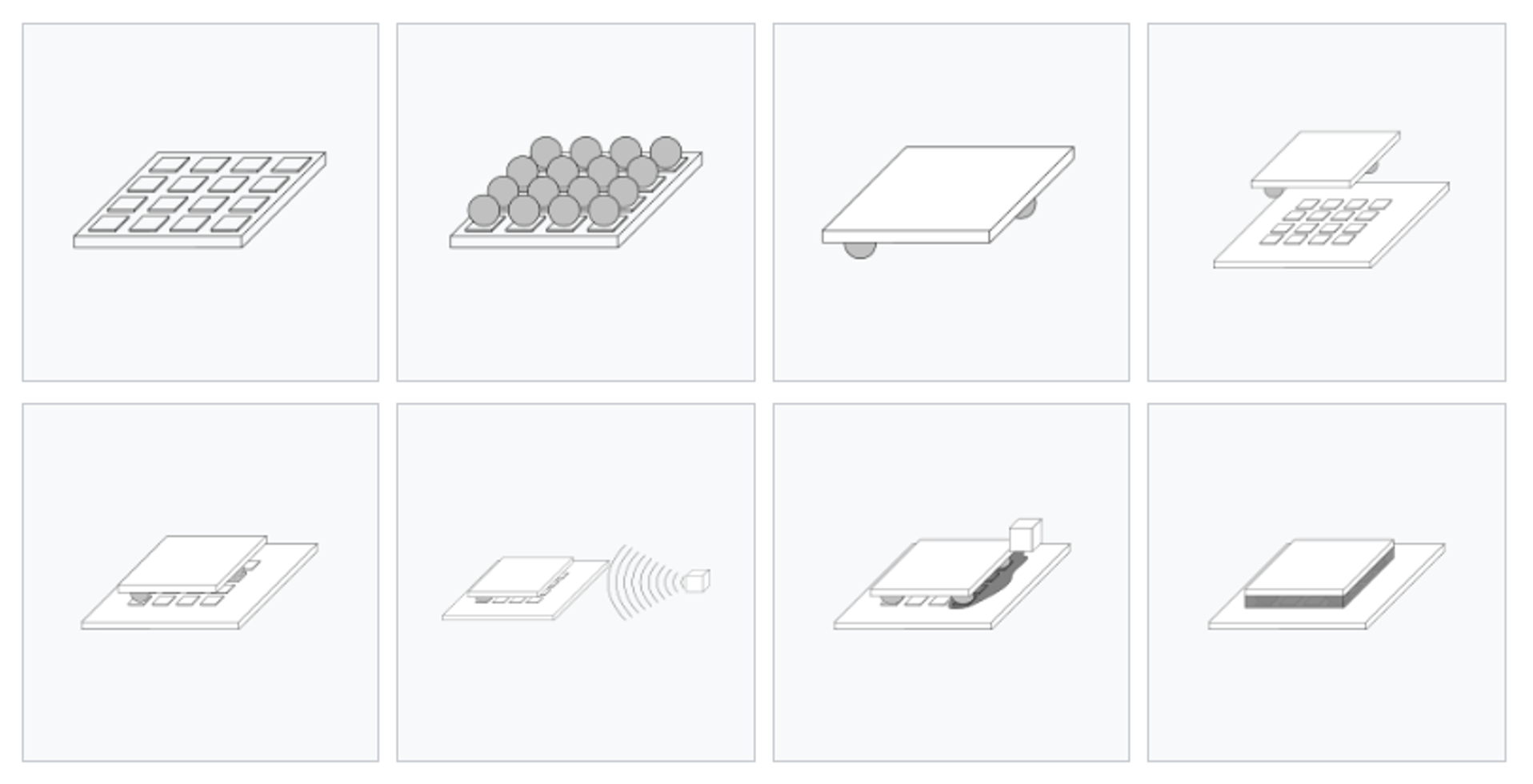

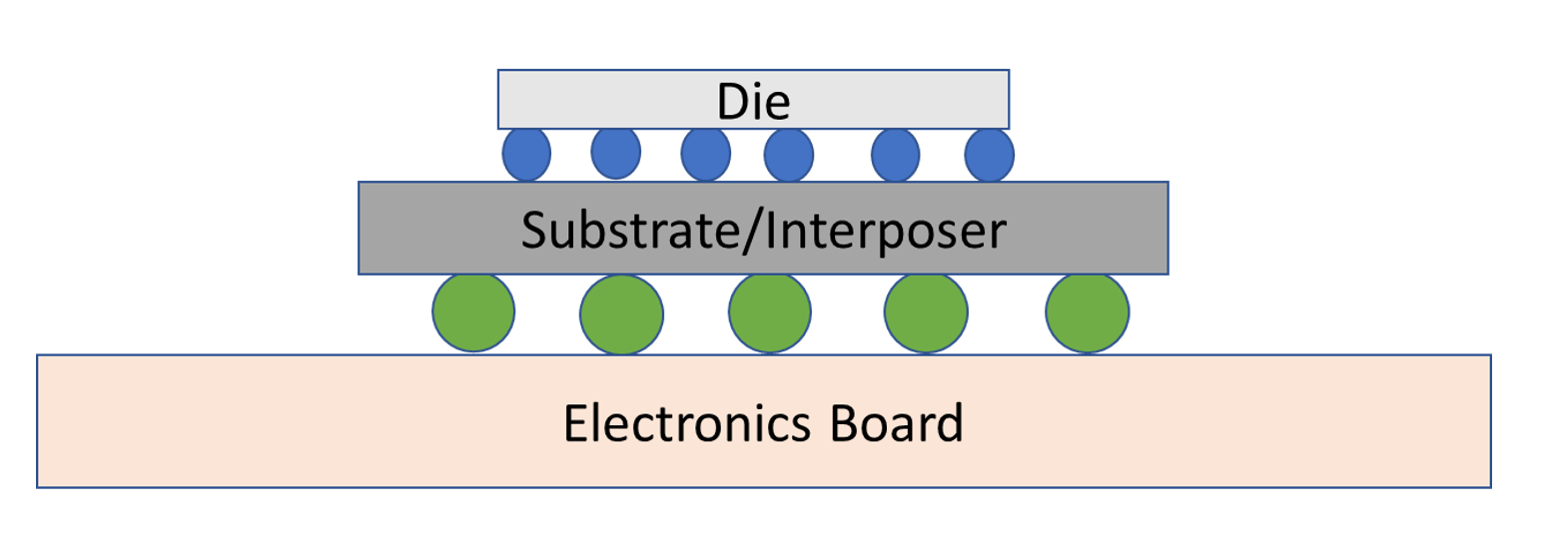

図4:フリップチップ実装の概念図。 出典: A. Meixner/半導体工学

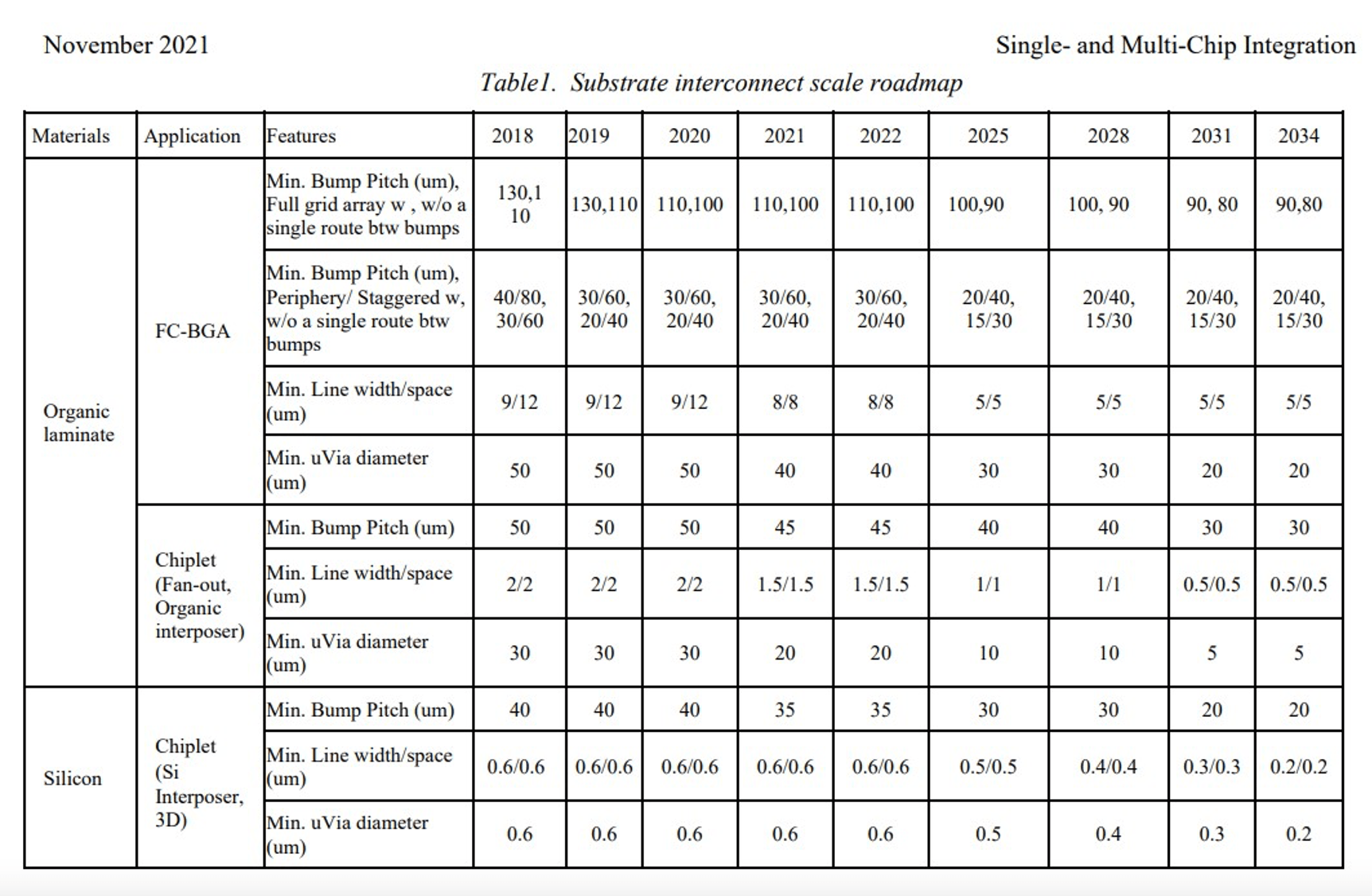

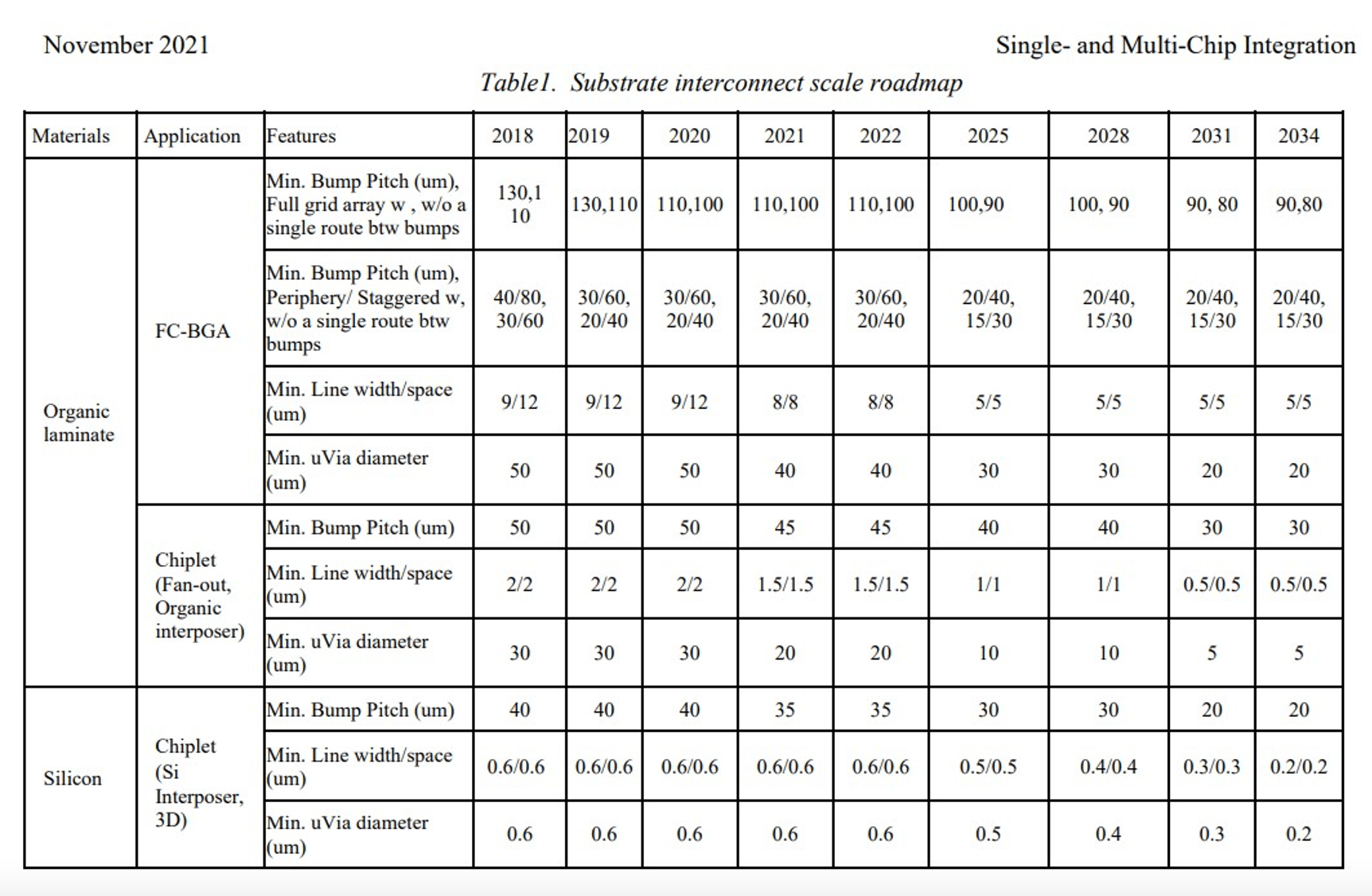

異機種間統合ロードマップ [8] の第 3 章には、現在および将来予測されるパッケージング技術のピッチの状況が文書化されています。 各フリップチップ相互接続テクノロジの最小ピッチは、サブセクション 1 (8.7 ページ) の表 41 に記載されています。

![異機種間統合ロードマップ [8] の第 3 章には、現在および将来予測されるパッケージング技術のピッチの状況が文書化されています。 各フリップチップ相互接続テクノロジの最小ピッチは、サブセクション 1 (8.7 ページ) の表 41 に記載されています。](https://platoaistream.com/wp-content/uploads/2023/05/challenges-grow-for-creating-smaller-bumps-for-flip-chips-7.png)

![異機種間統合ロードマップ [8] の第 3 章には、現在および将来予測されるパッケージング技術のピッチの状況が文書化されています。 各フリップチップ相互接続テクノロジの最小ピッチは、サブセクション 1 (8.7 ページ) の表 41 に記載されています。](https://platoaistream.com/wp-content/uploads/2023/05/challenges-grow-for-creating-smaller-bumps-for-flip-chips-8.png)

基板相互接続 (パッケージを基板に接続する部分) の対応表は、サブセクション 8.8 (43 ページ) にあります。

相互接続テクノロジーが変化するたびに、新しいプロセスとその限界が生じ、それがイノベーション、歩留まり管理、欠陥検査を推進します。

テクノロジーの限界を打ち破る

バンピング技術は、ピッチ、サイズ、高さ、電気的および機械的特性によって測定されます。 熱に関する考慮事項は、材料の CTE の不一致によって異なります。 反りは、より大きなダイおよびウェーハにとって懸念事項であり、ダイ取り付け前のウェーハのバックグラインドによって悪化します。

「相互接続の種類ごとにピッチ制限を引き起こす要因が多数あります」と ASE のガーバー氏は述べています。 「従来のはんだバンプ フリップ チップ相互接続から始まり、ピッチ機能は、アンダーフィルの崩壊高さ、トレース配線のキャプチャ パッド ピッチ、バンプ間ショート リスクのキャプチャ パッド ピッチ、およびその他のいくつかのピッチ関連の感度によって決まります。 プリマウントされたバンプの高さには定義された高さがありますが、IBM が C4 用語「制御されたコラプス チップ接続」を定義したように、はんだバンプの直径とキャプチャ パッドのサイズによって、相互接続の「コラプスまたは最終的な高さ」が決まります。 これは、ピッチに関連するはんだバンプを使用する場合の主なピッチ制限要因です。」

バンプの高さは設計によって決まりますが、加工の選択によっても決まります。

「標準的なメッキはんだバンプと銅ピラーバンプの場合、組み立て前のバンプの高さは一般に約 70µm ~ 75µm ですが、バンプ間のアンダーフィルの流れのための X、Y、Z スペースを確保するために、組み立て後のバンプの高さは約 50µm になります。 マイクロバンプはバンプ高さがはるかに低く、めっきするはんだの量がはるかに少なくなります。 具体的には、ピッチや端部のニーズに応じて、Cu やはんだの高さを低くして、マイクロバンプの高さを 10µm 未満にすることもできます」と Amkor の Scott 氏は述べています。 「標準的なメッキはんだバンプは、通常、130μm ~ 250μm の範囲のピッチで使用されます。 130µm 未満では、組み立て前のバンプ高さ 70µm から始めると、バンプ間に十分な xy スペースがありません。」

銅ピラーの作成には、はんだバンプよりも多くの処理ステップが必要です。

「ダイツーダイの世界に移行したとき、テクノロジーは異なっていました。なぜなら、現在はウェーハを扱っており、プラネライトはダイ対基板に比べて非常に優れているからです。 まず銅ピラーを作成します。はんだまたは銅ピラーを取り付ける最初のウェーハ上に、まずアンダー バンプ メタル (UBM) が存在します。 シリコンの中に入る開口部を覆う小さなキャップです。 それから銅のコアを作り、その上にブリキのキャップをかぶせます。 それで、受け取り側のウェーハは、そこにUBMパッドがあるように見えますが、通常はニッケルゴールドタイプのメッキが施されているため、美しくきれいです」とプロメックスインダストリーズのシェーファー氏は説明しました。 したがって、ラミネート基板のようなわずかな凹みではなく、わずかな突き出しが生じます。 「パッドにはんだ付け」をせずに、実際に濡れたままはんだ付けできることがわかりました。 そのように設計され、構築されています。 穴の中に落ちようとするのではなく、小さなドームなので、ほとんどはんだやパッドのように機能します。」

Cu ピラーの形成に必要なフォトリソグラフィーのステップには、基板の設計ルールと同様に制限があります。

「銅ポストと先端のはんだキャップで構成される銅ピラーの場合、銅ポストの高さは 110 つまたは複数のフォトレジスト層の厚さの制限に合わせて定義でき、ピッチを小さくするとアスペクト比が低くなります。ポストの高さからピッチまでが、フォトレジスト材料とイメージングツールの機能とともに制限になります」とガーバー氏は述べています。 「銅ピラー相互接続の二次的な制限は、使用される基板設計ルールです。 ピッチが 2um を超えるファイン ピッチの場合、BOT (ボンド オン トレース) または ET – 埋め込みトレースという XNUMX つの主要な方法が使用されます。この方法では、従来のキャプチャ パッドの代わりに銅ピラーのはんだキャップがトレースの上に配置されます。 銅ピラーのサイズと形状は、上記の制限を含め、ピッチを縮小し続けるための機能とロードマップに制限を与える可能性があります。 これらの制限の多くは、基板側のピラー間にトレースを配線する機能に起因します。 ウエハーレベルのRDLなどの新しいテクノロジーが利用可能になるにつれ、相互接続のロードマップはさらに前進することになるでしょうが、アンダーフィルなどの製造プロセスの高さ/アスペクト比には依然として制限があります。」

アンダーフィルプロセスには課題が伴うことに同意する人もいます。 「ピッチが細かくなると、バンプは短くなります。 その下に入れるアンダーフィルを見つけるのが難しくなってきています。 アンダーフィルは歴史的に 5 ミルのギャップ以下に収まるように設計されてきましたが、現在では 3 ミル、つまり 75 ミクロンまで下がっています」とシェーファー氏は述べています。 「現在、60 ミクロンと 25 ミクロンのギャップが見られ始めています。 きっと人々は新しいアンダーフィルの開発に取り組んでいると思います。 しかし、取り組むべきことはたくさんあります。 まず、粒子が細かくなるとスラッジのようになり、流れにくくなります。 これは取り除く必要がある障害です。」

収量の管理

バンピング技術が小型化するにつれて、銅ピラーを作成するためのリソグラフィーなどの追加の処理ステップにより、歩留まり検出器の新たな機会が開かれます。 ボンディングプロセスを成功させるには、微粒子、表面汚染物質、およびはんだバンプのボイド化が歩留まりにとって問題となります。 これらには、プロセス管理、計測、検査が必要です。

当然、汚染の管理も必要となります。 「Tier 1 OSATは工場の汚染源のレベルを下げるために投資しており、それによって不良品の割合を減らしています」とAmkorのScott氏は述べた。 「ピッチは欠陥の原因にはなりません。 ピッチに関係なく、同様のレベルの欠陥が存在します。」

しかし、ピッチには独自の課題もいくつか追加されています。 「ピッチが小さくなり、バンプサイズが小さくなるため、パーティクル汚染の管理が非常に重要になります。 ピッチが 30µm 以下に縮小され、表面間の接触が重要となるハイブリッド ボンディングなどの他のタイプの相互接続では、ウェハベースのクリーン ルーム環境が歩留まりにとって重要です」と ASE のガーバー氏は述べています。

アンダーフィルプロセスの準備も過小評価すべきではありません。

「一般的にラミネートでは、フリップチップを行った後にアンダーフィルを行うことになります」とプロメックスのシェーファー氏は語った。 「どこに配置するか、どのようにリフローするかを決定します。 ダイと基板の間のギャップの下にあるフラックス材料を取り除くために洗浄します。 次に、流れるエポキシでアンダーフィルを行います。 濡れて隙間やそのような性質のものを残さないように設計されています。 しかし、より細かいピッチに到達するにつれて課題が生じます。 バンプは少し短くなり、短くなるとチップと基板の間のギャップが小さくなるため、洗浄が難しくなります。 XNUMX 枚のスライドガラスを貼り合わせて、その間の汚れを取り除こうとすることを想像してください。」

計測と検査のニーズ

プロセス制御と歩留まりを管理するには、計測ツールと検査ツールが重要な役割を果たします。 「セットアップ時や規定の生産間隔で使用される工程内断面分析に加え、相互接続の完全性に関するガイダンスを提供するのに役立つツールが市場で入手可能です」と ASE のガーバー氏は述べています。

バンピングプロセスとボンディングプロセスにはそれぞれ、監視する必要がある特定の特性があります。 バンプの場合、計測では直径、高さ、および共平面性に焦点を当てます。 ピッチが小さくなると、バンプの直径と高さの制御をより厳密に制御する必要があります。 同様に、バンプの高さが縮小すると、共平面性のウィンドウが小さくなります。 通常、10% の変動は許容されます。 たとえば、バンプ高さが 30µm の場合、許容変動は ±3µm になります。 これを超えると、接合が失敗したり不十分になったりする原因になります。

「ボンディングは通常、マスリフローオーブンを使用して行われます」と、Amkor の先進パッケージおよびテクノロジー統合担当バイスプレジデントのマイク ケリー氏は述べています。 「リフロープロセスの初期特性評価は、リフロー中の反りを定量化するためのシャドーモアレと、フリップチップ部品自体の一貫した温度制御を保証するためのオーブンの温度マッピングを使用して確立されます。 セットアップ中に、ダイを機械的に持ち上げて検査し、はんだの濡れが良好であることを確認します。 また、フラックスは通常、「ディップフラックス」を使用して塗布されます。この場合、ダイバンプは、薄く厳密に制御されたフラックスリザーバに「浸漬」されます。 これらの品目の目視検査はサンプリングベースで行われます。」

目視検査の自動化が進むと、画像を見て判断するというオペレーターへの依存が減ります。 バンプ接続の指数関数的な増加が XNUMX つの要因です。 接着プロセスを変更すると、別のものが提供されます。 自己整合はんだリフロープロセスは成熟した技術です。 高度なパッケージングで一般的に使用される熱圧着には、電気試験に合格する信頼性のメカニズムがあります。 そのため、接合後のバンプを観察するために X 線検査および計測ツールの使用が促進されます。

「複雑さの低い包装の場合、施設はオペレーターと手作業による検査を省くことができます。 バンプが 100 個ある部品の場合、この方法は実行可能です。 1,000回の衝突では、間違いなく負担がかかります。 部品に 10,000 個のバンプがあると、チャンスはありません。 私たちはこの点を超えて、次の方法に進む必要があります」とアプリケーションおよび製品管理ディレクターのフランク・チェン氏は述べています。 ブルカー。 「品質と複雑さは密接に関係しています。より複雑なものを作ろうとすると、歩留まりが影響を受け、新しいツールが必要になるからです。 また、ツーリングとはプロセス ツールと計測ツールの両方を意味するため、両方を並行して進める必要があります。 私たち自身の研究によると、その 1,000 回の段差に到達したら、その時点で『自分の手先技術が不十分で、何か新しいものが必要だ』と考え始める必要があることが分かりました。」

パッケージ製造をサポートするために、さまざまな検査および計測ツールが利用可能です。

「プロセス制御を達成するために使用できる、または使用すべき方法がいくつかあります。 まず、従来の 2D 検査 (AOI) により、プロセス フロー (IQC、OQA、写真、洗浄、めっきなど) ごとに 100% の表面欠陥検査を行います。次に、2D 計測 (AOI) を使用して、バンプ サイズと直径のサイジングを制御できます。コントロール。 さらに、3D 計測 (AOI) は、サンプリング バンプ高さ/共平面性計測情報の取得に使用できます (これは通常、レーザー三角測量ベースの技術で行われます)」と、同社の製品マーケティング マネージャー、Nathan Peng 氏は述べています。 イノベーションへ。 「さらに、3D 計測では、通常白色光干渉計技術で収集される個々のバンプ高さ特性をターゲットにすることができます。 また、バンプとパッドの接続で障害を引き起こす可能性があるバンプ上部の有機残留物の検出を可能にする方法もあります。」

まとめ

より多くの相互接続数を必要とする製品が、相互接続ロードマップを推進し続けています。 各フリップチップ技術には、材料特性、アンダーフィル技術の課題となるサイズの縮小、相互接続構造を作成するためのリソグラフィーの使用の増加など、製造上の限界があります。 接合プロセスを変更すると、歩留まりと品質の目標を達成するために計測と検査のステップが増加します。

参考文献

- https://en.wikipedia.org/wiki/Flip_chip

- https://eps.ieee.org/technology/heterogeneous-integration-roadmap/2021-edition.html

- HIR 第 8 章 シングルチップとマルチチップの統合、 https://eps.ieee.org/images/files/HIR_2021/ch08_smcfinal.pdf

関連ストーリー:

バンプの同一平面性と不一致が歩留まりと信頼性の問題を引き起こす

チップとパッケージのサイズが縮小するにつれて、高度なパッケージングの課題は増大します。 さまざまな機器やテクノロジーが注目を集めています。

潜在的な欠陥によってバンプの信頼性が脅かされる

自動化されたソリューションは開発中ですが、開発には時間がかかります。

電力供給、材料、相互接続における大きな変化

製造とパッケージングは今後数十年間でどのように変化するか。

- SEO を活用したコンテンツと PR 配信。 今日増幅されます。

- プラトアイストリーム。 Web3 データ インテリジェンス。 知識増幅。 こちらからアクセスしてください。

- 未来を鋳造する w エイドリエン・アシュリー。 こちらからアクセスしてください。

- PREIPO® を使用して PRE-IPO 企業の株式を売買します。 こちらからアクセスしてください。

- 情報源: https://semiengineering.com/challenges-grow-for-creating-smaller-bumps-for-flip-chips/

- :持っている

- :は

- :not

- :どこ

- $UP

- 000

- 1

- 10

- 100

- 250

- 2D

- 3d

- 40

- 7

- 8

- a

- 能力

- できる

- 上記の.

- 達成する

- 買収

- Action

- 使徒行伝

- 実際に

- 添加

- NEW

- 追加

- 進める

- 高度な

- 後

- 先んじて

- 空気

- 整列する

- すべて

- 許す

- ことができます

- 沿って

- また

- an

- 分析

- &

- 別の

- どれか

- 適用された

- です

- AREA

- エリア

- 周りに

- AS

- 側面

- 側面

- アセンブリ

- At

- アタッチ

- オートメーション

- 利用できます

- 離れて

- バック

- 玉

- 基本

- 基礎

- BE

- なぜなら

- になる

- き

- さ

- 以下

- の間に

- 越えて

- ビッグ

- ボード

- 債券

- ロボット

- 両言語で

- ビルド

- 内蔵

- 焙煎が極度に未発達や過発達のコーヒーにて、クロロゲン酸の味わいへの影響は強くなり、金属を思わせる味わいと乾いたマウスフィールを感じさせます。

- by

- 来ました

- 缶

- キャップ

- 機能

- キャプチャー

- 原因となる

- 挑戦する

- 挑戦した

- 課題

- チャンス

- 変化する

- 変更

- 章

- 特性

- チェン

- チップ

- チップ

- 選択

- 選択肢

- クローザー

- 崩壊

- 崩壊

- 来ます

- 来ます

- コマンドと

- 一般に

- 比べ

- 複雑な

- 複雑さ

- コンポーネント

- コンピューティング

- 概念の

- 懸念

- お問合せ

- 接続する

- 接続

- Connections

- コネクト

- 検討事項

- 整合性のある

- 接触

- 汚染物質

- 続ける

- 連続

- 貢献する

- コントロール

- 制御

- 制御

- controls

- 銅

- 基本

- 対応する

- 可能性

- カップル

- 作ります

- 作成した

- 作成

- 重大な

- 電流プローブ

- 現在

- データ

- 取引

- 数十年

- 決定

- 定義済みの

- 絶対に

- 配達

- 需要

- 密度

- によっては

- 寄託

- 設計

- 設計

- 検出

- 決定する

- 決定

- 開発する

- 発展した

- Devices

- 死

- 異なります

- 難しい

- 取締役

- 土

- do

- ドキュメント

- ありません

- 行われ

- ダウン

- ドライブ

- ドライバー

- ドライバー

- 原因

- 間に

- e

- E&T

- 各

- どちら

- 埋め込まれた

- enable

- 可能

- end

- エンジニア

- エンジニアリング

- 十分な

- 確保

- 環境

- 装置

- 設立

- 等

- エーテル(ETH)

- 進化

- 例

- 存在する

- 拡大

- 期待する

- 高価な

- 説明

- 指数関数

- 施設

- 要因

- 工場

- 不良解析

- イチジク

- ファイナル

- もう完成させ、ワークスペースに掲示しましたか?

- 終わり

- 名

- フラットな

- 柔軟性

- フリップ

- フロー

- 流れ

- FLUX

- 焦点を当てて

- 収量のために

- 形成

- 発見

- から

- さらに

- さらに

- 利得

- ギャップ

- ギャップ

- 一般に

- 取得する

- 受け

- ガラス

- Go

- ゴエス

- 行く

- ゴールド

- 良い

- 研削

- 成長する

- ガイダンス

- ハンドル

- ハード

- 持ってる

- 持って

- 高さ

- ハイツ

- 助けます

- ハイ

- ハイパフォーマンス

- より高い

- 歴史的に

- ホール

- HOT

- 認定条件

- How To

- HTML

- HTTPS

- ハイブリッド

- i

- IBM

- IEEE

- 画像

- 絵

- イメージング

- 影響を受けた

- 重要

- in

- 含めて

- 増える

- 増加した

- の増加

- ますます

- 個人

- 情報

- 初期

- 革新的手法

- を取得する必要がある者

- 統合

- 整合性

- 相互接続

- に

- 投資する

- 巻き込む

- IT

- リーディングシート

- ITS

- 自体

- 風景

- より大きい

- レーザー

- 層

- つながる

- コメントを残す

- less

- レベル

- レベル

- 光

- ような

- LIMIT

- 制限

- 制限

- 制限

- 少し

- 長い

- 見て

- のように見える

- たくさん

- ロー

- メイン

- make

- 作る

- 管理

- マネージャー

- 管理する

- マニュアル

- 手動で

- 製造業

- 多くの

- マッピング

- マーク

- 市場

- マーケティング

- 材料

- 材料

- 成熟した

- 最大幅

- 手段

- 機械的な

- メカニズム

- 大会

- ご相談

- メモリ

- 言及した

- 金属

- 方法

- メソッド

- 計量

- ミクロン

- マイク

- 最小

- モバイル

- 監視対象

- 他には?

- 主に

- 移動

- ずっと

- マルチ

- 自然

- 必要

- 必要とされる

- ニーズ

- 新作

- 新技術

- 次の

- nice

- ニッケル

- いいえ

- 注意

- 今

- 数

- 目的

- of

- on

- かつて

- ONE

- 開いた

- 開設

- オペレータ

- 演算子

- 機会

- 反対した

- or

- オーガニック

- 元々

- その他

- 私たちの

- でる

- が

- 自分の

- パッケージ

- パッケージ

- 包装

- パッド

- ページ

- 並列シミュレーションの設定

- 部

- 粒子

- パス

- のワークプ

- 柱

- ピッチ

- ピッチ

- 場所

- プラトン

- プラトンデータインテリジェンス

- プラトデータ

- プレイ

- ポイント

- 貧しいです

- 人気

- 人気のある選択肢

- 配置された

- 可能

- ポスト

- 電力

- 社長

- 主要な

- 事前の

- プロセス

- ラボレーション

- 処理

- プロダクト

- 製品管理

- 生産

- 製品

- 投影

- プロパティ

- 提供します

- プッシュ

- 置きます

- 品質

- 測距

- 比

- 到達

- 本当に

- 受け入れ

- 減らします

- 電話代などの費用を削減

- 軽減

- 関係なく

- 関連する

- 信頼性

- 依存

- 削除済み

- 必要とする

- の提出が必要です

- 必要

- 結果

- リスク

- ロードマップ

- ロードマップ

- 職種

- ルーム

- ルート

- ルーティング

- ルール

- 前記

- 同じ

- 二次

- 見ること

- 見て

- 半導体

- シニア

- いくつかの

- 形状

- シフト

- ショート

- すべき

- 側

- シグナル

- シリコン

- 同様の

- 同様に

- から

- サイズ

- サイズ

- スライド

- わずかに異なる

- より小さい

- So

- ソリューション

- 一部

- 何か

- すぐに

- ソース

- ソース

- スペース

- 特定の

- 特に

- 標準

- start

- 起動

- ステップ

- 粘着

- まだ

- ストーリー

- ストレス

- 研究

- 成功した

- そのような

- サポート

- 表面

- SVG

- テーブル

- 取る

- ターゲット

- テクノロジー

- テクノロジー

- 期間

- テスト

- より

- それ

- 風景

- アプリ環境に合わせて

- それら

- テーマ

- その後

- そこ。

- したがって、

- サーマル

- ボーマン

- 彼ら

- 物事

- 考え

- この

- それらの

- しかし?

- しっかり

- 時間

- 先端

- 〜へ

- 今日

- 一緒に

- ツール

- 豊富なツール群

- top

- トレース

- 牽引力

- 伝統的な

- 試します

- 順番

- 2

- type

- 一般的に

- 下

- に

- つかいます

- 中古

- 通常

- 活用する

- 多様

- 非常に

- 副会長

- 詳しく見る

- 排尿

- ました

- we

- WELL

- いつ

- which

- 白

- 全体

- 広範囲

- Wikipedia

- 意志

- 無し

- 仕事

- ワーキング

- 作品

- 世界

- X

- X線

- 産出

- 収量

- 貴社

- あなたの

- ゼファーネット