SoC テストの課題は、チップに統合された機能ブロックの複雑さと多様性によって生じます。 SoC が複雑になるにつれて、テストのためにチップ内のすべての機能ブロックにアクセスすることがますます困難になります。また、SoC には数十億個のトランジスタが搭載されているため、チップのテストに非常に時間がかかります。テスト時間はテスト コストに直接影響するため、最終製品のコストを管理するにはテスト時間を最小限に抑えることが重要です。自動テスト パターン ジェネレーター (ATPG) は、設計内の障害を検出するためのテスト パターンを生成するため、SoC テストの重要な部分です。ただし、ATPG の自動化は、カバーする必要がある機能ブロックとテスト ポイントが多数あるため、特に複雑な SoC では困難な作業です。効率的かつ効果的な ATPG アルゴリズムを開発することは、SoC テストの重要な課題です。しかし、今日の ATPG ツールの多くは完全には自動化されていません。ツールを効果的に使用するには、ユーザーはツールが提供するすべてのコマンドとオプションを学習する必要があります。

ATPG プロセスに自動化をもたらし、それによってエンジニアリングの生産性を向上させるソリューションはありますか?このソリューションでテスト時間も大幅に節約できたらどうなるでしょうか? Siemens EDA の Tessent Streaming Scan Network (SSN) ソリューションは、これらの利点を提供することを約束します。これは、最近の User2User カンファレンスで、Siemens EDA の顧客の XNUMX つである Intel によって実証されました。 Intel の Toai Vo 氏は、Tessent SSN ソリューションを使用した最初の設計でのチームの経験に基づいて実証ポイントを提示しました。彼のチームには、ケビン・リー、ジョー・チョウ、チェンクオ(トム)ウーが含まれていました。

Tessent SSN ソリューション

標準的なスキャン テストのアプローチでは、テスト データが一度に 1 ビットずつ回路にロードされ、スキャン チェーンを介してシフトされて出力応答が観察されます。このプロセスはテスト パターンごとに繰り返されるため、時間がかかり、テスト時間が長くなる可能性があります。しかし、Tessent SSN ソリューションはテスト データをパケット化して、DFT 実装の労力を大幅に削減し、製造テスト時間を短縮します。コアレベルとチップレベルの DFT 要件を分離することで、各コアをそのコアに最適な圧縮構成で設計できます。このソリューションを使用すると、テストが必要な内部ノードが多数ある大規模で複雑なチップを効率的にテストできます。専用ネットワークを使用してテストデータをストリーミング方式で送信するため、データの並列処理が可能になり、テスト時間が短縮されます。

スケーラビリティ

ストリーミング スキャン ネットワークは、多数の機能ブロックを備えた SoC を処理できるスケーラブルなスキャン アーキテクチャをサポートしています。このツールは、テスト時間とスキャン データ量を最小限に抑えながら、任意の数のコアを同時にテストするスケーラブルなアプローチを提供します。 Tessent SSN テスト インフラストラクチャは、IEEE 1687/IJTAG 標準を中心に構築されており、より複雑な設計やテスト シナリオを処理するための優れた柔軟性と拡張性を提供します。

オートメーション

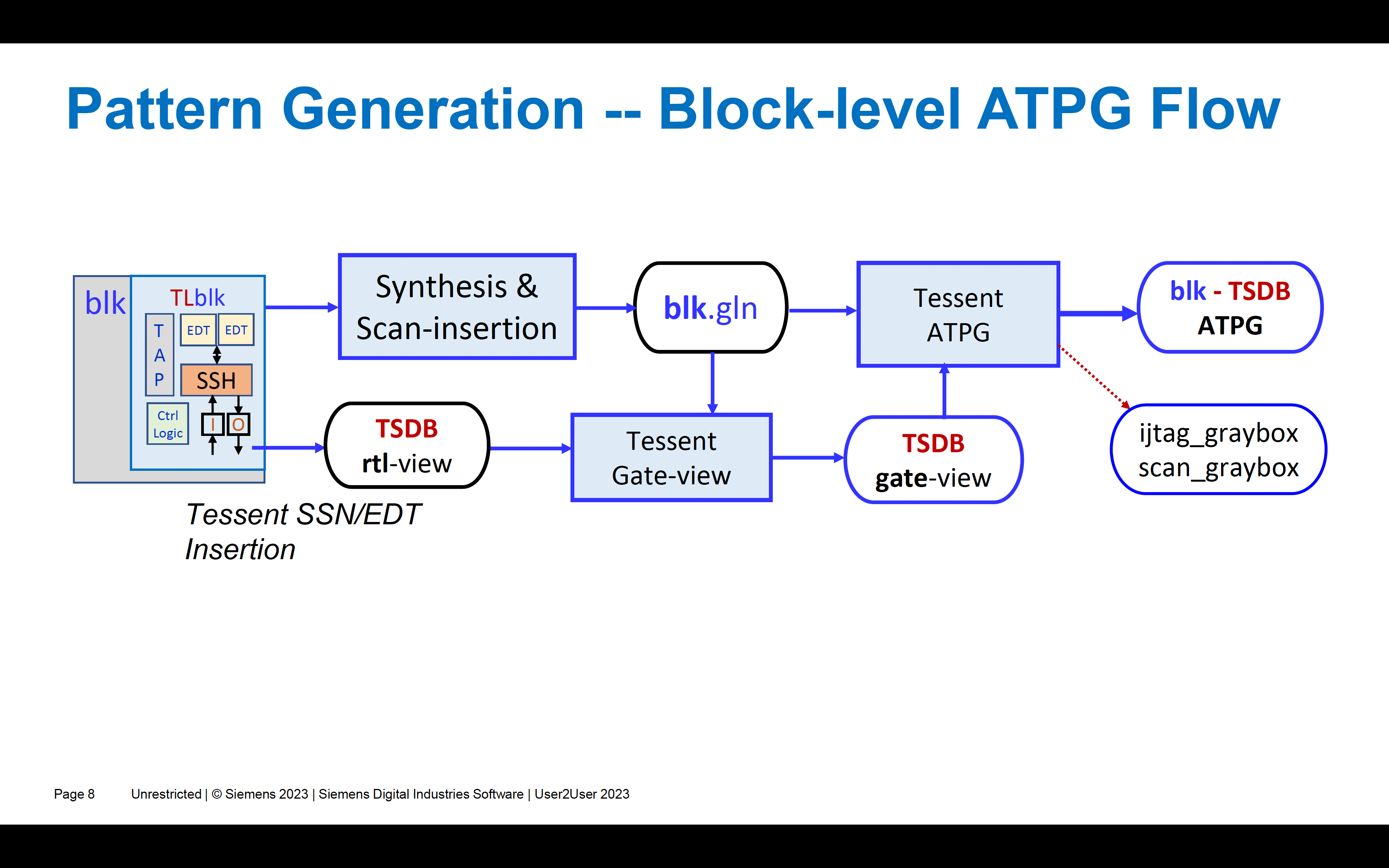

テスト インフラストラクチャの階層的なオブジェクト指向の性質は、自動化を容易にするのに役立ちます。 Tessent インフラストラクチャを使用すると、ユーザーはテスト ロジックをチップに簡単に挿入できます。このプロセスは RTL 設計から始まり、自動化を使用して SSN テスト ロジックが挿入されます。

テスト時間の節約

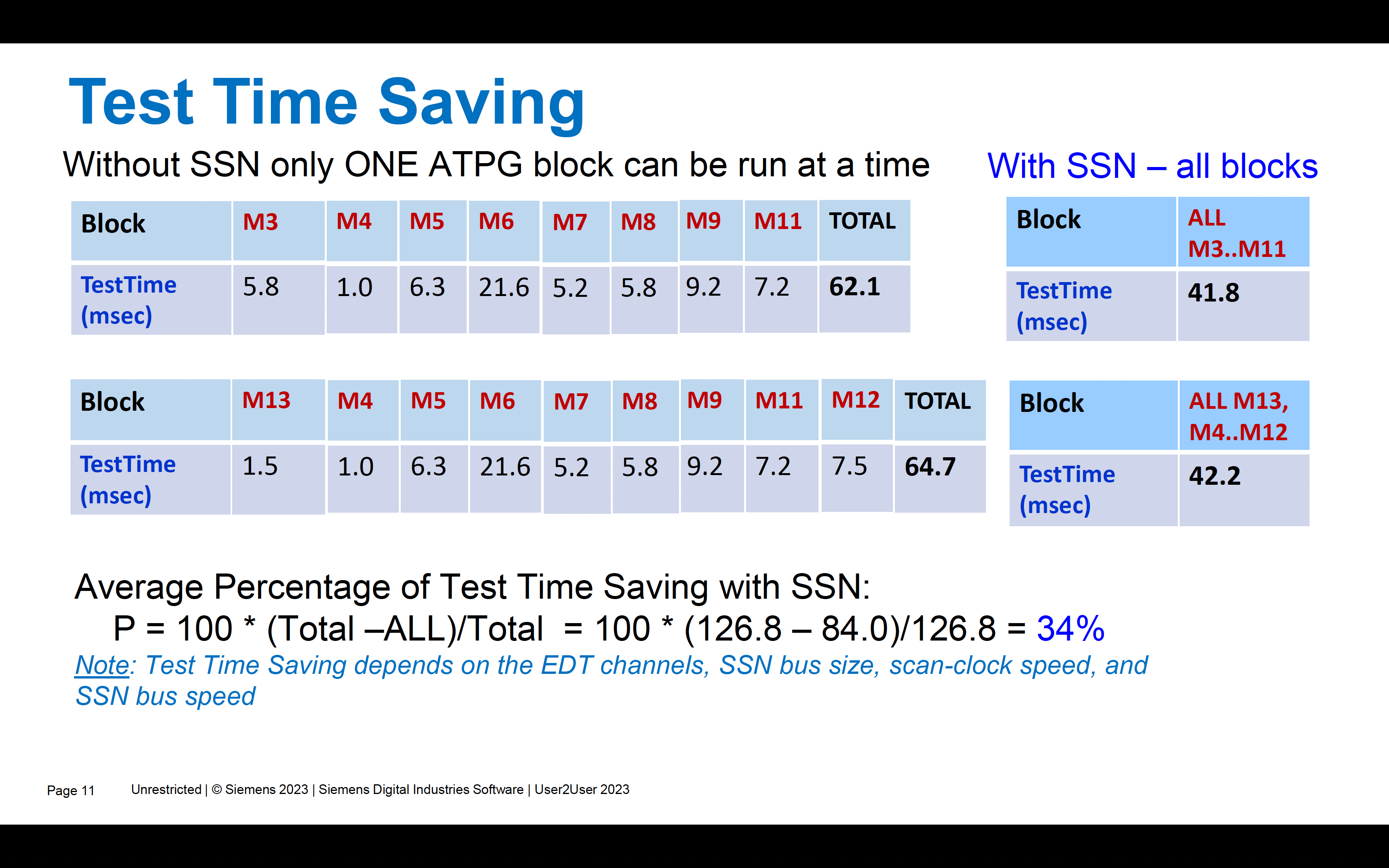

従来の ATPG アプローチを使用すると、通常は一度にブロックのみを実行できるため、合計テスト時間が長くなります。 Tessent SSN ATPG アプローチを使用すると、複数のブロックを並行して実行できるため、合計テスト時間が大幅に短縮されます。次の表は、Toai のチームが設計で達成したテスト時間の節約を示しています。

まとめ

Toai のチームは、従来の組み込み決定論的テスト (EDT) チャネル ベースの ATPG から SSN を使用したパケットベースの ATPG への移行が非常に簡単であることを発見しました。 Tessent SSN ソリューションは、エンジニアリングの労力とシリコンの立ち上げ時間を大幅に削減しました。また、従来のテスト ソリューションと比較して、テスト時間は大幅に短縮されました。 Toai Vo 氏の言葉を借りると、これはまさに革新的なテスト ソリューションであり、実際に機能します。

詳細については、 Tessent SSN 製品ページにアクセスしてください。

また読む:

高速 SerDes リンクでの DFE エラー伝播の影響を軽減する

この投稿を共有する:

- SEO を活用したコンテンツと PR 配信。 今日増幅されます。

- プラトアイストリーム。 Web3 データ インテリジェンス。 知識増幅。 こちらからアクセスしてください。

- 未来を鋳造する w エイドリエン・アシュリー。 こちらからアクセスしてください。

- PREIPO® を使用して PRE-IPO 企業の株式を売買します。 こちらからアクセスしてください。

- 情報源: https://semiwiki.com/eda/328395-tessent-ssn-enables-significant-test-time-savings-for-soc-atpg/

- :は

- :not

- :どこ

- $UP

- a

- 絶対に

- アクセス

- 達成

- アルゴリズム

- すべて

- また

- an

- および

- どれか

- アプローチ

- です

- 周りに

- AS

- At

- 自動化

- オートマチック

- オートメーション

- 自動車

- ベース

- BE

- になる

- になる

- 利点

- 億

- ビット

- ブロック

- ブロック

- 持って来る

- もたらす

- 内蔵

- 焙煎が極度に未発達や過発達のコーヒーにて、クロロゲン酸の味わいへの影響は強くなり、金属を思わせる味わいと乾いたマウスフィールを感じさせます。

- by

- 缶

- 携帯

- チェーン

- 挑戦する

- 課題

- 挑戦

- チャネル

- チップ

- チップ

- 比べ

- 複雑な

- 複雑さ

- 講演

- 基本

- 費用

- カバー

- 重大な

- 重大な

- Customers

- データ

- 専用の

- 配信する

- 配信する

- 提供します

- 設計

- 設計

- デザイン

- 細部

- 開発

- 難しい

- 直接に

- 多様性

- 劇的に

- 原因

- 間に

- 各

- 容易

- 簡単に

- 簡単に

- 効果的な

- 効果的に

- 効果

- 効率的な

- 効率良く

- 努力

- 埋め込まれた

- 可能

- 有効にする

- エンジニアリング

- 強化

- エラー

- 特に

- 体験

- 非常に

- 欠点

- 名

- 柔軟性

- フロー

- フォロー中

- 発見

- から

- 完全に

- 機能的な

- 生成

- 世代

- ジェネレータ

- 大きい

- 大いに

- ハンドル

- 持ってる

- ハイ

- 彼の

- しかしながら

- HTTPS

- IEEE

- if

- 影響

- 実装

- in

- 含まれました

- ますます

- インフラ関連事業

- 革新的な

- 統合された

- インテル

- 内部

- に

- IT

- 自体

- キー

- 大

- つながる

- LEARN

- レベル

- ロジック

- 長い

- 作成

- 管理する

- 方法

- 製造業

- 多くの

- 最大幅

- 移動します

- 最小化

- 他には?

- 最も

- の試合に

- 自然

- 必要

- ネットワーク

- ノード

- 通常は

- 数

- オブジェクト

- 観察する

- of

- 提供

- on

- ONE

- の

- 最適な

- オプション

- 注文

- 出力

- ページ

- 並列シミュレーションの設定

- 部

- パターン

- パターン

- プラトン

- プラトンデータインテリジェンス

- プラトデータ

- ポイント

- ポスト

- PLM platform.

- プロセス

- 処理

- プロダクト

- 生産性

- 約束

- 証明

- は、大阪で

- 読む

- 本当に

- 最近

- 減らします

- 電話代などの費用を削減

- 縮小

- 削減

- 繰り返される

- 要件

- 回答

- ルート

- ラン

- 貯蓄

- スケーラビリティ

- ド電源のデ

- スキャン

- シナリオ

- シフトした

- 作品

- ジーメンス

- 重要

- シリコン

- 溶液

- 一部

- 標準

- ストリーミング

- サポート

- テーブル

- 仕事

- チーム

- test

- テスト

- それ

- アプリ環境に合わせて

- それら

- そこ。

- それによって

- ボーマン

- この

- 介して

- 時間

- 時間がかかる

- <font style="vertical-align: inherit;">回数</font>

- 〜へ

- 今日

- ツール

- 豊富なツール群

- トータル

- 伝統的な

- 送信します

- 信頼

- つかいます

- 中古

- ユーザー

- users

- 非常に

- 、

- ボリューム

- ました

- この試験は

- which

- while

- 以内

- ウー

- 言葉

- 作品

- ゼファーネット