Banias Labs は、次世代通信のインフラストラクチャ ソリューションを開発する半導体企業です。同社のターゲット市場は、ハイパースケール データセンター、ネットワーキング、AI、光モジュール、および新たなハイ パフォーマンス コンピューティング設計用のイーサネット スイッチ SoC を含む、ハイ パフォーマンス コンピューティング インフラストラクチャ市場です。これらの SoC には、システム パフォーマンスを向上させ、市場投入までの時間を短縮するために、高速イーサネット設計と低遅延ソリューションが必要です。同社は、この市場の要件に対応するために、5nm プロセス技術で光 DSP SoC を開発しました。

![]()

光 DSP SoC は、高速光通信システムで使用するために設計された特殊なタイプのシステムオンチップ (SoC) です。 DSP に加えて、光 DSP SoC には通常、イーサネット PHY IP、PCIe IP、DDR メモリ コントローラーなどの高速インターフェイス IP ブロックが含まれています。これらのタイプの SoC は、リアルタイム信号処理のための低遅延での高速データ転送を可能にします。また、消費電力を最小限に抑えるように設計されているため、熱の問題を軽減しながら効率的な動作を必要とするアプリケーションに最適です。利点と同時に課題も伴います。光通信システムの特殊な要件により、光 DSP SoC の設計は通常の SoC の設計よりも困難になります。

実装の課題

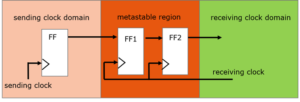

課題は、設計の複雑さ、厳しい電力と性能の要件、およびさまざまな業界標準を満たす必要性を中心に展開しています。 DSP プロセッサ、イーサネット PHY IP、その他のカスタム ブロックを含む複数の IP ブロックを統合するには、慎重な設計と検証が必要です。 PCIe や DDR などの高速インターフェイスが追加されると、設計はさらに複雑になります。システム内の高速インターフェイスと複数の IP ブロックは、信号の歪み、クロストーク、電磁干渉を引き起こす可能性があり、システムのパフォーマンスと信頼性に影響を与える可能性があります。システムがそのパフォーマンスと信頼性の要件を確実に満たせるように、信号と電力の整合性の分析と最適化を設計サイクルの早い段階で実行する必要があります。最後に、市場投入までの時間要件を満たすことは困難な場合があります。ハイパフォーマンス コンピューティング インフラストラクチャ市場は急速に進化しており、SoC 開発チームは競合他社に先んじるために設計を迅速に提供する必要があります。

シリコンのファーストパスを成功させる

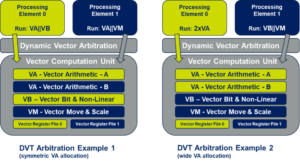

上記の課題を克服するには、包括的なアプローチが必要です。高性能、低遅延ソリューションの重要なコンポーネントの 10 つは、イーサネット PHY IP です。イーサネット PHY IP は、SoC とイーサネット ネットワーク間の物理層インターフェイスを担当します。 IP は、25G、40G、50G、100G、200G、400G、800G、802.3G などの高速イーサネット インターフェイスをサポートし、低遅延と低消費電力を実現する必要があります。さらに、IP は IEEE XNUMX や Ethernet Alliance などのさまざまな標準をサポートする必要があります。もう XNUMX つの重要なコンポーネントは EDA 設計スイートです。 EDA 設計スイートは、電力最適化、パフォーマンス分析、面積最適化、歩留まり分析など、SoC の設計と検証のための包括的なソリューションを提供する必要があります。 EDA 設計スイートには、人工知能 (AI) や機械学習 (ML) などの高度な機能が含まれており、生産性の向上と市場投入までの時間の短縮に優れています。

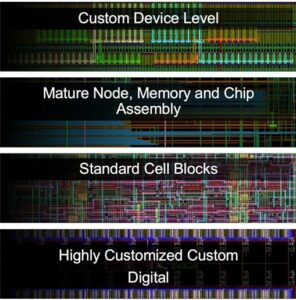

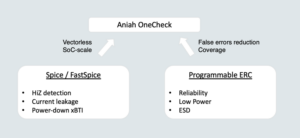

シノプシス、ファーストパスシリコンの成功を加速

シノプシスは、ハイパフォーマンス コンピューティング インフラストラクチャ市場向けの SoC 開発特有の課題に対処するソリューションを提供します。同社は、配線の実現可能性調査、パッケージング基板のガイドライン、信号と電力の完全性モデル、徹底したクロストーク解析を含む包括的な IP ソリューションを提供しています。これは、光 DSP SoC の開発時に直面する信号と電力の整合性の課題に対処するために不可欠です。シノプシスの 112G イーサネット PHY IP は、低遅延、柔軟な到達距離、5nm プロセス技術の成熟度を備えており、ハイパースケール データセンター、ネットワーキング、AI、光モジュール、イーサネット スイッチ SoC にとって理想的なソリューションとなります。さらに、シノプシスは、最適化された電力、パフォーマンス、面積、歩留まりで高品質の結果を提供する EDA デザイン スイートを提供します。シノプシスの AI 主導型 EDA デザイン スイートは、システム パフォーマンスを向上させ、市場投入までの時間を短縮するソリューションを提供し、ハイパフォーマンス コンピューティング インフラストラクチャ市場で成功するソリューションの重要なコンポーネントとなっています。

まとめ

シノプシスは、高度なイーサネット スイッチおよびネットワーキング SoC の開発を加速する、高性能、低遅延のソリューションを提供します。シノプシスの包括的な IP ソリューション、包括的な EDA デザイン スイート、および AI 強化 EDA スイートの詳細については、次のページを参照してください。

また読む:

マルチダイ システム: ここ数年のコンピューティングにおける最大の混乱

高速でアーキテクチャ主導の PPA 最適化により、独自の RISC-V プロセッサを開発する際のリスクを回避する

この投稿を共有する:

- SEO を活用したコンテンツと PR 配信。 今日増幅されます。

- Platoblockchain。 Web3メタバースインテリジェンス。 知識の増幅。 こちらからアクセスしてください。

- 未来を鋳造する w エイドリエン・アシュリー。 こちらからアクセスしてください。

- 情報源: https://semiwiki.com/ip/327703-synopsys-accelerates-first-pass-silicon-success-for-banias-labs-networking-soc/

- :持っている

- :は

- a

- 私たちについて

- 上記の.

- 加速する

- 加速する

- 添加

- NEW

- さらに

- 住所

- 高度な

- 利点

- 先んじて

- AI

- アライアンス

- また

- an

- 分析

- および

- 別の

- アプローチ

- です

- AREA

- 周りに

- 人工の

- 人工知能

- 人工知能(AI)

- AS

- At

- 帯域幅

- BE

- より良いです

- の間に

- 最大の

- ブロック

- ブースト

- 缶

- 注意深い

- センター

- 課題

- 挑戦

- 来ます

- コミュニケーション

- 通信部

- 会社

- コンペ

- 複雑さ

- コンポーネント

- コンポーネント

- 包括的な

- コンピューティング

- 消費

- 作ります

- 重大な

- カスタム

- サイクル

- データ

- データセンター

- 配信する

- 提供します

- 設計

- 設計

- 設計

- デザイン

- 発展した

- 開発

- 開発

- 開発

- 途絶

- 早い

- 効率的な

- 新興の

- enable

- 強化された

- 確保

- 本質的な

- 進化

- 直面して

- スピーディー

- 特徴

- 最後に

- 名

- フレキシブル

- フォロー中

- から

- さらに

- 成長

- ガイドライン

- ハイパフォーマンス

- 高品質

- HTML

- HTTPS

- 飢餓

- 理想

- IEEE

- 画像

- 影響

- 命令的

- 重要

- in

- 含ま

- 含めて

- 増加した

- 産業を変えます

- 業界標準

- インフラ関連事業

- 統合

- 整合性

- インテリジェンス

- インタフェース

- インターフェース

- IP

- 問題

- IT

- ITS

- ラボ

- レイテンシ

- 層

- LEARN

- 学習

- ロー

- 機械

- 機械学習

- make

- 作成

- 市場

- 満期

- 最大幅

- 大会

- ご相談

- メモリ

- 言及した

- ML

- モデル

- モジュール

- 他には?

- の試合に

- 必要

- ネットワーク

- ネットワーキング

- 次世代

- of

- オファー

- on

- ONE

- 操作

- 最適化

- 最適化

- その他

- 自分の

- 包装

- パス

- パフォーマンス

- 物理的な

- プラトン

- プラトンデータインテリジェンス

- プラトデータ

- ポスト

- 電力

- プロセス

- 処理

- プロセッサ

- 生産性

- 提供します

- は、大阪で

- すぐに

- 急速に

- リーチ

- 読む

- への

- 電話代などの費用を削減

- レギュラー

- 信頼性

- 必要とする

- 要件

- 必要

- 責任

- 結果

- リスク

- 半導体

- シグナル

- シリコン

- 溶液

- ソリューション

- 専門の

- 規格

- 滞在

- 勉強

- 成功

- 成功した

- そのような

- スイート

- サポート

- スイッチ

- システム

- ターゲット

- チーム

- テクノロジー

- より

- それ

- アプリ環境に合わせて

- それら

- サーマル

- ボーマン

- 彼ら

- この

- 〜へ

- あまりに

- 転送

- 一般的に

- ユニーク

- つかいます

- さまざまな

- 検証する

- 、

- 訪問

- which

- 産出

- あなたの

- ゼファーネット