1980 年代に同軸ケーブルを介した 10Mbps の共有 LAN が登場して以来、イーサネットは一貫した進歩を遂げ、現在では最大 1.6Tbps の速度をサポートできる可能性があります。この進歩により、イーサネットはライブ ストリーミング、無線アクセス ネットワーク、産業制御などの幅広いアプリケーションに対応できるようになり、信頼性の高いパケット転送とサービス品質の重要性が強調されています。現在のインターネット帯域幅は約 500 Tbps で上昇しており、バックエンドのデータセンター内トラフィック処理の改善に対する需要が高まっています。個々のサーバーはまだテラビット/秒レベルで動作していませんが、データセンター全体のトラフィックはこの規模に近づいており、IEEE 802.3dj グループが標準化の取り組みに着手するよう促され、拡大するデータ フローを管理するための堅牢なイーサネット コントローラーと SerDes が必要になっています。このような需要の高まりを背景に、プロセッサ間通信はすでにこの速度に達しています。

プロセッサ間通信は、遅延を最小限に抑えた 1.6T レートのニーズの先頭に立っています。個々のデバイスは固有の処理能力とチップ サイズによって制限されますが、チップを組み合わせることでこれらの能力を大幅に拡張できます。第 XNUMX 世代のアプリケーションの後には、データセンター内のスイッチ間接続が導入され、高性能プロセッサとメモリのプールが可能になり、クラウド コンピューティング内のスケーラビリティと効率が向上すると予想されています。

IEEE 802.3dj イニシアチブ: 1.6 Tbps の相互運用性を実現するイーサネット標準の進歩

進化する標準化の取り組みへの準拠は、シームレスなエコシステムの相互運用性にとって極めて重要です。 IEEE の 802.3dj グループは、物理層と 200G から 1.6 テラビット/秒までの速度の管理パラメータを含む次期イーサネット標準の策定を進めています。このグループの目標は 1.6 Tbps のイーサネット MAC データ レートで、MAC 層での最大ビット エラー レートが 10-13 以下になることを目指しています。さらに、16G および 8G SerDes を活用する、さまざまなチップ アプリケーションに適したオプションの 112 および 224 レーンのアタッチメント ユニット インターフェイス (AUI) が含まれます。物理的には、1.6Tbps 仕様では、8 ペアの銅線 Twinax ケーブルによる最大 8 メートルの伝送と、500 ペアのファイバーによる 2 メートルから 2026 km の距離の伝送が必要になります。この規格の完全な承認は 2024 年春までに予定されていますが、コア機能セットは XNUMX 年に完成すると予想されています。

1.6T イーサネット サブシステムにおける帯域幅のオーバーヘッドとエラー修正

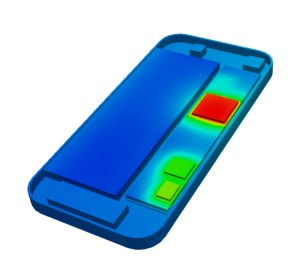

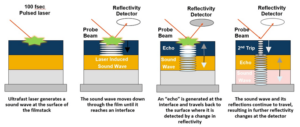

図 1: 1.6T イーサネット サブシステムのコンポーネントを示す図。

以前のイーサネットの反復では、PCS は信頼性の高いパケット検出のためのデータ エンコーディングに主に焦点を当てていました。しかし、1.6T イーサネット速度への増加に伴い、特に短いリンクでも信号劣化を防ぐために、前方誤り訂正 (FEC) の必要性が明らかになりました。この目的のために、1.6T イーサネットは引き続きリードソロモン FEC を利用します。このアプローチでは、514 シンボル ブロックにエンコードされた 10 個の 544 ビット シンボルで構成されるコードワードが構築され、6% の帯域幅オーバーヘッドが発生します。これらの FEC コードワードは、各物理リンク (8T イーサネットの場合は 1.6) がコードワード全体を伝送しないように、AUI 物理リンク全体に分散されます。この方法は、エラー バーストに対する追加の保護を提供するだけでなく、遠端のデコーダでの並列化も可能にし、それによって待ち時間を短縮します。

ギアボックスと SerDes を備えた物理メディア アタッチメント (PMA) は、イーサネット信号を送信チャネルにもたらします。 1.6T イーサネットの場合、これにはそれぞれ 8Gbps で動作する 212 チャネルが含まれ、6% の FEC オーバーヘッドが発生します。採用されている変調技術は 4 レベル パルス振幅変調 (PAM-4) で、送信シンボルごとに XNUMX つのデータ ビットをエンコードするため、従来のノンリターン ゼロ (NRZ) アプローチと併用すると、帯域幅が効果的に XNUMX 倍になります。送信メカニズムはデジタル - アナログ変換に依存していますが、受信側では DSP と組み合わせたアナログ - デジタル変換により正確な信号抽出が保証されます。

さらに、イーサネット PCS では、イーサネット リンク上のエンドツーエンドにまたがる「外部 FEC」が導入されることに注意することが重要です。より長い到達距離のチャネルを強化するために、個々の物理回線に対する追加のエラー訂正層がパイプラインにあり、おそらくハミング コード FEC が採用されています。この補正は、そのような補正が不可欠な光トランシーバ モジュールに主に応用されることが期待されています。

図 2: 拡張リーチに連結 FEC を使用する場合に追加される追加のオーバーヘッドを示す図。

図 2 に示すシステム例では、MAC と PCS は光モジュールとファイバーストレッチを介して接続されています。 PCS のビット エラー レートは 10-5 光モジュール リンクでのエラーに加えて、光リンク自体からのエラーも発生します。単一の RS-FEC をエンドツーエンドで使用するだけでは、10 を達成するには十分ではありません。-13 イーサネット標準のため、リンクの信頼性が低くなります。オプションとしては、ホップごとに個別の RS FEC を 212 重に実装することが考えられます。これにより、コストと遅延が大幅に増加します。より効果的なソリューションは、光リンク専用の連結ハミング コード FEC を統合し、光接続の典型的なランダム エラーに対応することです。この内部 FEC 層により、ライン レートが 226 Gbps から XNUMX Gbps にさらに拡張されるため、SerDes がこのライン レートをサポートできることが不可欠です。

1.6T イーサネット システムにおける遅延の課題

図 3: 1.6T イーサネット サブシステムのレイテンシ パス。

送信キュー、送信期間、媒体通過時間、いくつかの処理時間と受信時間など、さまざまなコンポーネントがイーサネット遅延に寄与します。これを視覚化するには、包括的な 3T イーサネット サブシステムを示す図 1.6 を考えてください。遅延は遠端アプリケーションの反応時間の影響を受ける可能性がありますが、この要因はイーサネットの外部にあるため、遅延分析では除外されることがよくあります。イーサネット インターフェイスでの遅延を最小限にするには、特定の状況を理解する必要があります。たとえば、スイッチ間のトランク接続では、低速のクライアント リンクに固有の遅延があるため、遅延は主な懸念事項ではない可能性があります。距離も影響します。長さが長くなると、待ち時間が長くなります。もちろん、これは他のシナリオでの遅延を無視すべきだという意味ではなく、遅延の削減は常に目標です。

伝送遅延は本質的にイーサネットの速度とフレーム サイズに関係しています。具体的には、1.6T イーサネット システムの場合、最小サイズのパケットの送信には 0.4ns が必要です。これは、基本的に、2.5 GHz クロックの 8 ティックあたり 48 つのイーサネット フレームに相当します。一方、標準の最大サイズのフレームの送信には 5ns かかり、ジャンボ フレームの場合は 4ns まで延長されます。選択したメディアによってさらに遅延が決まります。たとえば、光ファイバーでは通常、XNUMX メートルあたり XNUMXns の遅延が発生しますが、銅線ケーブルは XNUMX メートルあたり XNUMXns とわずかに高速です。

全体的な遅延のかなりの部分は、受信機コントローラーに根ざしています。 RS FEC デコーダは本質的に遅延を引き起こします。エラー訂正を開始するには、システムは 4 つのコードワードを受信する必要があります。これは、1.6Tbps で 12.8ns に相当します。エラー修正やバッファリングなどの後続のアクティビティにより、この遅延が増幅されます。 FEC コードワードの保存期間は一貫していますが、メッセージ受信時の遅延は特定の実装に依存します。それにもかかわらず、綿密なデジタル設計戦略を採用することでレイテンシを最適化することができます。

基本的に、FEC メカニズムと物理的な距離またはケーブルの長さに起因して、固有の避けられない遅延が存在します。これらの要素に加えて、設計の専門知識がイーサネット コントローラーの遅延を最小限に抑える上で極めて重要な役割を果たします。 MAC、PCS、および PHY を統合および最適化する完全なソリューションを活用することで、最も効率的で低遅延の実装への道が開かれます。

まとめ

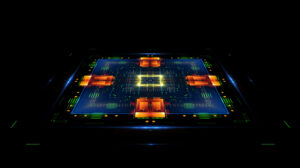

図 4: 224nm プロセスでの Synopsys 3G Ethernet PHY IP のファーストパス シリコンの成功は、高線形 PAM-4 アイを示しています。

1.6 Tbps イーサネットは、最も帯域幅が要求され、遅延に敏感なアプリケーション向けに調整されています。 224G SerDes テクノロジーの出現と、MAC および PCS IP の進歩により、進化する 1.6T イーサネット規格に継続的に準拠する包括的なソリューションが利用できるようになりました。さらに、プロトコルとエラー修正方法に固有のレイテンシーのため、データパスに不必要なレイテンシーが生じないよう、専門の設計者が IP デジタルおよびアナログ設計を入念に作成する必要があります。

1.6T SoC 設計で最高のパフォーマンスを達成するには、効率的に最適化されたアーキテクチャと、すべてのチップ コンポーネントの綿密な設計実践が必要です。これにより、省電力が重視され、シリコンの設置面積が最小限に抑えられ、1.6T のデータレートが実現します。 シリコンで実証済みの Synopsys 224G イーサネット PHY IP 1.6T MAC および PCS コントローラーの準備が整いました。シノプシスは、最先端の設計、解析、シミュレーション、測定技術を使用して、優れたシグナル インテグリティとジッター パフォーマンスを提供し続けています。 MAC+PCS+PHY を含む完全なイーサネット ソリューション.

- SEO を活用したコンテンツと PR 配信。 今日増幅されます。

- PlatoData.Network 垂直生成 Ai。 自分自身に力を与えましょう。 こちらからアクセスしてください。

- プラトアイストリーム。 Web3 インテリジェンス。 知識増幅。 こちらからアクセスしてください。

- プラトンESG。 カーボン、 クリーンテック、 エネルギー、 環境、 太陽、 廃棄物管理。 こちらからアクセスしてください。

- プラトンヘルス。 バイオテクノロジーと臨床試験のインテリジェンス。 こちらからアクセスしてください。

- 情報源: https://semiengineering.com/latency-considerations-for-1-6t-ethernet-designs/

- :持っている

- :は

- :not

- :どこ

- $UP

- 1

- 12

- 16

- 2024

- 2026

- 212

- 220

- 362

- 500

- 8

- a

- アクセス

- アクセス可能な

- 会計

- 正確な

- 達成する

- 越えて

- 活動

- 追加されました

- NEW

- さらに

- 採用

- 進歩

- 前進

- に対して

- 目指す

- 許可されて

- 既に

- また

- しかし

- 常に

- の中に

- 金額

- 増幅する

- an

- 分析

- および

- 予期された

- 申し込み

- アプローチ

- 建築

- です

- AS

- At

- 避ける

- バックエンド

- 背景

- 帯域幅

- BE

- になる

- の間に

- 越えて

- ビット

- ブロック

- ボルスター

- 後押し

- もたらす

- 構築します

- 焙煎が極度に未発達や過発達のコーヒーにて、クロロゲン酸の味わいへの影響は強くなり、金属を思わせる味わいと乾いたマウスフィールを感じさせます。

- by

- ケーブル

- ケーブル

- 缶

- 容量

- キャリー

- 課題

- チャンネル

- チップ

- チップ

- 選ばれた

- 状況

- クライアント

- 時計

- クラウド

- クラウドコンピューティング

- コード

- 組み合わせた

- 結合

- コミュニケーション

- コンプリート

- 完成

- コンポーネント

- コンポーネント

- 包括的な

- 備えます

- コンピューティング

- 懸念

- 共同

- 交流

- Connections

- 保全

- 検討

- 検討事項

- 整合性のある

- 続ける

- 連続的に

- 貢献する

- コントロール

- コントローラ

- 変換

- 銅

- 基本

- コスト

- 相殺する

- ここから

- 細工された

- 作成します。

- 電流プローブ

- データ

- データセンター

- デビュー

- 遅延

- 配信する

- 需要

- 厳しい

- 需要

- 描く

- 設計

- デザイナー

- デザイン

- 検出

- Devices

- 口述する

- 異なります

- デジタル

- 熱心に

- ディスプレイ

- 距離

- 配布

- そうではありません

- 倍増し

- 原因

- デュレーション

- 間に

- 各

- 前

- エコシステム

- 効果的な

- 効果的に

- 効率

- 効率的な

- 効率良く

- 努力

- 出現

- 強調

- 強調

- 採用

- 採用

- 可能

- 有効にする

- 包含する

- end

- 端から端まで

- 確実に

- 全体

- エラー

- エラー

- エスカレーション

- 本質

- 本質的な

- 本質的に

- エーテル(ETH)

- さらに

- あらゆる

- 明らか

- 進化

- 例

- 例外的

- 除外

- 拡大

- 拡大

- 予想される

- エキスパート

- 専門知識

- 伸ばす

- 延伸

- 外部

- 抽出

- 視線

- 要因

- 要因

- 遠く

- 速いです

- 特徴

- 特色

- フィギュア

- もう完成させ、ワークスペースに掲示しましたか?

- 名

- 初代

- フロー

- 焦点を当て

- 続いて

- フットプリント

- 処方

- フォワード

- FRAME

- から

- さらに

- 世代

- 与える

- 大きい

- グループ

- グループの

- 成長

- ハンド

- ハンドリング

- ハイ

- ハイパフォーマンス

- 非常に

- しかしながら

- HTML

- HTTPS

- 命令的

- 実装

- 重要性

- 重要

- 改善されました

- in

- その他の

- include

- 含めて

- の増加

- 個人

- インダストリアル

- 影響を受け

- 固有の

- 本質的に

- 開始する

- イニシアチブ

- 統合する

- 統合

- 整合性

- インタフェース

- インターフェース

- インターネット

- 相互運用性(インターオペラビリティ)

- に

- 本質的な

- 紹介する

- 紹介します

- 導入

- 関与

- IP

- IT

- 繰り返し

- ITS

- 自体

- JPG

- レーン

- レイテンシ

- 層

- 層

- 長さ

- レベル

- 活用

- 可能性が高い

- LINE

- ライン

- LINK

- リンク

- ライブ

- より長いです

- ロー

- MAC

- 作成

- 管理します

- 管理

- 最大幅

- 五月..

- 意味する

- 測定

- メカニズム

- ミディアム

- メモリ

- メッセージ

- 方法

- メソッド

- 細心の注意

- 最小限の

- 最小限に抑えます

- 最小化する

- 最小化

- モジュール

- モジュール

- 他には?

- 最も

- しなければなりません

- 近づいている

- 必要

- ネットワーク

- それにもかかわらず

- いいえ

- 注意

- 今

- 客観

- of

- 頻繁に

- on

- ONE

- の

- オペレーティング

- 最適化

- 最適化

- オプション

- or

- その他

- が

- 全体

- 足

- パラメータ

- 特に

- path

- パソコン

- 以下のために

- パフォーマンス

- 公演

- 物理的な

- 物理的に

- パイプライン

- 極めて重要な

- プラトン

- プラトンデータインテリジェンス

- プラトデータ

- 演劇

- さらに

- 潜在的な

- 電力

- プラクティス

- 主に

- 主要な

- プロセス

- 処理

- プロセッサ

- 進行

- 投影

- 保護

- パルス

- 目的

- 押す

- 品質

- ラジオ

- ランダム

- 範囲

- レート

- 価格表

- リーチ

- 到達

- 反応

- 現実

- 受け取ります

- 受け入れ

- レセプション

- 縮小

- 信頼性のある

- 残っている

- レンダリング

- 必要

- 制限されました

- 結果として

- 堅牢な

- 職種

- 根付いた

- ランニング

- スケーラビリティ

- 規模

- シナリオ

- シームレス

- 二番

- 見て

- セグメント

- 敏感な

- 別

- 役立つ

- サービス

- セッションに

- いくつかの

- shared

- ショート

- すべき

- 展示の

- シグナル

- 著しく

- シリコン

- サイズ

- So

- 溶液

- ソリューション

- スパン

- 先導する

- 特定の

- 特に

- 仕様

- 速度

- 春

- ステージ

- 標準

- 標準化

- 規格

- ストレージ利用料

- 作戦

- ストリーミング

- それに続きます

- かなりの

- 成功

- そのような

- 適当

- サポート

- シンボル

- テーラード

- 取り

- 技術

- テクニック

- テクノロジー

- より

- それ

- アプリ環境に合わせて

- そこ。

- それによって

- したがって、

- ボーマン

- この

- 介して

- 従って

- ダニ

- タイド

- 時間

- <font style="vertical-align: inherit;">回数</font>

- 〜へ

- top

- 伝統的な

- トラフィック

- 転送

- 送信します

- トリプル

- 2

- 典型的な

- 一般的に

- やむを得ない

- 理解する

- 引き受ける

- 単位

- 今後の

- に

- 活用する

- 、

- 視覚化する

- 仕方..

- we

- いつ

- which

- while

- より広い

- 以内

- でしょう

- まだ

- ゼファーネット

- ゼロ