複数の異種ダイをパッケージに統合することは、ムーアの法則を拡張し、パフォーマンス、電力効率、機能を向上させる上で極めて重要ですが、熱負荷の管理方法に関して重大な問題も引き起こしています。

高度なパッケージング これは、デジタル回路を単に縮小してレチクル サイズの SoC に多くの機能を詰め込むのではなく、さまざまなコンポーネントを垂直に積み重ねることによって、より多くの機能をデバイスに詰め込む方法を提供します。そのため、パフォーマンスと電力を最適化する方法に関する問題が生じます。単一のダイでは、信号経路を必要なだけ短くすることができ、基板は熱を効果的に放散します。しかし、パッケージ内に複数のダイがある場合、信号が伝わる距離を減らすために基板と誘電体をより薄くする必要があり、それにより熱放散が制限されます。

これによりホットスポットが発生する可能性があり、特にさまざまなワークロードやユースケースでは予測が困難な場合があります。また、さまざまな熱特性を持つ複数のチップまたはチップレットを 1 つのパッケージに統合すると、さらに状況が悪化する可能性があります。

「基板やインターポーザー上に複数のダイを配置するときは、常に困難が伴います」と、製品マーケティングおよびビジネス開発担当シニア ディレクターの Vik Chaudhry 氏は述べています。 Amkorテクノロジー。 「ベンダーが 3 つや 4 つだけでなく、8 つや 10 つ、あるいは 12 つものダイを配置しているのを目にしています。その熱をどうやって全体に分散させるのですか?」

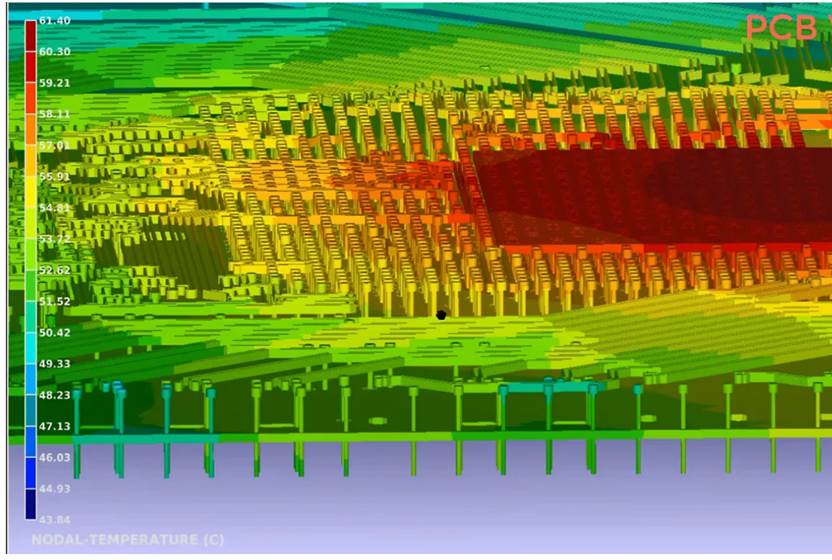

図 1: 熱電対における熱放散のシミュレーション。出典: アンシス

異種統合 熱を効果的に除去できるかどうかは、モジュール内に高密度に配置されたダイが信頼性の高い動作のために許容可能な温度を維持できるかどうかにかかっています。 IEEE の異種統合ロードマップでは、熱の流れを予測および管理するための高度なモデリング技術、高熱伝導率と低電気伝導率の両方を備えた新素材、複雑なパッケージにシームレスに統合できる新しい冷却ソリューションなど、開発ニーズのいくつかの分野が特定されています。

熱の不一致

異種統合における熱管理には、材料の選択が重要です。熱膨張係数 (CTE) が異なるコンポーネントが加熱および冷却されると、これらの材料は異なる速度で膨張および収縮します。これにより機械的ストレスが発生し、チップの完全性が損なわれ、チップをインターポーザーや他の基板に接続する結合が弱くなり、デバイスの全体的な機能に影響を与える可能性があります。

同様の CTE を持つ材料を採用すると、これらの応力が軽減され、早期故障のリスクの一部が軽減されるだけでなく、老化の促進、電子移動度の低下、アナログ信号や光信号のドリフトなど、その他の熱誘発効果も軽減されます。

「CTE はおそらく高度なパッケージングにとって最大の課題ですが、これを完全に理解している人は誰もいないと思います」と、同社 COO 兼エンジニアリング担当副社長の David Fromm 氏は述べています。 プロメックスインダストリーズ。 「私たちはこれまでに見たことのない方法で CTE を 3 次元スケールで扱っており、部品の歪みや破損に関するこれらの問題は非常に困難です。一部の企業は特定のプロセスについてそれを理解するかもしれませんが、その後、材料が変更され、デバイスのサイズが変更され、方程式が変更されます。そして、もう一度考え直さなければなりません。」

簡単に言うと、ヘテロジニアス集積には、パッケージ化されたデバイスの信頼性と歩留まりを最終的に形作る可能性があるすべての材料の熱膨張特性の基本的な理解が必要です。そしてそれは問題の一部にすぎません。高度なパッケージングでは、チップまたはチップレットの周囲に他に何があるのか、それらの他の要素がどのように使用されているのかを理解する必要があり、現実的なワークロードと予想されるものを使用してそれらすべてをモデル化し、一緒にシミュレーションする必要があります。この問題は、生成 AI によって処理する必要のあるデータ量が大幅に増加し、プロセッサとメモリの使用率が高くなっているデータ センターなど、コンピューティング ニーズが変化すると、さらに困難になります。

「常にある程度のレベルの熱分析は行われてきましたが、それは、手に負えないほどのことがないかどうかを確認するために、最後に行われました」と、同社の製品マーケティング担当ディレクターのマーク・スウィネン氏は述べています。 ANSYS。 「特定のジャンクション温度を目標にすることができ、それが準拠していれば、それは非常に簡単でした。しかし、マルチダイ システムでは、RTL フロア プランニングの段階でそれを行う必要があります。同じ動作モードで発熱する 2 つのチップが隣り合ったり、重なったりしないように、各チップの出力をある程度把握しておく必要があります。 。それはあなたのデザインを破滅させるでしょう。」

ふりだしに戻る

業界が異種統合ロードマップに対するさまざまな課題に取り組んでいる中、熱管理はもはや後回しではありません。それは、設計から製造までのフローから左にシフトし、さまざまなチップやチップレットの分割から優先順位付けに至るまで、インサーキットモニターがあらゆるものを評価および調整できる分野にシフトしました。

「悪魔は細部に宿る」とフロムは言う。 「これらの一見些細な設計と統合の決定は、望むものを構築できるかどうか、ましてや下流での歩留まりや製品の信頼性を備えたものを構築できるかどうかに多大な影響を与える可能性があります。適切な材料を選択すること、積み重ねについて考えること、プロセス フローについて考えることがすべて重要です。」

これは、データセンターから家庭用電化製品、自動運転車に至るまで、ますます多くの設計における根本的な変化を表しています。異種要素が一緒にパッケージ化されるため、 ファンアウト 柱と一緒に、 2.5D、特に 三次元IC 設計では、熱経路をより詳細に計画する必要があります。間違ったやり方をすると、複数のチップ/チップレットが詰まったパッケージ全体に損傷を与える可能性があり、問題の原因を見つけるだけでもコストがかかる可能性があります。

CHIPS National Advanced Packaging Manufacturing Program (NAPMP) の研究科学者、George Orji 氏は次のように述べています。 「高度なパッケージングではやり直しができないため、高度なパッケージング用のモノリシックチップ設計手法が必要です。」

異種混合統合システムに固有の複雑さのため、設計には学際的なアプローチが必要です。これは複雑なことであり、このアプローチを機能させる試みは新しいものではなく、平面スケーリングの前に失敗しました。デビッド・フリード氏、コーポレートバイスプレジデント ラムリサーチ氏は、最近のパネルディスカッションで、IBM が 3 年前にそこにいたときに 25D 異種統合を試みたと述べました。 「私たちは、その中の多くのプロセスコンポーネントをつなぎ合わせることができると考えました」と彼は言いました。 「しかし、最大の課題のいくつかは、設計と EDA 側にあり、どのテクノロジーを使用するかを分割し、システムのさまざまなコンポーネントをさまざまなチップ上でどのようにセグメント化し、それらを遡って再統合するかということでした。これが機能するには、設計と設計の最適化が必要です。」

それ以来何が変わったかというと、チップ業界には選択肢がなくなってしまったということだ。最先端のノードでチップを開発するにはコストが高くなりすぎており、レチクルのサイズによる制約も多すぎます。しかし、これはまだ難しい作業です。

設計者の負担を軽減するために、特にチップ構成がより複雑になり、統合された機能が増加するにつれて、先端材料科学とコンピュータ支援設計ツールを含む相乗技術がますます重要になっています。 「ここはまだやるべきことがあるのです」と Ansys の Swinnen 氏は付け加えます。 「すべての設計者が熱の専門家、電磁干渉の専門家、機械の専門家である必要がない方法で、この問題を解決するにはどうすればよいでしょうか?私たちのデザインコミュニティにそれを期待するのは非現実的です。」

これらの制約により、設計プロセスのいくつかの重要な側面で革新が必要になります。高密度に集積されたチップ内での発熱の多面的な性質を認識すると、定常状態だけでなく、主にユースケースやワークロードに基づく過渡的な熱イベントにも対処することが不可欠です。異種統合のロードマップには、均一な熱分布を確保するための 3D サーマル インターフェイス マテリアルや CTE に適合したヒート スプレッダなどの戦略が含まれています。

「複数のダイを使用すると、複数の熱影響源、複数の機械的勾配と温度勾配が存在します」と、同社のシニア製品マーケティング マネージャーのマヌエル モタ氏は述べています。 シノプシス。 「これらすべては設計段階で対処する必要があります。」

熱に関する考慮事項を設計プロセスに組み込むことは、複雑な半導体デバイスを実際に実現するための要件です。適切な材料やコンポーネントを特定するだけではありません。また、これらすべてが現場でどのように連携して機能するかを構想しています。

エンジニアが電子デバイスのパフォーマンスを向上させながらフォームファクターを削減すると、熱エンベロープが大幅に厳しくなります。最新のヒートスプレッダとサーマルインターフェース材料を活用して、さまざまな動作状態にわたる熱プロファイルを包括的に管理することは、意図したライフサイクルにわたってデバイスの完全性とパフォーマンスを維持するために不可欠になります。

「集積密度に対する最大の制限は熱です」と Swinnen 氏は言います。 「チップを積み重ねるのは簡単です。製造することも設計することもできますが、熱くなりすぎるため決して機能しません。したがって、熱はすべての 3D-IC チップ設計者の懸念事項の中心となっています。」

ヘテロジニアス集積における熱の課題を解決するには、熱を効果的に放散するために、シリコンなどの CTE が低い半導体と銅やアルミニウムなどの金属など、さまざまな材料を組み合わせる必要があります。残念ながら、この材料の組み合わせにより、反り、亀裂、はんだバンプの浮きが発生し、予想よりも早くデバイスが故障することがよくあります。これらの問題を克服するには、互換性のある特性を備えた新しい材料が必要です。

「これらの基板材料は、おそらく界面材料、接着剤、エポキシなどよりも開発が遅くなるでしょう」とフロム氏は言います。 「重要なのは、プロセス条件とそれをどのように管理するかです。加工面で私たちがより優れている点は、接着剤メーカーと協力して温度の変化を理解し、上流の設計レベルで温度の変化を考慮してこれらすべてのスタックがどのように進化するかを理解することです。」

材料の革新

熱に関する懸念は、チップの動作だけにとどまりません。製造面でも熱は問題となります。高度なパッケージ内のチップは、同じ CTE の問題のいくつかが問題になる可能性がある組み立ておよび製造に耐える必要があります。

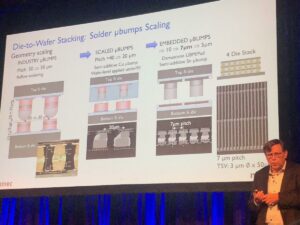

たとえば、熱圧着を使用してダイをウェーハに取り付ける一括ダイツーウェーハ (CoD2W) を考えてみましょう。 「CoD2W プロセスでは、異なるダイが異なるソースから供給され、高さや厚さが異なる場合があります」と、同社の先進技術 R&D 担当エグゼクティブ ディレクターのラマ プリガッダ氏は述べています。 ブリューワーサイエンス。 「これらのダイをキャリアに実装する場合、ボンディング中にすべてのダイがターゲットと接触するかどうかを知ることは非常に困難です。ダイアタッチ接着剤の機械的特性は、ボンディング中に背の高いダイがわずかに埋め込まれるように設計されており、これによりすべてのダイがターゲットウェハに良好に接触できるようになります。」

それはさまざまな問題を引き起こします。 「当社の材料の課題には、さまざまな金型の温度制限が含まれます」とプリガッダ氏は述べています。 「材料の接合に使用される温度が、パッケージに組み込まれているチップの熱制限を超えないようにする必要があります。さらに、再配線層の形成や成形などの後続プロセスがいくつかある場合があります。私たちの材料はそれらのプロセスに耐えなければなりません。包装プロセス全体を通じて接触する化学薬品に耐えなければなりません。パッケージ内の機械的応力により、材料の接合にさらなる課題が加わります。」

優れた熱伝導性と電気絶縁性を備えたさまざまな材料が開発中です。これらの新しく設計されたサーマル インターフェイス マテリアル (TIM) は、チップのパフォーマンスを妨げることなく、チップとそのクーラーの間に効率的な熱伝導経路を提供します。 TIM は熱伝導率の向上を誇るだけでなく、チップ表面全体での不均一な発熱によって引き起こされる微細な変化にも対応します。

「熱管理には、新しい熱材料だけでなく、高度な基板とヘテロジニアス統合を採用した新しい回路トポロジーも必要になります」と Orji 氏は言います。 「チップは互いに非常に近くに詰め込まれているため、余分な熱を拡散する能力は非常に限られています。」

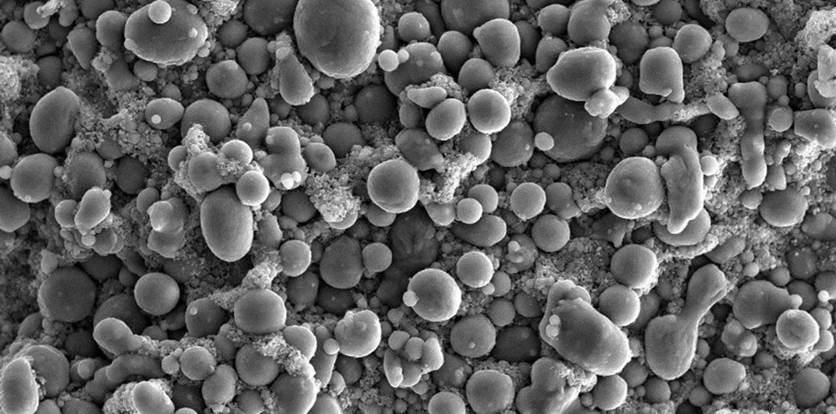

図 2: 粒子を含んだポリマー サーマル インターフェイス マテリアルの詳細図。出典: Amkor

理想的には、これらの新しい材料は、ダイヤモンドに見られる単純な原子構造に似た、強力な共有結合とバランスの取れたアニオンとカチオンの質量を示します。このカテゴリで認識されている材料には、ダイヤモンドのほか、酸化ベリリウム、窒化アルミニウム、窒化ホウ素、およびある程度の窒化ケイ素などの化合物が含まれます。これらの材料は、熱伝導能力にもかかわらず、その強度を提供するまさに結合によって製造上の問題が生じ、たとえば、所望の密度を達成するために高温焼結プロセスが必要となります。例外はダイヤモンドであり、焼結には適していません。

加工上の課題にもかかわらず、これらの材料の利点を活用するための 1 つのアプローチには、複合材料の利用が含まれます。たとえば、エポキシ複合材料内に窒化アルミニウムを組み込むと、熱処理上の利点が部分的に得られますが、固体セラミックの同等物の導電率レベルには匹敵しません。この材料特性の混合は、信号性能の低下を防ぐためにチップコアから十分な熱を奪う優れた導電体を有することが望ましいエレクトロニクスパッケージングにおいて極めて重要である。

ダイヤモンドは、その極めて高い硬度で有名であり、熱伝導体および絶縁体としての代表的な役割を果たしています。テフロン (ポリテトラフルオロエチレン、つまり PTFE) などのポリマー材料は、セラミックやダイヤモンドよりも導電性が劣るものの、熱を伝導し、信頼性の高い電気絶縁を提供する能力において、依然として多くのプラスチックを上回っています。 PTFE は、調理器具などの熱を大量に使用する用途のコーティング材料として使用するのに十分な効果があります。

ガラス、磁器、その他の緻密なセラミックは、これらの断熱性と熱伝導性を共有します。これらは、特に熱を管理するために優れた電気絶縁体も必要な場合に、実用的な解決策となります。窒化アルミニウム (AlN) は、半導体デバイスの絶縁体として利用され、ダイと熱伝達コンポーネントの間のギャップを橋渡しします。 AlN は酸化ベリリウムほど熱伝導性が高くありませんが、より安全でコスト効率の高い代替品となります。さらに、AlN は熱管理に関して、マイカ、ポリイミド、アルミナなどの標準的な絶縁体を上回っています。

合成サファイアは、手頃な価格とさまざまな形状に加工できることから注目に値し、半導体パッケージング分野におけるもう 1 つの貴重なプレーヤーとなっています。これらの材料はそれぞれ、電子性能を妨げずに熱を制御することが最も重要なパッケージ設計において独自の利点をもたらします。

ダイヤモンドや窒化アルミニウムなどの先端材料は、半導体デバイスの熱問題への取り組みの最前線にありますが、すべてのソリューションが特殊なコンポーネントや剛性の高いコンポーネントを必要とするわけではありません。サーマル グリースと接着剤は、電子パッケージングにおける結合組織として機能し、小さな隙間や表面の凹凸を埋め、さまざまな形状のコンポーネント間の熱伝達を促進します。表面に適合する機能は、より堅牢な熱管理ソリューションを補完する重要な機能を提供し、熱放散に対する包括的なアプローチを形成します。研究者らは、これらの材料の改良に重点を置いて、その熱伝導特性を強化し、熱管理パラダイムにおけるより効果的なパートナーにすることを目指しています。

「サーマル グリースやサーマル接着剤は熱伝導性があります」とフロム氏は付け加えます。「しかし、一般的なセラミックなどの熱伝導性の材料と比較すると、それらは 10 倍もひどい伝導体です。これらの材料はそれほど優れたものではありませんが、それには物理的および化学的な理由があります。そこでは達成されるべき多くの利点があり、その分野では多くの取り組みが行われています。」

今後

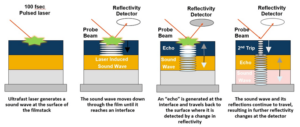

新しい素材が熱緩和への道を切り開くにつれて、革新的な新しい冷却技術も開発中です。基板にエッチングされたマイクロスケールの経路であるシリコンマイクロチャネルは、冷却剤をホットスポットの中心部に直接送ることができます。この直接冷却方式は従来のヒートシンクよりも優れていますが、設計、組み立て、信頼性の面で課題があります。

同様に、閉ループ液体冷却システムの開発により、空気流方式による制約を受けることなくコンポーネントを冷却状態に保つことができるようになります。これらのシステムは、サーマル スロットリングの脅威を伴わずに、より低い動作温度を保証しますが、液冷システムの設計とプロセス処理の両方で多くの研究を行う必要があります。

もう 1 つのオプションは、単純にスタックされたダイの構造を逆にすることです。つまり、ロジックの上にメモリを置く代わりに、ロジックをメモリの上に置き、その上にヒートシンクを置きます。その一例として、Winbond 社は、カスタマイズされた超帯域幅要素 (CUBE) テクノロジーでこれを提案しました。これは、SoC の上部ダイをメモリに直接積層し、シリコン貫通ビアを使用して基板に接続する高性能アプローチです。のマーケティング責任者、CS Lin 氏によると、このアプローチは次のとおりです。 Winbond社、消費電力が少なくなり、熱が下がります。さらに、熱を異種コンポーネントの迷路に通すのではなく、直接除去することができます。

もう 1 つのオプションは、AI を活用したリアルタイムの熱管理を使用することです。アルゴリズムにより、オンチップのさまざまな位置の温度を監視できるようになり、冷却リソースを動的に指示し、サーマルレッドラインを越えることなく最適なパフォーマンスを確保できます。たとえば、ProteanTecs はデータセンター向けのソリューションを発表したばかりで、チップを過熱から保護するために必要なガードバンディングの量を減らすことでサーバーの電力を削減できるとしています。このアプローチは、チップ内からの変更を監視し、必要に応じて調整を行うことに依存しています。

シノプシスとシーメンス EDA は、内部センサーを使用してさまざまな活動や温度変化を監視するソリューションも備えています。テレメトリを使用してパッケージ内部から情報を取得できることは、熱管理においてますます重要な要素となっています。

「チップ・オン・チップおよびインターポーザー上には数千または数百万のマイクロバンプを備えた機械的構造があり、それらはすべてチップが温まるにつれて膨張および収縮します」とスウィネン氏は付け加えます。 「サーマルマップに応じて、電力の完全性をローカルの温度プロファイルにリアルタイムで適応させる必要があります。チップがどのくらいの電力を出力するかを計算することはできますが、チップがどの程度の温度に達するかは依存します。それは冷たい皿の上に座っているのでしょうか、それともサハラ砂漠の太陽の下に座っているのでしょうか?同じチップと同じアクティビティでも、周囲の環境に応じて非常に異なる温度が発生する可能性があります。」

さらに、状態を変化させることで熱を吸収する相変化材料の研究は、受動的でありながら強力な温度調節を約束します。さらに、熱に対する人体の反応を模倣しようとする生物学的冷却システムの探求は、デバイスが汗をかくのと同じように直感的に熱を放散できる未来を予感させます。

まとめ

半導体業界が性能と統合の限界を押し広げ続ける中、高度なパッケージング内の熱管理は依然として課題となっています。一方では、企業がより高密度に実装されたマルチチップ モジュールを目指すにつれて、熱の複雑さが増大しています。逆に、材料科学の進歩と革新的な冷却技術は、結果として生じる熱ひずみを軽減しようと努めています。どちらも複雑な熱の課題に対処するために必要ですが、これを一貫して予測可能な方法で解決するには、まだ多くの作業が必要です。

— EdSperlingがこのレポートに貢献しました。

関連レディング

チップの熱誘起応力の管理

高度なノードでの異種統合と高密度化により、IC の製造とパッケージングに複雑で困難な課題が生じています。

- SEO を活用したコンテンツと PR 配信。 今日増幅されます。

- PlatoData.Network 垂直生成 Ai。 自分自身に力を与えましょう。 こちらからアクセスしてください。

- プラトアイストリーム。 Web3 インテリジェンス。 知識増幅。 こちらからアクセスしてください。

- プラトンESG。 カーボン、 クリーンテック、 エネルギー、 環境、 太陽、 廃棄物管理。 こちらからアクセスしてください。

- プラトンヘルス。 バイオテクノロジーと臨床試験のインテリジェンス。 こちらからアクセスしてください。

- 情報源: https://semiengineering.com/navigating-heat-in-advanced-packaging/

- :持っている

- :は

- :not

- :どこ

- $UP

- 1

- 10

- 12

- 25

- 3d

- 8

- a

- 能力

- できる

- 私たちについて

- 加速された

- ことができます。

- 従った

- 達成する

- 達成

- 越えて

- アクティビティ

- 適応する

- 加えます

- 添加

- NEW

- さらに

- 住所

- 対処する

- 追加

- 接着剤

- 調整します

- 調整

- 高度な

- 高度な素材

- 進歩

- 利点

- 影響を及ぼす

- 再び

- 高齢化

- 前

- 先んじて

- AI

- 目指す

- 目的としました

- 空気

- 同族の

- アルゴリズム

- すべて

- 緩和する

- 許す

- ことができます

- ALN

- 沿って

- また

- 代替案

- しかし

- 常に

- 量

- an

- 分析

- および

- 別の

- どれか

- アプローチ

- です

- エリア

- 周りに

- AS

- 側面

- アセンブリ

- 評価する

- At

- アトミック

- アタッチ

- 試み

- 注意

- 自律的

- 自律車両

- 離れて

- バック

- バランスのとれた

- ベース

- BE

- なぜなら

- になる

- になる

- になる

- き

- さ

- 利点

- より良いです

- の間に

- 越えて

- 最大の

- 絆

- 両言語で

- 境界

- 破壊

- ブリッジ

- もたらす

- ビルド

- 負担

- ビジネス

- 事業開発

- 焙煎が極度に未発達や過発達のコーヒーにて、クロロゲン酸の味わいへの影響は強くなり、金属を思わせる味わいと乾いたマウスフィールを感じさせます。

- by

- 計算する

- 缶

- 機能

- キャプチャ

- 例

- カテゴリー

- 応じます

- 原因となる

- 祝っ

- センター

- センター

- 中央の

- 一定

- 挑戦する

- 課題

- 挑戦

- 変化する

- 変更

- 変更

- 変化

- チェック

- 化学物質

- 化学品

- チップ

- チップ

- 選択肢

- 選択する

- 閉じる

- 冷たい

- 集団

- 集合的に

- 来ます

- comes

- コミュニティ

- 企業

- 比べ

- 互換性のあります

- 補体

- 複雑な

- 複雑さ

- 複雑さ

- 準拠した

- 複雑な

- コンポーネント

- コンポーネント

- 包括的な

- 妥協

- 計算

- 懸念

- 懸念事項

- 条件

- プロフェッショナルな方法で

- 導電率

- 導体

- お問合せ

- 検討事項

- 考えると

- 整合性のある

- 制約

- 建設

- consumer

- 家電

- 接触

- 続ける

- 縮小することはできません。

- 貢献

- 制御

- coo

- クール

- 銅

- 企業

- コスト効率の良い

- 高額で

- 可能性

- カウンターパート

- 共有結合

- 作成

- 重大な

- 横断

- 重大な

- カスタマイズ

- 損傷

- データ

- データセンター

- データセンター

- デイビッド

- 取引

- 決定

- 需要

- 密集

- 密度

- によっては

- 依存

- 設計

- 設計プロセス

- 設計

- デザイナー

- デザイナー

- デザイン

- 希望

- にもかかわらず

- 詳細

- 詳細な

- 細部

- 開発する

- 開発

- 発達上の

- デバイス

- Devices

- 悪魔

- ダイヤモンド

- 死

- 異なります

- 難しい

- デジタル

- 直接

- 演出

- 直接に

- 取締役

- 議論

- 距離

- 分配します

- ディストリビューション

- do

- ありません

- そうではありません

- 行われ

- ドント

- 運命

- ダウン

- 描画

- 描画

- ドライブ

- 原因

- 間に

- 動的に

- 各

- 前

- 簡単に

- ed

- 効果的な

- 効果的に

- 効果

- 効率

- 効率的な

- エレクトロニック

- 電子

- 要素は

- ほかに

- 埋め込まれた

- 出てくる

- 採用

- 可能

- end

- 設計された

- エンジニアリング

- エンジニア

- 高めます

- 強化

- 十分な

- 確保

- 確保する

- 全体

- 封筒

- 特に

- 本質的な

- さらに

- イベント

- あらゆる

- すべてのもの

- 進化

- 例

- 超えます

- 優れた

- 例外

- 過剰

- エグゼクティブ

- エグゼクティブ·ディレクター

- 展示

- エキゾチック

- 詳細

- 拡大

- 期待する

- 予想される

- 高価な

- エキスパート

- 探査

- 伸ばす

- 延伸

- エクステント

- 極端な

- 顔

- 容易化する

- 要因

- Failed:

- 失敗

- 不良解析

- 遠く

- 特徴

- フィールド

- イチジク

- フィギュア

- 考え出した

- 埋め

- 充填

- 発見

- フロー

- フォーカス

- 最前線

- フォーム

- 形成

- フォーム

- 前進

- 発見

- から

- 完全に

- function

- 機能性

- 機能

- 基本的な

- 未来

- ギャップ

- ギャップ

- 世代

- 生々しい

- 生成AI

- ジョージ

- 取得する

- 与えられた

- Go

- 行く

- 良い

- だ

- 勾配

- ハンド

- ハンドリング

- 出来事

- ハード

- 利用する

- 持ってる

- he

- ハート

- ハイツ

- ことができます

- ハイ

- ハイパフォーマンス

- より高い

- ヒンジ

- HOT

- 認定条件

- How To

- HTTPS

- 人間

- i

- IBM

- アイデア

- 識別する

- 識別

- if

- 影響

- 命令的

- 重要

- 課さ

- 改善されました

- 改善

- in

- include

- 含ま

- 含めて

- 組み込む

- 増加した

- の増加

- ますます

- 産業を変えます

- 固有の

- 革新的手法

- 革新的な

- 内部

- を取得する必要がある者

- 統合された

- 統合

- 統合

- 整合性

- 意図された

- インタフェース

- 干渉

- 干渉する

- 内部

- に

- 複雑な

- 関与

- 問題

- 問題

- IT

- ITS

- 自体

- JPG

- ただ

- キー

- 知っている

- 迷路

- 主として

- 最新の

- 法律

- 層

- つながる

- リード

- 左

- LEND

- less

- レベル

- レベル

- 活用

- wifecycwe

- フェイスリフト

- ような

- 制限

- 制限

- 限定的

- 制限

- LIN

- LINE

- 液体

- 負荷

- ローカル

- 場所

- ロジック

- より長いです

- たくさん

- ロー

- 下側

- 製

- 維持する

- make

- 作成

- 管理します

- 管理

- マネージャー

- 管理する

- メーカー

- 製造業

- 多くの

- 地図

- マーケティング

- 大衆

- 一致

- 材料

- 材料

- 最大幅

- 五月..

- 機械的な

- 思い出

- メモリ

- 金属

- 方法

- 方法論

- メソッド

- 雲母

- かもしれない

- 何百万

- マイナー

- 分

- 緩和する

- ミックス

- モビリティ

- モード

- モデリング

- モジュール

- モジュール

- モニター

- モニタリング

- モニター

- 一枚岩

- 他には?

- 最も

- ずっと

- 学際的

- の試合に

- しなければなりません

- 国民

- 自然

- ナビゲート

- 必要

- 必要

- 必要とされる

- ニーズ

- 決して

- 新作

- 新しく

- 次の

- いいえ

- ノード

- 何も

- 小説

- 今

- 数

- of

- 提供

- オファー

- 頻繁に

- on

- ONE

- の

- 操作

- オペレーショナル

- 反対

- 最適化

- 最適化

- 最適な

- オプション

- オプション

- or

- その他

- 私たちの

- でる

- 出力

- が

- 全体

- 克服する

- パック

- パッケージ

- パッケージ化された

- パッケージ

- 包装

- パック

- パネル

- パネルディスカッション

- パラダイム

- 最高の

- 部

- 特に

- パートナー

- 部品

- パッシブ

- パス

- 経路

- 舗装する

- パフォーマンス

- 相

- 物理的な

- ピース

- 柱

- 極めて重要な

- 場所

- 配置

- プラスチック

- プラトン

- プラトンデータインテリジェンス

- プラトデータ

- プレイヤー

- ポリマー

- 強力な

- 電力

- パワード

- 実用的

- 予測する

- 予測可能な

- 早漏

- プレゼント

- 社長

- 防ぐ

- 優先順位付け

- 多分

- 問題

- プロセス

- 処理されました

- ラボレーション

- 処理

- プロセッサ

- プロダクト

- プロフィール

- 対応プロファイル

- 演奏曲目

- 約束

- 約束

- プロパティ

- 守る

- 提供します

- は、大阪で

- 提供

- プッシュ

- 置きます

- パッティング

- R&D

- 提起

- 調達

- ランピング

- 範囲

- 価格表

- むしろ

- リアル

- への

- 現実的な

- 実現

- 本当に

- 理由は

- 最近

- 認識

- 認識

- レッド

- 減らします

- 電話代などの費用を削減

- 軽減

- 縮小

- に対する

- 規制

- 信頼性

- 信頼性のある

- 救済

- 残っている

- 削除します

- 削除済み

- レポート

- 表し

- 必要とする

- の提出が必要です

- 要件

- 必要

- 研究

- 研究者

- 解決する

- リソース

- 応答

- 結果

- 結果として

- 逆

- 右

- 堅い

- 上昇

- リスク

- ロードマップ

- 圧延

- ルート

- ラン

- s

- より安全な

- 前記

- 同じ

- 言う

- 規模

- スケーリング

- スキーム

- 科学

- 科学者

- シームレス

- 見ること

- 見て

- セグメント

- 半導体

- 半導体関連装置

- シニア

- センサー

- 役立つ

- サーバ

- いくつかの

- 形状

- シェアする

- シフト

- シフトした

- ショート

- 側

- ジーメンス

- シグナル

- 信号

- 重要

- 著しく

- シリコン

- 同様の

- 簡単な拡張で

- 単に

- から

- 座っている

- 状況

- サイズ

- サイズ

- ゆっくり

- 小さい

- So

- 固体

- 溶液

- ソリューション

- 解決する

- 一部

- 何か

- ソース

- ソース

- スペース

- スペクトラム

- 広がる

- スタック

- 積み上げ

- スタッキング

- スタック

- ステージ

- 標準

- スタンド

- 都道府県

- 米国

- 滞在

- まだ

- 作戦

- 力

- ストレス

- 努力する

- 強い

- 構造

- それに続きます

- そのような

- 日

- 優れた

- 表面

- しのぐ

- 凌駕する

- 生き残る

- 相乗的

- システム

- タックル

- ターゲット

- テクニック

- テクノロジー

- テクノロジー

- 10

- ひどい

- より

- それ

- ソース

- アプリ環境に合わせて

- それら

- その後

- そこ。

- サーマル

- ボーマン

- 彼ら

- 考える

- 考え

- この

- それらの

- しかし?

- 考え

- 数千

- 脅威

- 三次元の

- 介して

- 全体

- 時間

- 〜へ

- 一緒に

- あまりに

- 豊富なツール群

- top

- に向かって

- 伝統的な

- 転送

- 旅行

- すばらしい

- 試み

- しよう

- 順番

- 2

- 典型的な

- 最終的に

- 下

- わかる

- 理解する

- 残念ながら

- ユニーク

- UPS

- アップサイド

- つかいます

- ユースケース

- 中古

- 使用されます

- 利用された

- 活用

- 貴重な

- さまざまな

- 変化する

- 車

- ベンダー

- 垂直に

- 非常に

- バイス

- 副会長

- 詳しく見る

- 欲しいです

- 暖かい

- ました

- 仕方..

- 方法

- we

- WELL

- した

- この試験は

- 何ですか

- いつ

- かどうか

- which

- while

- なぜ

- 意志

- 以内

- 無し

- 仕事

- ワーキング

- もっと悪い

- 間違った

- 年

- まだ

- 産出

- 貴社

- あなたの

- ゼファーネット