銅の抵抗率は、その結晶構造、空隙量、粒界、および材料界面の不一致に依存し、これはスケールが小さくなるとより顕著になります。銅 (Cu) ワイヤの形成は伝統的に、トレンチ エッチング プロセスを使用して Low-k 二酸化シリコンにトレンチ パターンをエッチングし、続いてダマシン フローによってトレンチを Cu で充填することによって行われます。残念ながら、この方法では大きな粒界とボイドを備えた多結晶構造が生成され、Cu ワイヤの抵抗が増加します。このプロセスでは、ダマシン アニール プロセス中の Cu の拡散を防ぐために、高抵抗の TaN ライナー材料も使用されます。

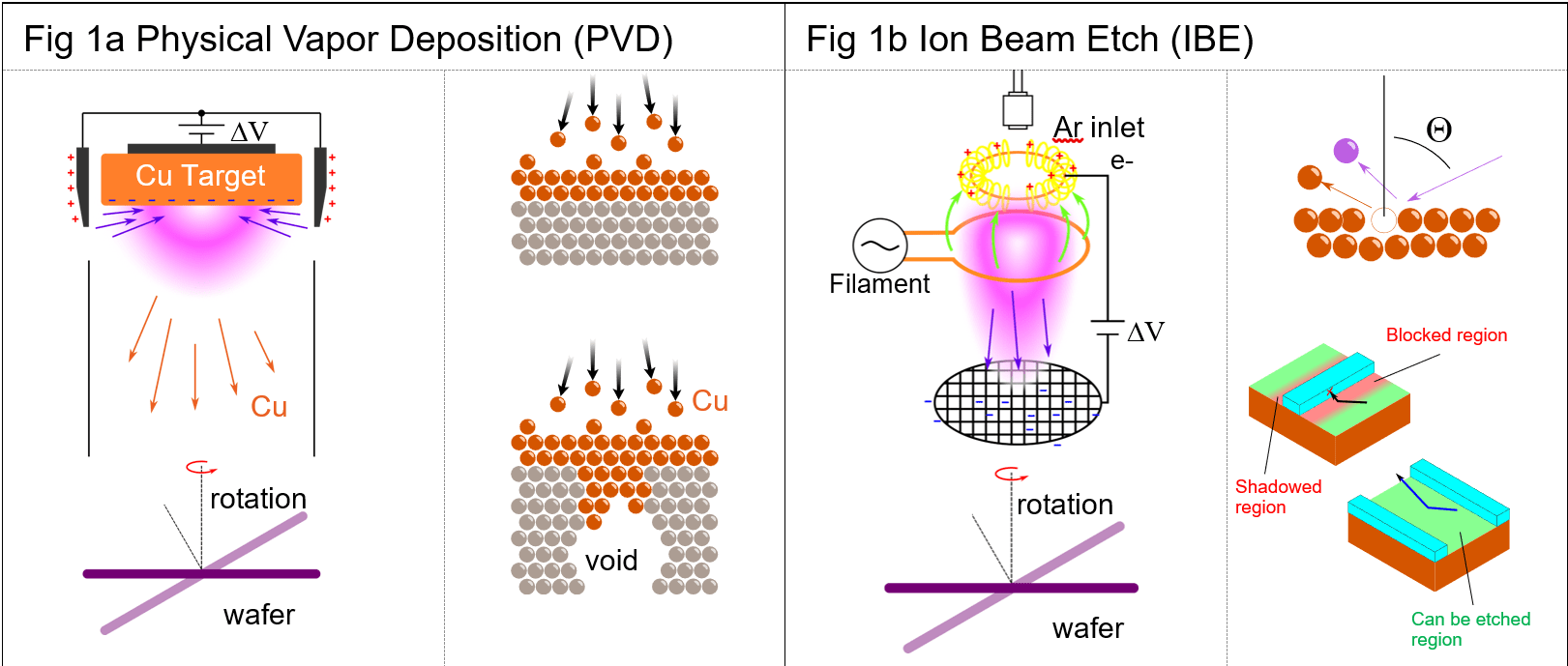

物理蒸着 (PVD) を使用すると、高い運動エネルギー (10 ~ 100 eV) で銅を蒸着し、低抵抗で緻密な単結晶構造を形成できます。 PVD の欠点は、PVD 堆積では視線が広がり、平らな表面にしか均一に堆積できないことです。深い穴や溝を埋めるのには使用できません (図 1a)。孤立したワイヤ形状を形成するには、均一な Cu 層を平坦な表面に堆積し、イオン ビームによって物理的にエッチングする必要があります。 Cu は反応性ガスによって揮発性化合物を形成しないため、反応性イオン エッチング プロセスは使用できません。イオンビームエッチング (IBE) 中に生成される加速された Ar イオンは、入射角が非常に高い場合に Cu を除去する可能性があります。残念ながら、エッチング可能な領域はマスクのシャドウイング効果により制限されます。図 1b は、マスクが入射イオン ビームに対して垂直である場合に材料がエッチングできない領域 (赤色) を示しています。このエッチングの失敗は、射出された原子の経路の遮蔽または遮断によって発生します。マスクがイオンの経路と平行である場合、マスクされていないすべての領域をエッチングできます。したがって、イオンビームエッチングは、任意の長さの線状マスクのエッチングに限定される。

![]()

図 1: (1a) 物理蒸着 (PVD)。 (1b) イオン ビーム エッチング (IBE)。

プロセスステップと仮想製造プロセス

ライン抵抗に対する堆積とエッチングの影響を理解するために、SEMulator3D 可視堆積およびエッチング機能を使用して PVD および IBE エッチング プロセスをモデル化します。 PVD は、SEMulator30D で 3 度の角度拡散可視蒸着プロセスを使用して再現されました。これは、AR イオンの衝突中に放出された Cu 原子のランダムな性質を正確にモデル化します。 IBE は、ビーム発散が小さいグリッド加速イオンの挙動を反映するために、2 度の角度広がりと 60 度の極角傾斜を備えた可視エッチングを使用してモデルで再現されました。両方のウェーハは自由に回転すると仮定されます。他のプロセスステップは、IBE および PVD の制約に対応するために仮想製造プロセスで調整されています。図 2 は、ダマシン Cu 充填 (図 2a) と PVD/IBE プロセス (図 2b) の両方を使用して作成された同じ構造を示しています。 PVD/IBE の特定の制限を組み込んで、目的の最終構造に相当する形状を作成するために、追加のプロセス ステップが含まれていました。

![]()

図 2: (2a) ダマシンフィル Cu ワイヤの製造。 (2b) PVD/IBE Cu ワイヤの製造。

次に、これらの制限を遵守しながら、同等の 16nm SRAM 回路セルを PVD/IBE ワイヤで製造できることを実証します。ラインの中間端より上のすべての金属層は平坦な表面から製造されるため、finFET デバイスに見られる複雑な相互接続トポロジとは異なり、PVD/IBE ワイヤのアイデア候補になります。図 3 は、各金属層の分離構造と、PVD/IBE を使用して XNUMX 金属層の FinFET 構造を作成するために必要な手順を示しています。

![]()

図 3: (3a) 16nm FinFET MEOL および 3 つの金属層。 (3b) PVD/IBE による段階的な金属層の製造。

抵抗の結果と結論

次に、ダマシン フローと物理蒸着の両方について、最上層の金属層から finFET の P および N チャネルのビアまでのワイヤの電気抵抗を測定します。図 4 は、P チャネルと N チャネルでの抵抗測定の開始点と終了点を示しています (他のすべての絶縁材料は透明です)。 TaN ライナーと銅線の間の界面抵抗を補償するために、TaN 界面への最近接距離の関数として 1 nm の指数関数的減衰定数を使用して銅の抵抗率を増加させました。ダマシン充填 Cu 堆積は完全に結晶質であるとは予想されないため、Cu の抵抗率は 50% 増加しました。 PVD/IBE 銅プロセスでは TaN ライナーが使用されないため、指数関数的減衰関数は適用されず、このモデルでは銅のバルク抵抗率が使用されました。ダマシンフローと PVD を比較した抵抗率の表を図 4 に示します。

![]()

図 4: P チャネルと N チャネルでの抵抗測定の開始点と終了点。

私たちのモデルから計算された抵抗値は、IBE/PVD 製造方法を使用すると、従来のトレンチ エッチングとそれに続くダマシン堆積と比較して、抵抗の 67% の減少を達成できることを示しています。これは、IBE/PVD では TaN ライナーが必要なく、このプロセス中の CU の抵抗率が低いために発生します。私たちの結果は、より複雑な製造プロセスを犠牲にして、金属線形成中にダマシン充填と比較して IBE/PVD を使用することで抵抗率の改善が達成できることを示しています。

ティモシー・ヤン

(すべての投稿)

Timothy Yang は、Lam Research Company である Coventor のソフトウェア アプリケーション エンジニアです。彼は、メモリ技術の専門知識を活かし、プロセス開発、統合、歩留まり向上のアプリケーションに取り組んでいます。 Coventor で働く前は、Yang は東京エレクトロンでエッチング スキーム、ポスト リソグラフィ パターン改善技術、SADP および SAQP パターニング アプリケーションのプロセス フロー制御、EUV および液浸リソグラフィ フォトレジスト技術の開発に従事していました。ヤンは、UCLA で物理学の学士号を取得し、千葉工業大学で材料科学の修士号を取得し、博士号を取得しました。東北大学で物質科学の学位を取得。

- SEO を活用したコンテンツと PR 配信。 今日増幅されます。

- Platoblockchain。 Web3メタバースインテリジェンス。 知識の増幅。 こちらからアクセスしてください。

- 未来を鋳造する w エイドリエン・アシュリー。 こちらからアクセスしてください。

- 情報源: https://semiengineering.com/a-deposition-and-etch-technique-to-lower-resistance-of-semiconductor-metal-lines/

- :持っている

- :は

- ][p

- 1

- 10

- 100

- a

- 上記の.

- 加速された

- 対応する

- 正確にデジタル化

- 達成する

- 達成

- NEW

- 調整

- すべて

- 全ての記事

- および

- 角度の

- 適用された

- AR

- です

- AS

- 想定される

- At

- 原子

- BE

- ビーム

- になる

- き

- の間に

- 境界

- by

- 計算された

- 缶

- 候補者

- 一定

- チャンネル

- 会社

- 比べ

- 比較

- 複雑な

- 定数

- 制約

- コントロール

- 従来の

- 銅

- 費用

- 作ります

- 作成した

- クリスタル

- データ

- 減少

- 深いです

- 度

- 実証します

- 依存

- 保証金

- 寄託

- 希望

- 開発

- 開発

- デバイス

- ディスプレイ

- 距離

- 発散

- ダウン

- 間に

- 各

- 効果

- 効果

- どちら

- エンジニア

- 同等の

- EV

- 予想される

- 専門知識

- 指数関数

- 不良解析

- フィギュア

- 埋める

- フラットな

- フロー

- 続いて

- フォーム

- 形成

- フォーム

- 無料版

- から

- 完全に

- function

- 機能

- グリッド

- 持ってる

- he

- ハイ

- 非常に

- 穴

- HTTPS

- アイデア

- イマージョン

- 改善

- 改善

- in

- 事件

- 含まれました

- 入ってくる

- 組み込む

- 増加した

- 増加

- 示す

- 機関

- 統合

- インタフェース

- 分離された

- IT

- ITS

- JPG

- ラム

- 層

- 層

- 制限

- 限定的

- LINE

- ライン

- 長い

- ロー

- 作る

- mask

- マスク

- 材料

- 材料

- 最大幅

- だけど

- メモリ

- 金属

- 方法

- 真ん中

- モデル

- 他には?

- 自然

- 必要

- 必要とされる

- of

- on

- 注文

- その他

- 私たちの

- 並列シミュレーションの設定

- path

- パターン

- 物理的な

- 物理的に

- 物理学

- プラトン

- プラトンデータインテリジェンス

- プラトデータ

- ポイント

- 極性の

- ポスト

- 投稿

- 防ぐ

- 事前の

- プロセス

- ラボレーション

- ランダム

- 受け

- レッド

- 反映する

- 地域

- 削除します

- 研究

- 結果

- s

- 同じ

- 秤

- スキーム

- 科学

- 半導体

- 形状

- 形

- シェイプ

- 作品

- 視力

- 重要

- シリコン

- から

- より小さい

- So

- ソフトウェア

- 広がる

- 起動

- 都道府県

- 手順

- ステップ

- 構造

- 続いて

- 表面

- テーブル

- テクニック

- テクノロジー

- テクノロジー

- それ

- ボーマン

- 三

- サムネイル

- 〜へ

- 東京

- 一番上の

- 伝統的に

- トランスペアレント

- UCLA

- わかる

- 大学

- つかいます

- 中古

- 利用された

- 価値観

- 、

- バーチャル

- 視認性

- ボリューム

- vs

- which

- while

- 意志

- ワイヤー

- 仕事

- 働いていました

- 作品

- 産出

- ゼファーネット