2010 年から 50 年間で、ムーアの法則の利点が崩れ始めました。 ムーアの法則によると、トランジスタ密度は 20 年ごとに XNUMX 倍になり、計算コストは対応して XNUMX% 縮小します。 ムーアの法則の変化は、平面デバイスから Finfet へのトランジスタ構造の進化により、設計の複雑さが増したことによるものです。 Finfet では、デバイスの寸法を XNUMX nm ノード未満にするために、リソグラフィ用に複数のパターニングが必要です。

この XNUMX 年間の初めに、主にデータセンターの急増と、生成および処理されるデータの量が原因で、コンピューティングのニーズが爆発的に増加しました。 実際、人工知能 (AI) や機械学習 (ML) などの技術の採用により、増え続けるデータの処理に使用されるようになり、サーバーのコンピューティング能力が大幅に向上しています。

サーバーにはさらに多くの CPU コアが追加され、グラフィックスには使用されなくなった ML 専用のより大きな GPU が統合され、カスタム ASIC AI アクセラレーターまたは補完的な FPGA ベースの AI 処理が組み込まれています。 初期の AI チップの設計は、より大きなモノリシック SoC を使用して実装され、そのうちのいくつかは、レチクルによって課せられたサイズ制限 (約 700mm) に達しました。2.

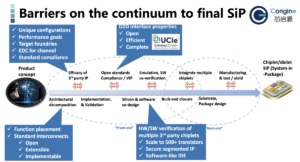

現時点では、より小さな SoC とさまざまなコンピューティングおよび IO チップレットへの分解が適切なソリューションのようです。 Intel、AMD、Xilinx などのいくつかのチップ メーカーは、生産に入る製品にこのオプションを選択しています。 The Linley Group の優れたホワイト ペーパー「Chiplets Gain Rapid Adoption: Why Big Chips Are Getting Small」では、このオプションがモノリシック SoC と比較してコストの削減につながることが示されました。

この傾向が IP ベンダーに与える主な影響は、主に SoC とチップレットをリンクするために使用される相互接続機能にあります。 この時点 (3 年第 2021 四半期) では、いくつかのプロトコルが使用されており、業界はそれらの多くに対して正式な標準を構築しようとしています。

現在の主要な D2D 標準には、i) Intel によって最初に定義され、現在はロイヤリティ フリーの使用を提供している Advanced Interface Bus (AIB、AIB2)、ii) DRAM ダイがシリコン インターポーザーの上に互いに積み重ねられている High Bandwidth Memory (HBM) が含まれます。 iii) 業界グループである Open Domain-Specific Architecture (ODSA) サブグループは、他の XNUMX つのインターフェイス、Bunch of Wires (BoW) と OpenHBI を定義しました。

異種チップレット設計により、システムの残りの部分を変更せずに、関連するチップレットのみを変更または追加することで、さまざまなアプリケーションまたは市場セグメントをターゲットにすることができます。 再設計はチップレットを収容するために使用されるパッケージ基板にのみ影響するため、大幅に少ない投資で、新しい開発をより迅速に市場に投入できます。

たとえば、コンピューティング チップレットを TSMC 5nm から TSMC 3nm に再設計して、システムの残りの部分を変更せずに、より大きな L1 キャッシュまたはより高性能な CPU コアを統合できます。 スペクトルの反対側では、SerDes を統合したチップレットのみが、新しいプロセス ノードでより高速なレートを実現するように再設計でき、より多くの IO 帯域幅を提供して市場でのポジショニングを向上させることができます。

Intel PVC は、同じチップ メーカーがさまざまなチップレット コンポーネント (メモリ デバイスを除く) を所有している場合、垂直統合と呼ぶことができる異種統合 (さまざまな機能チップレット、CPU、スイッチなど) の完璧な例です。

HPC、データセンター、AI、ネットワークなどのハイエンド アプリケーション向けの SoC を開発しているチップ メーカーは、チップレット アーキテクチャを早期に採用する可能性があります。 大規模な L3 キャッシュ用の SRAM や AI アクセラレータなどの特定の機能は、イーサネット、PCIe、または CXL 規格のいずれかが、チップレット設計の最初のインターフェイス候補となるはずです。

これらのアーリーアダプターが、複数の異なるビジネスモデルを活用する異種チップレットの有効性を実証し、明らかにテストとパッケージングの製造の実現可能性を実証すると、この新しいテクノロジーをサポートするために重要なエコシステムが作成されます。 この時点で、高性能アプリケーションだけでなく、より幅広い市場での採用が期待できます。

チップ メーカーがコンピューティングおよび IO 機能をターゲットとするさまざまなチップレットで構成されたシステムを市場に投入すれば、異種製品はさらに進化する可能性があると想像できます。 社内の D2D プロトコルを使用してチップレットを提供する IP ベンダーは業界にとって魅力的ではないため、このアプローチでは D2D プロトコルへの収束が必須になります。

これと類似しているのは、2000 年代の SoC 構築で、半導体企業はさまざまなソースからのさまざまな設計 IP の統合に移行しています。 2000 年代の IP ベンダーは、2020 年代のチップレット ベンダーになることは避けられません。 高度な SerDes や PCIe、イーサネット、CXL などの複雑なプロトコルなどの特定の機能については、IP ベンダーがシリコン上に実装するための最良のノウハウを持っています。

複雑なデザイン IP の場合、顧客に出荷する前にシミュレーション検証が実行されたとしても、ベンダーはパフォーマンスを保証するためにシリコン上で IP を検証する必要があります。 デジタル IP の場合、FPGA で機能を実装できます。これは、テスト チップを作成するよりも高速ではるかに安価であるためです。 SerDes ベースの PHY のような混合信号 IP の場合、ベンダーはテスト チップ (TC) オプションを選択して、顧客に出荷する前にシリコンで IP を特性評価できるようにします。

チップレットは単なる TC ではありませんが、フィールドで使用される前に広範囲にテストされ、認定されるため、製品チップレットを開発するためにベンダーが行う増分作業の量ははるかに少なくなります。 言い換えれば、IP ベンダーは、独自の IP から構築されたチップレットを迅速にリリースし、可能な限り最高の TTM を提供し、リスクを最小限に抑えるのに最適な立場にあります。

異種統合のビジネス モデルは、関連する IP ベンダーによって作成されたさまざまなチップレットを支持しています (たとえば、ARM ベースの CPU チップレットには ARM、Risc-V ベースのコンピューティング チップレットには Si-Five、高速 SerDes チップレットには Alphawave)。彼らは設計 IP の所有者です。

これは、チップ メーカーが独自のチップレットを設計し、複雑な設計 IP をソースして、独自のアーキテクチャを保護したり、自社製の相互接続を実装したりすることを妨げるものではありません。 2000 年代の SoC 設計 IP と同様に、チップレットの購入または決定は、コア コンピテンシーの保護と差別化されていない機能の調達の間で重み付けされます。

2000 年代以降の歴史的および現代的なデザイン IP ビジネスの成長は、外部調達の継続的な採用によって維持されてきました。 両方のモデルが共存しますが (社内または IP ベンダーによって設計されたチップレット)、購入の決定が最終的に成功することを歴史が示しています。

業界では、ムーアの法則を達成することにマニアックに焦点を当てることは、高度な技術ノードにはもはや有効ではないというコンセンサスがあります。 7nm以下。 チップの統合はまだ行われており、新しいテクノロジ ノードごとに XNUMX 平方 mm あたりのトランジスタが追加されています。 ただし、トランジスタあたりのコストは、新しいノードごとに増加しています。

チップレット技術は、古いノードを他の機能に使用しながら、メイン SoC の統合を促進するための重要なイニシアチブです。 このハイブリッド戦略により、他のデザイン IP をメイン SoC に直接統合することに伴うコストとデザイン リスクの両方が減少します。

IPnest は、この傾向がインターフェイス IP ビジネスに 2 つの主な影響を与えると考えています。2021 つは、D2025D IP 収益の急速な成長 (XNUMX 年から XNUMX 年) であり、もう XNUMX つは、ハイエンド シリコンを増強する異種チップレット市場の創出です。 IP市場。

この市場は、PCIe、CXL、イーサネットなどの複雑なプロトコル機能で構成されると予想されます。 I/O SoC (USB、HDMI、DP、MIPI など) に統合されたインターフェイス IP を提供する IP ベンダーは、代わりに I/O チップレットを提供することを決定する場合があります。

この革命によって影響を受ける他の IP カテゴリは、L3 キャッシュ用の SRAM メモリ コンパイラ IP ベンダーです。 本来、キャッシュ サイズはプロセッサによって異なると予想されます。 それにもかかわらず、L3 キャッシュ チップレットを設計することは、IP ベンダーが新しい製品タイプを提供することで設計 IP の収益を増やす方法になる可能性があります。

同様に、NVM IP は高度なプロセス ノードで設計された SoC に統合されなくなったため、NVM IP カテゴリはプラスの影響を受ける可能性があります。 これは、NVM IP ベンダーがチップレットを提供することで新しいビジネスを生み出す方法となります。

FPGA および AI アクセラレータ チップレットは、ASSP チップ メーカーの新たな収益源になると考えていますが、厳密に IP ベンダーとしてランク付けできるとは考えていません。

インターフェイス IP ベンダーがこのシリコン革命の主役になるとすれば、TSMC や Samsung などの最先端ノードに対応するシリコン ファウンドリも重要な役割を果たすことになります。 ファウンドリがチップレットを設計するとは考えていませんが、IP ベンダーをサポートする決定を下し、3nm の SoC で使用するチップレットを設計するように促す可能性があります。これは、高度な IP ベンダーがハイエンドの SerDes を販売するのをサポートする場合と同様です。 7nm と 5nm のハード IP として。

インテルの最近の 3 への移行rd パーティのファウンドリーもサードパーティの IP を活用することが期待されており、半導体の大物による異種チップレットの採用も期待されています。 この場合、Microsoft、Amazon、Google などのハイパースカラーもチップレット アーキテクチャを採用することは間違いありません。

By エリック・エステベ (PhD.) アナリスト、IPnest オーナー

- 2021

- 加速器

- 加速器

- 養子縁組

- 先進技術

- AI

- 許可

- Amazon

- AMD

- アナリスト

- 建築

- ARM

- 人工知能

- 人工知能(AI)

- ASIC

- BEST

- ビルド

- 建物

- 束

- バス

- ビジネス

- ビジネスモデル

- 購入

- コール

- 容量

- 変化する

- チップ

- チップ

- 到来

- 企業

- 計算

- コンピューティング

- コンセンサス

- コスト

- Customers

- データ

- 配信する

- 設計

- 開発する

- Devices

- デジタル

- 早い

- 早期採用者

- エコシステム

- 等

- 進化

- 名

- フォーカス

- FPGA

- 無料版

- function

- でログイン

- GPU

- グループ

- 成長

- 成長性

- ハイ

- history

- お家の掃除

- HTTPS

- ハイブリッド

- 影響

- 増える

- 産業を変えます

- イニシアチブ

- 統合

- インテル

- インテリジェンス

- 投資

- IP

- IT

- 保管

- キー

- 起動する

- 法律

- 主要な

- 学習

- ツェッペリン

- 活用します

- LINK

- 機械学習

- 主要な

- メーカー

- 作成

- 製造業

- 市場

- Microsoft

- ML

- ネットワーキング

- 新製品

- ノード

- 提供

- 提供すること

- 開いた

- オプション

- その他

- 所有者

- 包装

- 紙素材

- パフォーマンス

- プロダクト

- 生産

- 製品

- 守る

- 保護

- 価格表

- 再設計

- REST

- リスク

- ラン

- サムスン

- 半導体

- 発送

- サイズ

- 規格

- 戦略

- サポート

- スイッチ

- ターゲット

- テクニック

- テクノロジー

- test

- top

- us

- USB

- ベンダー

- Verification

- ホワイトペーパー

- 言葉

- 仕事

- 年

- 産出