過去 25 年間の半導体業界の拡大を見ると、あらゆるアプリケーションでの設計 IP の採用が成功の主要な要因の 100 つであるように見えます。シリコン テクノロジーは 250 年の 2018nm から 3nm まで、2 倍の驚異的な発展を遂げています。私たちは、チップレットベースのアーキテクチャへの移行が、2023 年代に SoC チップベースのアーキテクチャと設計 IP の大量使用が果たしたのと同じ役割を果たすことになると予測しています。

問題は、チップレットの採用時期をどのように正確に予測するか、そしてこの革命を可能にする鍵となるものは何かということです。イノベーション理論の普及が予測を微調整し、どのタイプのアプリケーションが推進力となるかを判断するのに役立つかどうかを見ていきます。業界での迅速な導入を可能にし、IA やスマートフォン アプリケーション プロセッサなどのアプリケーションを迅速に推進する、チップ間相互接続プロトコルの標準仕様が最大の実現要因であるように見えますが、特に EDA ツールの効率化や新しいテクノロジーのパッケージ化、専用ファブの作成などが確実に鍵となります。

はじめに: チップレット技術の出現

2010 年から 50 年間で、ムーアの法則の利点が崩れ始めました。 ムーアの法則によると、トランジスタ密度は 20 年ごとに XNUMX 倍になり、計算コストは対応して XNUMX% 縮小します。 ムーアの法則の変化は、平面デバイスから Finfet へのトランジスタ構造の進化により、設計の複雑さが増したことによるものです。 Finfet では、デバイスの寸法を XNUMX nm ノード未満にするために、リソグラフィ用に複数のパターニングが必要です。

この 700 年の終わりに、主にデータセンターの急増と、生成および処理されるデータの量により、コンピューティングのニーズが爆発的に増加しました。実際、人工知能 (AI) や機械学習 (ML) などの技術の導入により、増え続けるデータの処理に使用されており、サーバーのコンピューティング能力が大幅に向上しています。サーバーにはさらに多くの CPU コアが追加され、グラフィックスには使用されなくなった ML 専用に使用される大型の GPU が統合され、カスタム ASIC AI アクセラレータまたは補完的な FPGA ベースの AI 処理が組み込まれています。初期の AI チップ設計は、より大きなモノリシック SoC を使用して実装されており、その一部はレチクルによって課せられるサイズ制限 (約 XNUMXmm) に達していました。2.

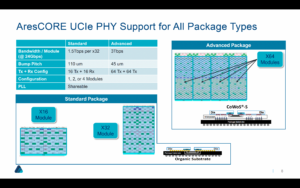

現時点では、より小さな SoC とさまざまなコンピューティングおよび IO チップレットに分散することが正しい解決策であるように見えます。 Intel、AMD、Xilinx などのいくつかのチップ メーカーは、量産に入る製品にこのオプションを選択しています。 The Linley Group の優れたホワイト ペーパー「チップレットが急速に普及: 大型チップが小型化する理由」では、このオプションがモノリシック SoC と比較して、大型化による歩留まりの影響によりコストの向上につながることが示されています。これらのチップ メーカーは同種チップレットを設計しましたが、Universal Chiplet Interconnect Express (UCIe) IP などの相互接続規格の出現と採用により、異種チップレットの採用が容易になりました。

業界がより高いパフォーマンスを求め続ける中、より新しく高速なプロトコル標準の進化は加速しています。残念ながら、さまざまな標準が単一の組織によって同期されていません。新しい PCIe 標準は、新しいイーサネット プロトコル標準より 5 年 (またはそれ以上) 早く、または遅くなる可能性があります。ヘテロジニアス統合を使用すると、シリコン プロバイダーは、関連するチップレットの設計のみを変更するだけで、急速に変化する市場に適応できます。高度な SoC 設計の製造には 4nm、3nm、または XNUMXnm プロセス ノードに多額の設備投資が必要であることを考慮すると、チップレット アーキテクチャの影響は半導体分野における将来のイノベーションを推進する上で多大です。

異種チップレット設計により、システムの残りの部分は変更せずに、関連するチップレットのみを変更または追加することで、さまざまなアプリケーションや市場セグメントをターゲットにすることができます。再設計はチップレットを収容するために使用されるパッケージ基板にのみ影響を与えるため、大幅に少ない投資で、新しい開発をより迅速に市場に投入できる可能性があります。たとえば、コンピューティング チップレットを TSMC 5nm から TSMC 3nm に再設計して、システムの残りの部分を変更せずに、より大規模な L1 キャッシュやより高性能な CPU や CPU コア数を統合できます。 SerDes を統合するチップレットは、新しいプロセス ノードでの高速化のために再設計され、より多くの IO 帯域幅を提供して市場でのポジショニングを向上させることができます。

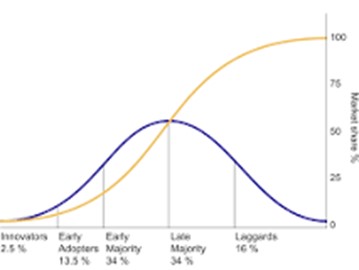

異種チップレットを使用すると、システムを更新する際の市場投入までの時間 (TTM) が向上し、チップレットで設計されている場合はシステムの一部を変更せずに再利用できます。これは、一部の機能チップレットを最先端のノードよりも安価な、あまり高度でないノードに維持する場合のコストを最小限に抑える方法でもあります。しかし、主な疑問は、チップレット技術が半導体市場の重要な部分を生み出す時期を予測することです。チップレットと IP は類似しており、成功するにはどちらも NIH 症候群を打破する必要があるため、IP 導入の歴史を確認します。イノベーション理論と定義されたカテゴリー (イノベーター、アーリーアダプターなど。以下の図を参照) を使用して、チップレット採用の主な原因を抽出し、予測を構築します。

1991 年から 2018 年までの ARM CPU IP 採用と 1995 年から 2027 年までの IP 採用履歴をレビューし、この採用率がイノベーション理論とどのように一致しているかを確認します。

テクノロジーとマーケティング関連の理由を検討しながら、なぜチップレットの採用が促進されるのかを説明します。

- IPベースのSoCからチップレットベースのシステムへ

- チップレット相互接続優先プロトコル標準による相互運用性

- ハイエンド インターフェイス IP がチップレット採用の鍵となる理由を説明する

- 解決すべきデザイン関連の課題。

- 最後になりますが、ファウンドリによる投資も重要です。

最後に、イノベーション理論に基づいて、暫定的なチップレット採用予測を構築できます。言及しておきますが、業界は「アーリーアダプター」フェーズに移行したばかりで、数多くの IP およびチップレット ベンダーが HPC と AI にサービスを提供しています。

ダウンロードした場合 ホワイトペーパー全てのテキストと、この作品のために描き下ろされた多数の写真でお楽しみいただけます。

By エリック・エステベ (PhD.) アナリスト、IPnest オーナー

Alphawave はこのホワイト ペーパーの作成を後援しましたが、意見と分析は著者のものです。 記事はここにあります:

https://awavesemi.com/resource/will-chiplet-adoption-to-mimic-ip-adoption/

また読む:

1.6T エコシステムの解放: AI データ インフラストラクチャを強化する Alphawave Semi の 200G 相互接続テクノロジー

分散システム: UCIe インターコネクトとチップレットベースの設計によるコンピューティングの実現

2022 年のインターフェース IP: 依然としてデータ中心の成長が続く前年比 22%

この投稿を共有する:

- SEO を活用したコンテンツと PR 配信。 今日増幅されます。

- PlatoData.Network 垂直生成 Ai。 自分自身に力を与えましょう。 こちらからアクセスしてください。

- プラトアイストリーム。 Web3 インテリジェンス。 知識増幅。 こちらからアクセスしてください。

- プラトンESG。 カーボン、 クリーンテック、 エネルギー、 環境、 太陽、 廃棄物管理。 こちらからアクセスしてください。

- プラトンヘルス。 バイオテクノロジーと臨床試験のインテリジェンス。 こちらからアクセスしてください。

- 情報源: https://semiwiki.com/chiplet/339927-will-chiplet-adoption-mimic-ip-adoption/

- :持っている

- :は

- :not

- $UP

- 1

- 1995

- 200

- 2018

- 2022

- 2023

- 25

- a

- 私たちについて

- 加速器

- 達成する

- 適応する

- 追加されました

- 追加

- 採用者

- 養子縁組

- 高度な

- AI

- AIデータ

- すべて

- 許可

- ことができます

- また

- AMD

- 間で

- 量

- 分析

- アナリスト

- および

- 離れて

- 登場する

- 申し込み

- 建築

- です

- ARM

- 記事

- 人工の

- 人工知能

- 人工知能(AI)

- AS

- ASIC

- 質問

- At

- 著者

- 帯域幅

- ベース

- BE

- になる

- 始まった

- さ

- 以下

- 利点

- より良いです

- ビッグ

- ブーストされた

- 両言語で

- ブレーク

- ビルド

- 焙煎が極度に未発達や過発達のコーヒーにて、クロロゲン酸の味わいへの影響は強くなり、金属を思わせる味わいと乾いたマウスフィールを感じさせます。

- by

- キャッシュ

- 缶

- 容量

- 資本

- カテゴリー

- 原因

- 確かに

- 課題

- 変化する

- 変化

- 安い

- チェック

- チップ

- チップ

- 来ます

- 比べ

- 補完的

- 複雑さ

- 計算

- コンピューティング

- 考えると

- 対応する

- 費用

- コスト

- 可能性

- CPU

- 作ります

- 作成した

- 創造

- カスタム

- データ

- 十年

- 専用の

- 定義済みの

- 密度

- 設計

- 設計

- デザイン

- 決定する

- 開発

- 進展

- Devices

- 異なります

- 大きさ

- 倍増

- ダウンロード

- ドライブ

- ドライバー

- 運転

- 原因

- 間に

- 前

- 早い

- 早期採用者

- イージング

- エコシステム

- 効率

- 埋め込まれた

- 出現

- イネイブラー

- 有効にする

- end

- 楽しみます

- 等

- 増え続ける

- あらゆる

- 進化

- 例

- 優れた

- 排他的に

- 拡大

- 説明する

- 表現します

- エキス

- 実際

- 要因

- 要因

- 秋

- スピーディー

- 速いです

- フィギュア

- 予想

- 予見する

- 発見

- FPGA

- から

- 機能的な

- 未来

- 利得

- 生成された

- 受け

- 行く

- GPU

- グラフィック

- グループ

- 成長性

- 持ってる

- 役立つ

- こちら

- ハイエンド

- より高い

- history

- お家の掃除

- 認定条件

- How To

- hpc

- HTTPS

- ia

- if

- 影響

- 実装

- 課さ

- in

- 増加した

- の増加

- 信じられない

- 産業を変えます

- 革新的手法

- イノベーター

- 統合する

- 統合された

- 統合

- 統合

- インテル

- インテリジェンス

- インタフェース

- に

- 投資

- IP

- IT

- JPG

- ただ

- 保管

- キー

- より大きい

- 姓

- 後で

- 打ち上げ

- 法律

- リード

- 学習

- 最低

- ツェッペリン

- less

- ような

- LIMIT

- より長いです

- 見て

- 下側

- 機械

- 機械学習

- 製

- メイン

- 主要な

- メーカー

- 多くの

- 市場

- マーケティング

- 大規模な

- 言及

- 最小限に抑えます

- ML

- 一枚岩

- 他には?

- 最も

- 主に

- 移動

- の試合に

- 必要

- ニーズ

- 新作

- 新技術

- より新しい

- NIHの

- いいえ

- ノード

- 今

- 数

- 多数の

- of

- 提供

- 提供すること

- on

- ONE

- の

- 意見

- オプション

- or

- 組織

- その他

- 所有者

- パッケージ

- 包装

- 紙素材

- 部

- パフォーマンス

- 実行

- 相

- 博士号

- PHP

- ピッキング

- ピクチャー

- プラトン

- プラトンデータインテリジェンス

- プラトデータ

- プレイ

- 演奏

- さらに

- ポイント

- ポジショニング

- ポスト

- 電源

- 正確に

- 予測する

- 予測

- 優先

- プロセス

- 処理されました

- 処理

- プロセッサ

- 生産

- 製品

- プロバイダ

- 質問

- より速い

- すぐに

- 急速な

- レート

- 価格表

- 到達

- 読む

- 理由は

- 再設計

- 再設計されました

- 関連する

- 関連した

- リマインダー

- 必要

- REST

- レビュー

- レビュー

- 革命

- 右

- 職種

- 同じ

- 見ること

- と思われる

- セグメント

- セグメント

- select

- 半導体

- サーバ

- サービング

- いくつかの

- 示す

- 重要

- 著しく

- シリコン

- 同様の

- サイズ

- より小さい

- スマートフォン

- 溶液

- 解決する

- 一部

- すぐに

- スペース

- 仕様

- スピード

- スポンサー

- 標準

- 規格

- 明記

- スティック

- まだ

- 構造

- 成功

- 成功した

- システム

- ターゲット

- テクニック

- テクノロジー

- テクノロジー

- 클라우드 기반 AI/ML및 고성능 컴퓨팅을 통한 디지털 트윈의 기초 – Edward Hsu, Rescale CPO 많은 엔지니어링 중심 기업에게 클라우드는 R&D디지털 전환의 첫 단계일 뿐입니다. 클라우드 자원을 활용해 엔지니어링 팀의 제약을 해결하는 단계를 넘어, 시뮬레이션 운영을 통합하고 최적화하며, 궁극적으로는 모델 기반의 협업과 의사 결정을 지원하여 신제품을 결정할 때 데이터 기반 엔지니어링을 적용하고자 합니다. Rescale은 이러한 혁신을 돕기 위해 컴퓨팅 추천 엔진, 통합 데이터 패브릭, 메타데이터 관리 등을 개발하고 있습니다. 이번 자리를 빌려 비즈니스 경쟁력 제고를 위한 디지털 트윈 및 디지털 스레드 전략 개발 방법에 대한 인사이트를 나누고자 합니다.

- より

- 感謝

- それ

- アプリ環境に合わせて

- それら

- 理論

- ボーマン

- この

- それらの

- 介して

- 時間枠

- 〜へ

- 豊富なツール群

- top

- すばらしい

- tsmc

- 2

- type

- 残念ながら

- ユニバーサル

- 更新

- us

- つかいます

- 中古

- さまざまな

- ベンダー

- 、

- ました

- 仕方..

- we

- した

- この試験は

- いつ

- while

- 白

- ホワイトペーパー

- なぜ

- 意志

- 仕事

- でしょう

- 年

- 年

- 産出

- 貴社

- ゼファーネット