今日の半導体設計から製造までのプロセスにおいて系統的欠陥の伝播を防ぐには、多くの検証、分析、最適化のステップが必要です。このプロセスに関連するツールには、デザイン ルール チェック (DRC)、光近接効果補正 (OPC) 検証、マスク書き込みおよびウェーハ プリンティング計測/検査 (プロセスを評価するため)、ウェーハ プリンティング計測/検査、および故障を確認するための物理的故障解析が含まれます。診断。これらのステップ間の情報交換と共同最適化は、多くのフィードフォワード ループとフィードバック ループを伴う複雑なプロセスです。プロセステクノロジーのさまざまな部分の間にある「壁」によってコミュニケーションが妨げられることが多く、イノベーションが遅れています。最近の SPIE カンファレンスで、シーメンス EDA は、これらの壁を打ち破ってチップ設計から製造プロセスまでを改善するための一連のアプローチを提案する基調講演を行いました。シーメンスが設計テクノロジーの協調最適化を拡張することで、イノベーションの障壁をどのように打破することを目指しているかを読んでください。

基調講演について

SPIE は光学とフォトニクスの国際学会です。この組織の起源は 1955 年に遡り、そのカンファレンスは高度な設計と製造のトピックを扱う主要なイベントとなっています。今年のイベントで、シーメンスはこの投稿のテーマである基調講演を行いました。このプレゼンテーションには、Le Hon、Fan Jiang、Yuansheng Ma、Srividya Jayaram、Joe Kwan、Siemens EDA (米国) を含む多くの寄稿者が参加しました。 Doohwan Kwak、シーメンス EDA (韓国); Sankaranarayanan Paninjath Ayyappan、シーメンス EDA (インド)。講演のタイトルは、 設計テクノロジーの共同最適化をテクノロジーの立ち上げから HVM まで拡張.

この講演は、設計技術の協調最適化 (DTCO) に関するセッションの一部でした。この概念は新しいものではありませんが、シーメンスは、設計から大量生産 (HVM) まで、プロセスのより広い範囲にわたってその適用を検討しました。提示されたアイデアと結果は重要な意味を持ちます。詳しく見てみましょう。

提示された内容

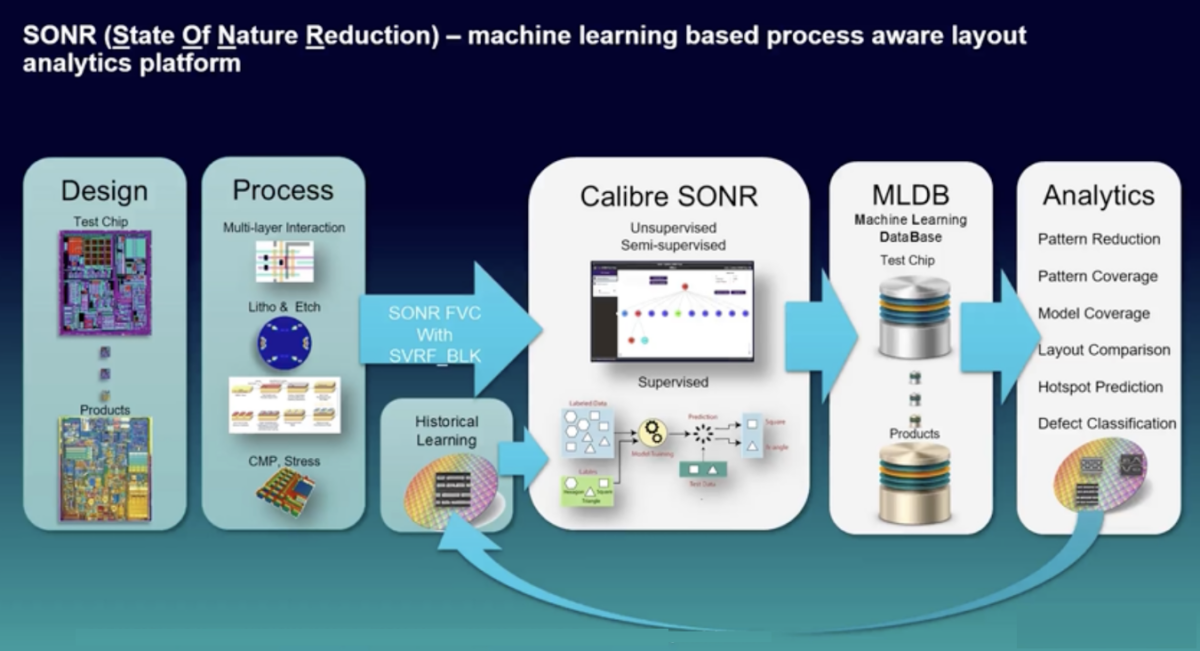

まず、エコシステムの主要部分にわたる DTCO の使用状況の現状が示されました。設計の観点から見ると、多くの先進的なファブレス企業の DFM チームは、パターンベースのアプローチの限界を認識しています。本当に必要なのは、ファウンドリに依存せずに歩留まり学習を促進する新しいテクノロジーです。

ファウンドリは総当たりパターンベースの機械学習アプローチを使用していますが、これはコストがかかりますが、完全に効果的ではありません。また、作成した膨大な製造データの効率的な情報マイニングも求めています。機器ベンダーと EDA ベンダーは緊密に連携し、より効率的な機械学習ソリューションを考案しています。

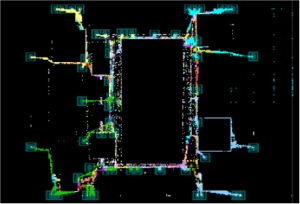

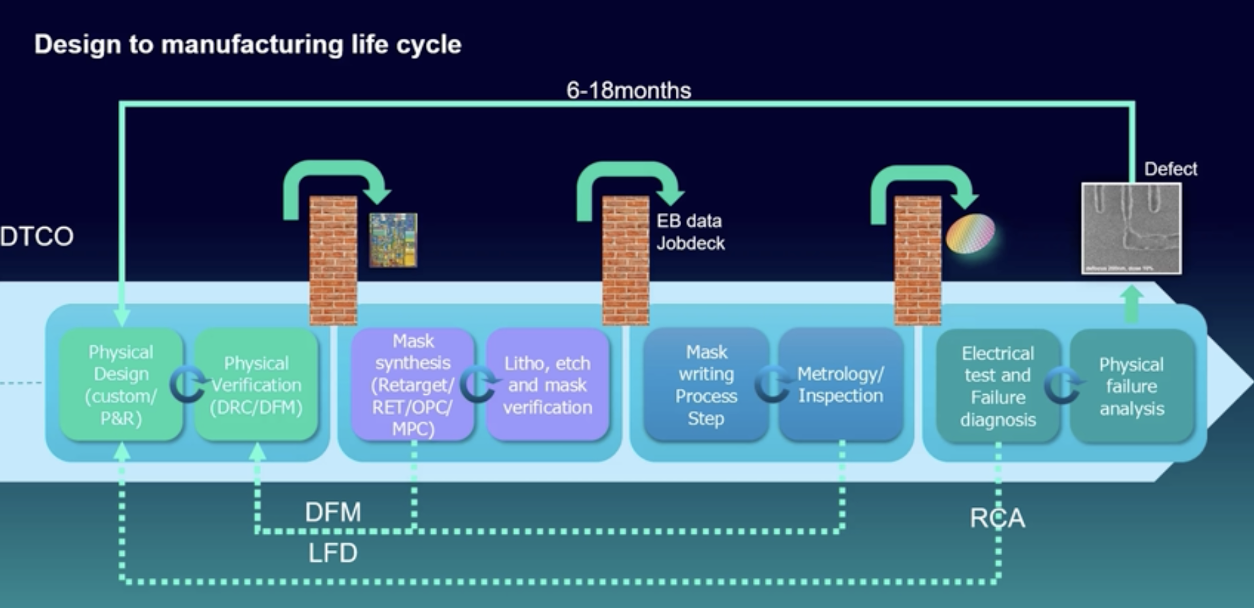

少し話を戻しますが、プロセスの設計段階と製造段階の間には壁があることが指摘されました。ファブレス企業は設計を作成し、DRC と製造向け設計 (DFM) を実行して、それをファウンドリまたは IDM 内の OPC/RET チームに渡します。設計では OPC や検証などのタスクが実行され、その後データはマスク書き込みや計測/検査のために別の壁に投げ込まれます。最後の壁は製作用です。ここでは、電気的テストと故障解析が行われます。障害の根本原因が見つかるまでに、6 ~ 18 か月が経過します。それは非常に長いフィードバック ループです。この投稿の上部にある図は、このプロセスを示しています。

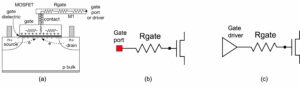

DTCO は壁を打ち破ろうとしていますが、利用可能な方法論は不完全です。従来の DTCO は、プロセス開発の非常に早い段階から開始されます。スケーリングのニーズから始まり、標準セルが定義され、合成、配置、配線が実行されて基本パターンが作成され、パフォーマンスと電力が測定されます。 SRAM イールドも実行され、そのデータは標準セル設計にループバックされます。

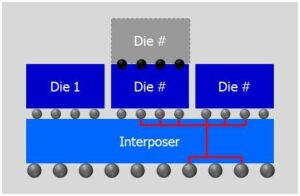

SPIE の基調講演で発表されたのは、この協調最適化の概念を設計から製造までのプロセス全体に拡張する方法でした。このアプローチには、情報チャネルを作成することで、設計から最終プロセスおよび物理解析に至るまでの情報の流れを容易にすることが含まれます。

これは簡単そうに聞こえますが、実際はそうではありません。多くの課題について、問題を軽減するための具体的なアプローチについて議論されました。たとえば、プロセスの開発中に実際の設計問題に合わせてプロセスを調整するのに役立つレイアウト合成ジェネレーターを使用して初期の設計を作成できます。これにより、初期プロセスのテープアウトで現在直面している驚きの多くを軽減できます。

大量のデータを処理することも課題です。新しい高度な圧縮技術を使用すると、30 倍の改善が可能です。これにより、データの処理と分析のタスクが大幅に改善されます。というコンセプト 説明可能なAI 問題の根本原因をより迅速に見つけるのに役立ちます。以前の結果を無効にすることなく、製造プロセスの後半で AI モデルを再トレーニングできる機能も改善の余地があります。データ分析の分野でも、「不均衡なデータ」に対処する手法があります。たとえば、100,000,000 億のパターンの中に XNUMX つのホット スポットが見つかる可能性があります。

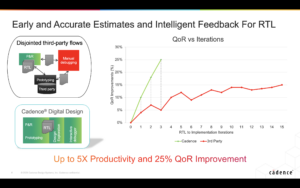

これらすべてを組み合わせると、次の図に示すように、より効率的なエンドツーエンドの設計フローを作成できます。

はこちらから

この基調講演で概説されたアプローチの影響は多大です。あなたはできる ここでプレゼンテーションを表示し、プロセスに関するホワイトペーパーにアクセスしてください。得られる有益な情報がたくさんあります。こうしてシーメンスは、設計テクノロジーの協調最適化を拡張することでイノベーションの障壁を打ち破ることを目指しています。

この投稿を共有する:

- SEO を活用したコンテンツと PR 配信。 今日増幅されます。

- PlatoData.Network 垂直生成 Ai。 自分自身に力を与えましょう。 こちらからアクセスしてください。

- プラトアイストリーム。 Web3 インテリジェンス。 知識増幅。 こちらからアクセスしてください。

- プラトンESG。 カーボン、 クリーンテック、 エネルギー、 環境、 太陽、 廃棄物管理。 こちらからアクセスしてください。

- プラトンヘルス。 バイオテクノロジーと臨床試験のインテリジェンス。 こちらからアクセスしてください。

- 情報源: https://semiwiki.com/events/339386-spie-2023-buzz-siemens-aims-to-break-down-innovation-barriers-by-extending-design-technology-co-optimization/

- :持っている

- :は

- :not

- $UP

- 000

- 100

- 2023

- a

- 能力

- アクセス

- 越えて

- 住所

- 高度な

- AI

- AIモデル

- 目指して

- すべて

- 緩和する

- また

- an

- 分析

- および

- 別の

- 申し込み

- アプローチ

- アプローチ

- です

- AREA

- AS

- At

- 試み

- 利用できます

- バック

- 障壁

- 基本

- BE

- になる

- き

- 以下

- の間に

- ビット

- ブレーク

- より広い

- 焙煎が極度に未発達や過発達のコーヒーにて、クロロゲン酸の味わいへの影響は強くなり、金属を思わせる味わいと乾いたマウスフィールを感じさせます。

- by

- 呼ばれます

- 缶

- 原因となる

- 原因

- セル

- 挑戦する

- 課題

- チャネル

- 点検

- チップ

- クローザー

- CO

- 来ます

- 到来

- コミュニケーション

- 企業

- 完全に

- 複雑な

- コンセプト

- 具体的な

- 講演

- 確認します

- 貢献者

- 高額で

- 作ります

- 作成した

- 作成

- 電流プローブ

- 現在の状態

- 現在

- データ

- データ分析

- 試合日

- 取引

- 定義済みの

- 依存性

- 設計

- デザイン

- 細部

- 発展した

- 開発

- 診断

- 議論する

- 行われ

- ダウン

- Drc

- 前

- 早い

- 容易

- エコシステム

- 効果的な

- 効率的な

- 有効にする

- 端から端まで

- 全体

- 装置

- イベント

- 例

- 交換

- 伸ばす

- 延伸

- 直面して

- 容易にする

- 不良解析

- ファン

- 速いです

- フィードバック

- フィギュア

- ファイナル

- もう完成させ、ワークスペースに掲示しましたか?

- フロー

- 発見

- ファウンドリ

- から

- 獲得

- ゲージ

- 発電機

- グラフィック

- ハンドリング

- 持ってる

- 助けます

- こちら

- ホン

- HOT

- 認定条件

- HTTPS

- 考え

- 影響

- 意義

- 改善します

- 改善

- 向上させる

- in

- include

- 含めて

- インド

- 情報

- 革新的手法

- 世界全体

- 関係する

- 関与

- 問題

- IT

- ITS

- ジョー

- キー

- 基調

- 韓国

- 後で

- 起動する

- レイアウト

- LEARN

- 学習

- 制限

- 長い

- 見て

- 見

- たくさん

- 機械

- 機械学習

- 製造業

- 多くの

- mask

- 大規模な

- 最大幅

- 五月..

- だけど

- 方法論

- 鉱業

- 軽減する

- モデル

- ヶ月

- 他には?

- もっと効率的

- ずっと

- 必要

- 必要とされる

- 新作

- of

- 頻繁に

- on

- ONE

- 光学

- 光学とフォトニクス

- 最適化

- or

- 組織

- でる

- 概説

- が

- 紙素材

- 部

- 部品

- 渡された

- パターン

- 実行する

- パフォーマンス

- 実行

- 視点

- 物理的な

- 場所

- プラットフォーム

- プラトン

- プラトンデータインテリジェンス

- プラトデータ

- 可能

- ポスト

- 電力

- プレミア

- プレゼンテーション

- PLM platform.

- printing

- 問題

- プロセス

- 伝播

- 提案された

- 非常に

- 読む

- リアル

- 本当に

- 最近

- 共和国

- 必要

- 結果

- ルート

- ルート

- ルール

- スケーリング

- スコープ

- 見ること

- を求める

- 半導体

- シリーズ

- セッション

- 示す

- ジーメンス

- 重要

- 減速

- 社会

- ソリューション

- 洗練された

- Spot

- 標準

- 起動

- 開始

- 都道府県

- 米国

- ステップ

- かなりの

- そのような

- 驚き

- 合成

- 合成

- 取る

- Talk

- タスク

- チーム

- テクニック

- テクノロジー

- test

- それ

- その後

- そこ。

- ボーマン

- 彼ら

- この

- 時間

- 役職

- 〜へ

- 今日の

- 一緒に

- 豊富なツール群

- top

- トピック

- トピック

- 投げ捨てる

- 投げた

- 伝統的な

- ユナイテッド

- 米国

- 使用法

- 有用な情報

- さまざまな

- ベンダー

- Verification

- 非常に

- 、

- ボリューム

- 壁

- ました

- 仕方..

- した

- この試験は

- 何ですか

- which

- 白

- ホワイトペーパー

- 意志

- 以内

- 無し

- ワーキング

- 書き込み

- 産出

- 収穫

- 貴社

- ゼファーネット