מאז הופעת הבכורה שלו בשנות ה-1980 עם רשתות LAN משותפים של 10Mbps על כבלים קואקסיאליים, Ethernet ראה התקדמות עקבית, כעת עם פוטנציאל לתמוך במהירויות של עד 1.6Tbps. התקדמות זו אפשרה ל-Ethernet לשרת מגוון רחב יותר של יישומים, כגון סטרימינג בשידור חי, רשתות גישה לרדיו ובקרה תעשייתית, תוך שימת דגש על החשיבות של העברת מנות אמינה ואיכות השירות. עם רוחב הפס הנוכחי של האינטרנט מזמזם ב-500 Tbps בערך, יש ביקוש הולך וגובר לטיפול משופר בתעבורה בתוך מרכז הנתונים האחורי. למרות ששרתים בודדים עדיין לא פועלים ברמות Terabit-לשנייה, התעבורה הכוללת של מרכז הנתונים מתקרבת לקנה מידה זה, מה שגרם לקבוצת 802.3dj של IEEE לבצע מאמצי סטנדרטיזציה ומצריך בקרי Ethernet ו-SerDes חזקים לניהול זרימת הנתונים המתרחבת. על רקע זה של דרישות מתגברות, התקשורת בין המעבדים כבר דוחפת למהירויות אלה.

תקשורת בין-מעבדים מובילה את הצורך בקצבי 1.6T עם חביון מינימלי. בעוד שהתקנים בודדים מוגבלים על ידי יכולות העיבוד המובנה וגודל השבב שלהם, שילוב שבבים יכול להרחיב משמעותית את היכולות הללו. הדור הראשון של יישומים צפוי לבוא בעקבות חיבורי מתג-למתג בתוך מרכז הנתונים, המאפשרים איחוד של מעבדים וזיכרון בעלי ביצועים גבוהים, להגביר את המדרגיות והיעילות בתוך מחשוב ענן.

יוזמת 802.3dj של IEEE: קידום תקני Ethernet עבור יכולת פעולה הדדית של 1.6 Tbps

עמידה במאמצי הסטנדרטיזציה המתפתחים היא חיונית עבור יכולת פעולה הדדית חלקה של המערכת האקולוגית. קבוצת ה-802.3dj של IEEE נמצאת בתהליך של גיבוש תקן ה-Ethernet הקרוב, המקיף שכבות פיזיות ופרמטרי ניהול למהירויות מ-200G עד 1.6 טרה-ביט לשנייה. מטרת הקבוצה היא קצב נתונים של 1.6 Tbps Ethernet MAC, המכוון לשיעור שגיאות סיביות מקסימלי של לא יותר מ-10-13 בשכבת ה-MAC. הוראות נוספות כוללות ממשקי יחידות חיבור של 16 ו-8 נתיבים אופציונליים (AUI) המתאימים ליישומי שבבים שונים, תוך מינוף 112G ו-224G SerDes. מבחינה פיזית, מפרט ה-1.6Tbps כולל שידור דרך 8 זוגות של כבלי twinax נחושת עד מטר אחד ו-8 זוגות סיבים למרחקים המגיעים בין 500 מטר ל-2 ק"מ. למרות שהאשרור המלא של התקן צפוי באביב 2026, מערך הליבה של תכונות צפוי להשלמת 2024.

תקורה ברוחב פס ותיקון שגיאות בתתי מערכות 1.6T Ethernet

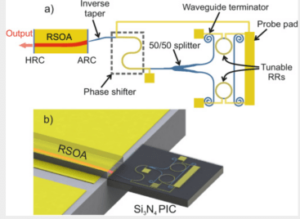

איור 1: תרשים המתאר את הרכיבים של תת-מערכת Ethernet 1.6T.

באיטרציות מוקדמות של Ethernet, ה-PCS התמקד בעיקר בקידוד נתונים לזיהוי מנות אמין. עם זאת, עם ההסלמה למהירויות Ethernet של 1.6T, הצורך בתיקון שגיאות קדימה (FEC) מתברר, במיוחד כדי לנטרל את השפלת האות אפילו על קישורים קצרים. למטרה זו, 1.6T Ethernet ממשיך להשתמש ב-Reed-Solomon FEC. גישה זו בונה מילת קוד הכוללת 514 סמלים של 10 סיביות המקודדים לבלוק של 544 סמלים, וכתוצאה מכך תקורה ברוחב פס של 6%. מילות קוד FEC אלו מופצות על פני הקישורים הפיזיים של AUI כך שכל קישור פיזי (8 עבור 1.6T Ethernet) אינו נושא מילת קוד שלמה. שיטה זו לא רק מעניקה הגנה נוספת מפני פרצי שגיאה אלא גם מאפשרת הקבלה במפענח הקצה הרחוק, ובכך מפחיתה את ההשהיה.

החיבור הבינוני הפיזי (PMA), הכולל תיבת הילוכים ו-SerDes, מביא את אות ה-Ethernet לערוצים המשודרים. עבור 1.6T Ethernet, זה כולל 8 ערוצים הפועלים כל אחד במהירות של 212Gbps, המהווים תקורה של 6% FEC. טכניקת האפונון המופעלת היא 4-Level Pulse Amplitude Modulation (PAM-4), המקודדת שני סיביות נתונים עבור כל סמל שידור, ובכך למעשה מכפילה את רוחב הפס כאשר היא ממוקמת לצד הגישה המסורתית של Non-Return Zero (NRZ). מנגנון השידור מסתמך על המרה דיגיטלית לאנלוגית, בעוד שבקצה המקבל המרה אנלוגית לדיגיטל בשילוב DSPs מבטיח חילוץ אותות מדויק.

יתר על כן, חשוב לציין שה-Ethernet PCS מציג "FEC חיצוני" המשתרע מקצה לקצה בקישור Ethernet. כדי לחזק ערוצי טווח ארוך יותר, שכבה נוספת של תיקון שגיאות עבור קווים פיזיים בודדים נמצאת בצנרת, ככל הנראה מאמצת את קוד האמינג FEC. תיקון זה צפוי למצוא את היישום העיקרי שלו במודולים של מקלטי משדר אופטיים שבהם תיקון כזה הוא הכרחי.

איור 2: תרשים המציג תקורה נוספת שנוספה בעת שימוש ב-FEC משורשר לטווח ארוך.

במערכת לדוגמה המתוארת באיור 2, ה-MAC וה-PCS מחוברים באמצעות מודול אופטי ומתיחה של סיבים. ל-PCS יש שיעור שגיאות סיביות של 10-5 בקישור המודול האופטי, בתוספת שגיאות מהקישור האופטי עצמו. שימוש ב-RS-FEC בלעדי מקצה לקצה לא יספיק כדי להשיג את ה-10-13 תקן Ethernet, מה שהופך את הקישור לבלתי אמין. אופציה תהיה הטמעה משולשת של RS FEC נפרד בכל קפיצה, מה שמגדיל את העלויות והשהייה באופן משמעותי. פתרון יעיל יותר הוא שילוב של קוד Hamming FEC משורשר במיוחד עבור הקישור האופטי, המשרת את השגיאות האקראיות האופייניות של חיבורים אופטיים. שכבת FEC פנימית זו יוצרת הרחבה נוספת של קצב הקו מ-212 Gbps ל-226 Gbps, ולכן חיוני שה-SerDes יוכל לתמוך בקצב הקו הזה.

אתגרי חביון במערכות 1.6T Ethernet

איור 3: נתיב אחזור עבור תת-מערכת Ethernet 1.6T.

רכיבים שונים תורמים להשהיית Ethernet: תור השידור, משך השידור, זמן מעבר בינוני וכמה זמני עיבוד וקבלה. כדי לדמיין זאת, שקול את איור 3, המציג תת-מערכת 1.6T Ethernet מקיפה. בעוד שהחביון יכול להיות מושפע מזמן התגובה של היישום המרוחק, גורם זה הוא חיצוני ל-Ethernet ולכן לעתים קרובות אינו נכלל במהלך ניתוח השהיה. צמצום השהיה בממשק ה-Ethernet מחייב הבנת הנסיבות הספציפיות. לדוגמה, ייתכן שהשהייה לא מהווה דאגה עיקרית לחיבורי טראנק בין מתגים עקב עיכובים מובנים בקישורי לקוח איטיים יותר. גם המרחק משחק תפקיד; אורכים גדולים יותר מציגים יותר חביון. כמובן, זה לא אומר שעלינו להתעלם מהשהייה בתרחישים אחרים, צמצום השהיה הוא תמיד מטרה.

זמן השידור קשור מטבעו לקצב ה-Ethernet ולגודל המסגרת. באופן ספציפי, עבור מערכת 1.6T Ethernet, שידור חבילה בגודל מינימלי מצריך 0.4ns - בעצם, מסגרת Ethernet אחת לכל תקתק של שעון 2.5 GHz. מצד שני, העברת מסגרת סטנדרטית בגודל מקסימלי לוקחת 8ns, ומתארכת ל-48ns עבור Jumbo Frames. המדיום הנבחר מכתיב עוד יותר את השהיה. לדוגמה, סיב אופטי חווה בדרך כלל חביון של 5ns למטר, בעוד שכבלי נחושת מהירים מעט יותר ב-4ns למטר.

חלק ניכר מהשהייה הכוללת מושרש בבקר המקלט. מפענח RS FEC מציג מטבעו חביון. כדי ליזום תיקון שגיאות, על המערכת לקבל 4 מילות קוד, אשר, ב-1.6Tbps, מסתכמות ב-12.8ns. פעילויות עוקבות, כולל תיקון שגיאות ואגירה, מעצימות את זמן האחזור הזה. בעוד שמשך האחסון של מילת הקוד של FEC נשאר עקבי, זמן ההשהיה במהלך קליטת ההודעות מותנה ביישום הספציפי. עם זאת, ניתן לייעל את ההשהיה על ידי שימוש באסטרטגיות עיצוב דיגיטליות מדוקדקות.

בעיקרו של דבר, קיים השהייה אינהרנטית ובלתי נמנעת עקב מנגנון FEC והמרחק הפיזי או אורך הכבל. מעבר לגורמים אלה, מומחיות התכנון ממלאת תפקיד מרכזי כדי למזער את זמן האחזור של בקר Ethernet. מינוף פתרון שלם המשלב ומבצע אופטימיזציה של ה-MAC, PCS ו-PHY, סולל את הדרך למימוש היעיל ביותר עם חביון נמוך.

<br> סיכום

איור 4: הצלחת סיליקון במעבר ראשון עבור Synopsys 224G Ethernet PHY IP בתהליך 3nm המציג עיני PAM-4 ליניאריות במיוחד.

1.6 Tbps Ethernet מותאם עבור היישומים הדורשים ביותר ברוחב הפס והשהייה הרגישים ביותר. עם הופעתה של טכנולוגיית 224G SerDes, בשילוב עם ההתקדמות ב-MAC ו-PCS IP, נגישים כעת פתרונות מקיפים העומדים ברציפות בתקני 1.6T Ethernet המתפתחים. בנוסף, בשל ההשהיה הטבועה בפרוטוקול ושיטות תיקון השגיאות, העיצוב הדיגיטלי והאנלוגי של IP חייב להיות נבנה בקפידה על ידי מעצבים מומחים כדי להימנע מהכנסת השהייה מיותרת לנתיב הנתונים.

השגת ביצועים מובילים עבור עיצובי 1.6T SoC דורשת ארכיטקטורה אופטימלית ביעילות ושיטות תכנון קפדניות עבור כל רכיב שבב. זה מדגיש את שימור החשמל וממזער את טביעת הרגל של הסיליקון, מה שהופך את קצבי הנתונים של 1.6T למציאות. Synopsys 224G Ethernet PHY IP מוכח סיליקון קבעה את הבמה לבקר 1.6T MAC ו-PCS. באמצעות עיצוב, ניתוח, סימולציה וטכניקות מדידה מובילות, Synopsys ממשיכה לספק שלמות אות יוצאי דופן וביצועי ריצוד, עם פתרון Ethernet מלא כולל MAC+PCS+PHY.

- הפצת תוכן ויחסי ציבור מופעל על ידי SEO. קבל הגברה היום.

- PlatoData.Network Vertical Generative Ai. העצים את עצמך. גישה כאן.

- PlatoAiStream. Web3 Intelligence. הידע מוגבר. גישה כאן.

- PlatoESG. פחמן, קלינטק, אנרגיה, סביבה, שמש, ניהול פסולת. גישה כאן.

- PlatoHealth. מודיעין ביוטכנולוגיה וניסויים קליניים. גישה כאן.

- מקור: https://semiengineering.com/latency-considerations-for-1-6t-ethernet-designs/

- :יש ל

- :הוא

- :לֹא

- :איפה

- $ למעלה

- 1

- 12

- 16

- 2024

- 2026

- 212

- 220

- 362

- 500

- 8

- a

- גישה

- נגיש

- חשבונאות

- מדויק

- להשיג

- לרוחב

- פעילויות

- הוסיף

- נוסף

- בנוסף

- אימוץ

- התקדמות

- מתקדם

- נגד

- מכוון

- מותר

- כְּבָר

- גם

- למרות

- תמיד

- בתוך

- כמויות

- להגביר

- an

- אנליזה

- ו

- צפוי

- בקשה

- יישומים

- גישה

- ארכיטקטורה

- ARE

- AS

- At

- לְהִמָנַע

- עורפי

- רקע

- רוחב פס

- BE

- הופך להיות

- בֵּין

- מעבר

- קצת

- לחסום

- לחזק

- חיזוק

- מביא

- בונה

- אבל

- by

- כֶּבֶל

- כבלים

- CAN

- קיבולת

- לשאת

- האתגרים

- ערוצים

- שבב

- שבבי

- נבחר

- בנסיבות

- לקוחות

- שעון

- ענן

- ענן מחשוב

- קוד

- משולב

- שילוב

- תקשורת

- להשלים

- השלמה

- רְכִיב

- רכיבים

- מַקִיף

- מכיל

- מחשוב

- דְאָגָה

- יחד

- מחובר

- חיבורי

- שימור

- לשקול

- שיקולים

- עִקבִי

- ממשיך

- ברציפות

- לתרום

- לִשְׁלוֹט

- בקר

- המרה

- נְחוֹשֶׁת

- ליבה

- עלויות

- לְנַטְרֵל

- קורס

- מעוצב

- יוצר

- נוֹכְחִי

- נתונים

- Datacenter

- הופעה ראשונה

- עיכובים

- למסור

- דרישה

- תובעני

- דרישות

- מתאר

- עיצוב

- מעצבים

- עיצובים

- איתור

- התקנים

- מכתיב

- אחר

- דיגיטלי

- בחריצות

- מציג

- מרחק

- מופץ

- לא

- כפילה

- ראוי

- משך

- בְּמַהֲלָך

- כל אחד

- מוקדם יותר

- המערכת האקולוגית

- אפקטיבי

- יעילות

- יְעִילוּת

- יעיל

- יעילות

- מַאֲמָצִים

- הִתהַוּוּת

- מדגיש

- הדגשת

- מוּעֳסָק

- העסקת

- מאפשר

- מה שמאפשר

- מקיף

- סוף

- מקצה לקצה

- מבטיח

- שלם

- שגיאה

- שגיאות

- הסלמה

- מַהוּת

- חיוני

- למעשה

- Ether (ETH)

- אֲפִילוּ

- כל

- ברור

- מתפתח

- דוגמה

- יוצא דופן

- נשלל

- הרחבת

- הרחבה

- צפוי

- מומחה

- מומחיות

- להאריך

- מאריך

- חיצוני

- הוֹצָאָה

- עיניים

- גורם

- גורמים

- רחוק

- מהר יותר

- תכונות

- משתתפים

- תרשים

- ראשון

- דור ראשון

- תזרים

- מרוכז

- בעקבות

- עָקֵב

- בעד

- ניסוח

- קדימה

- מסגרת

- החל מ-

- נוסף

- דור

- נותן

- יותר

- קְבוּצָה

- קבוצה

- גדל

- יד

- טיפול

- גָבוֹהַ

- ביצועים גבוהים

- מאוד

- אולם

- HTML

- HTTPS

- הֶכְרֵחִי

- הפעלה

- חשיבות

- חשוב

- משופר

- in

- באחר

- לכלול

- כולל

- גדל

- בנפרד

- התעשייה

- מוּשׁפָע

- הטמון

- מטבע הדברים

- ליזום

- יוזמה

- למשל

- משלב

- השתלבות

- שלמות

- מִמְשָׁק

- ממשקים

- אינטרנט

- יכולת פעולה הדדית

- אל תוך

- מהותי

- מבוא

- מציג

- החדרה

- כרוך

- IP

- IT

- איטרציות

- שֶׁלָה

- עצמו

- jpg

- נתיב

- חֶבִיוֹן

- שכבה

- שכבות

- אורך

- רמות

- מינוף

- סביר

- קו

- קווים

- קשר

- קישורים

- לחיות

- עוד

- נמוך

- מק

- עשייה

- לנהל

- ניהול

- max-width

- מקסימום

- מאי..

- אומר

- מדידה

- מנגנון

- בינוני

- זכרון

- הודעה

- שיטה

- שיטות

- קַפְּדָנִי

- מינימלי

- לצמצם

- ממזער

- מזעור

- מודול

- מודולים

- יותר

- רוב

- צריך

- מתקרב

- צורך

- רשתות

- אף על פי כן

- לא

- הערות

- עַכשָׁיו

- מטרה

- of

- לעתים קרובות

- on

- ONE

- רק

- פועל

- אופטימיזציה

- מייעל

- אפשרות

- or

- אחר

- יותר

- מקיף

- זוגות

- פרמטרים

- במיוחד

- נתיב

- מחשבים

- עבור

- ביצועים

- הופעות

- גופני

- פיזית

- צינור

- מכריע

- אפלטון

- מודיעין אפלטון

- אפלטון נתונים

- משחק

- ועוד

- פוטנציאל

- כּוֹחַ

- פרקטיקות

- בראש ובראשונה

- יְסוֹדִי

- תהליך

- תהליך

- מעבדים

- התקדמות

- מוקרן

- .

- פרוטוקול

- דופק

- מטרה

- דוחף

- איכות

- רדיו

- אקראי

- רכס

- ציון

- תעריפים

- לְהַגִיעַ

- הגעה

- תגובה

- מציאות

- לקבל

- קבלה

- קבלה

- הפחתה

- אָמִין

- שְׂרִידִים

- טיוח

- דורש

- מוגבל

- וכתוצאה מכך

- חָסוֹן

- תפקיד

- מוּשׁרָשׁ

- ריצה

- בקרת מערכות ותקשורת

- סולם

- תרחישים

- בצורה חלקה

- שְׁנִיָה

- לראות

- קטע

- רגיש

- נפרד

- לשרת

- שרות

- סט

- כמה

- משותף

- קצר

- צריך

- לראווה

- לאותת

- באופן משמעותי

- סיליקון

- הדמיה

- מידה

- So

- פִּתָרוֹן

- פתרונות

- משתרע

- חוד החנית

- ספציפי

- במיוחד

- מפרט

- מהירויות

- אביב

- התמחות

- תֶקֶן

- תקינה

- תקנים

- אחסון

- אסטרטגיות

- נהירה

- לאחר מכן

- ניכר

- הצלחה

- כזה

- מַתְאִים

- תמיכה

- סמל

- מערכת

- מותאם

- לוקח

- טכניקה

- טכניקות

- טכנולוגיה

- מֵאֲשֶׁר

- זֶה

- השמיים

- שֶׁלָהֶם

- שם.

- בכך

- לכן

- אלה

- זֶה

- דרך

- כָּך

- Tick

- קָשׁוּר

- זמן

- פִּי

- ל

- חלק עליון

- מסורתי

- תְנוּעָה

- להעביר

- לְהַעֲבִיר

- לְשַׁלֵשׁ

- שתיים

- טיפוסי

- בדרך כלל

- בלתי נמנע

- הבנה

- להתחייב

- יחידה

- בקרוב ב

- על

- באמצעות

- לנצל

- באמצעות

- לחזות

- דֶרֶך..

- we

- מתי

- אשר

- בזמן

- רחב יותר

- עם

- בתוך

- היה

- עוד

- זפירנט

- אפס