אתגרי בדיקת SoC מתעוררים עקב המורכבות והמגוון של הבלוקים הפונקציונליים המשולבים בשבב. ככל שה-SoC הופכים מורכבים יותר, קשה יותר ויותר לגשת לכל הבלוקים הפונקציונליים בתוך השבב לצורך בדיקה. SoCs יכולים גם להכיל מיליארדי טרנזיסטורים, מה שהופך את זה ללוקח מאוד זמן לבדוק שבבים. מכיוון שזמן הבדיקה משפיע ישירות על עלות הבדיקה, צמצום זמן הבדיקה הוא קריטי לניהול העלות של מוצר מוגמר. מחולל דפוסי בדיקה אוטומטי (ATPG) הוא חלק מכריע בבדיקות SoC, מכיוון שהוא מייצר דפוסי בדיקה כדי לזהות תקלות בתכנון. עם זאת, האוטומציה של ATPG היא משימה מאתגרת, במיוחד עבור SoCs מורכבים, בשל המספר הגדול של בלוקים פונקציונליים ונקודות בדיקה שצריך לכסות. פיתוח אלגוריתמי ATPG יעילים ואפקטיביים הוא אתגר מרכזי עבור בדיקות SoC. אבל רבים מכלי ה-ATPG כיום אינם אוטומטיים לחלוטין. על המשתמשים ללמוד את כל הפקודות והאפשרויות שמציעות הכלים כדי להשתמש בהן ביעילות.

האם יש פתרון שמביא קצת אוטומציה לתהליך ATPG, ובכך משפר את הפרודוקטיביות ההנדסית? מה אם הפתרון הזה מספק גם חיסכון משמעותי בזמן הבדיקה? פתרון Tessent Streaming Scan Network (SSN) של סימנס EDA מבטיח לספק את היתרונות הללו. זה הוכח על ידי אינטל, אחת מלקוחות סימנס EDA במהלך ועידת User2User האחרונה. Toai Vo של אינטל הציג נקודות הוכחה המבוססות על הניסיון של הצוות שלו עם העיצוב הראשון שלהם באמצעות פתרון Tessent SSN. הצוות שלו כלל את קווין לי, ג'ו צ'ו וצ'יינקואו (טום) וו.

פתרון SSN של Tessent

בגישת בדיקות סריקה סטנדרטית, נתוני בדיקה נטענים למעגל ביט אחד בכל פעם ומועברים דרך שרשראות הסריקה כדי לצפות בתגובות הפלט. תהליך זה חוזר על עצמו עבור כל דפוס בדיקה, מה שעלול לקחת זמן ויכול להוביל לזמני בדיקה ארוכים. אבל פתרון Tessent SSN מארז נתוני בדיקה כדי להפחית באופן דרמטי את מאמצי היישום של DFT ולהפחית את זמני בדיקות הייצור. על ידי ניתוק דרישות DFT ברמת הליבה וברמת השבב, ניתן לעצב כל ליבה עם תצורת הדחיסה האופטימלית ביותר עבור אותה ליבה. ניתן להשתמש בפתרון זה כדי לבדוק ביעילות שבבים גדולים ומורכבים שיש להם מספר גבוה של צמתים פנימיים שצריך לבדוק. היא משתמשת ברשת ייעודית כדי להעביר נתוני בדיקה בצורה סטרימינג, המאפשרת עיבוד מקביל של הנתונים ובכך מקצרת את זמן הבדיקה.

בקרת מערכות ותקשורת

רשת הסטרימינג סריקה תומכת בארכיטקטורות סריקה ניתנות להרחבה שיכולות להתמודד עם SoCs עם מספר רב של בלוקים פונקציונליים. הכלי מספק גישה ניתנת להרחבה של בדיקת כל מספר של ליבות במקביל תוך צמצום זמן הבדיקה ונפח הנתונים בסריקה. תשתית בדיקות SSN של Tessent בנויה סביב תקן IEEE 1687/IJTAG כדי לספק גמישות ומדרגיות רבה יותר לטיפול בתכנונים ותרחישי בדיקה מורכבים יותר.

אוטומציה

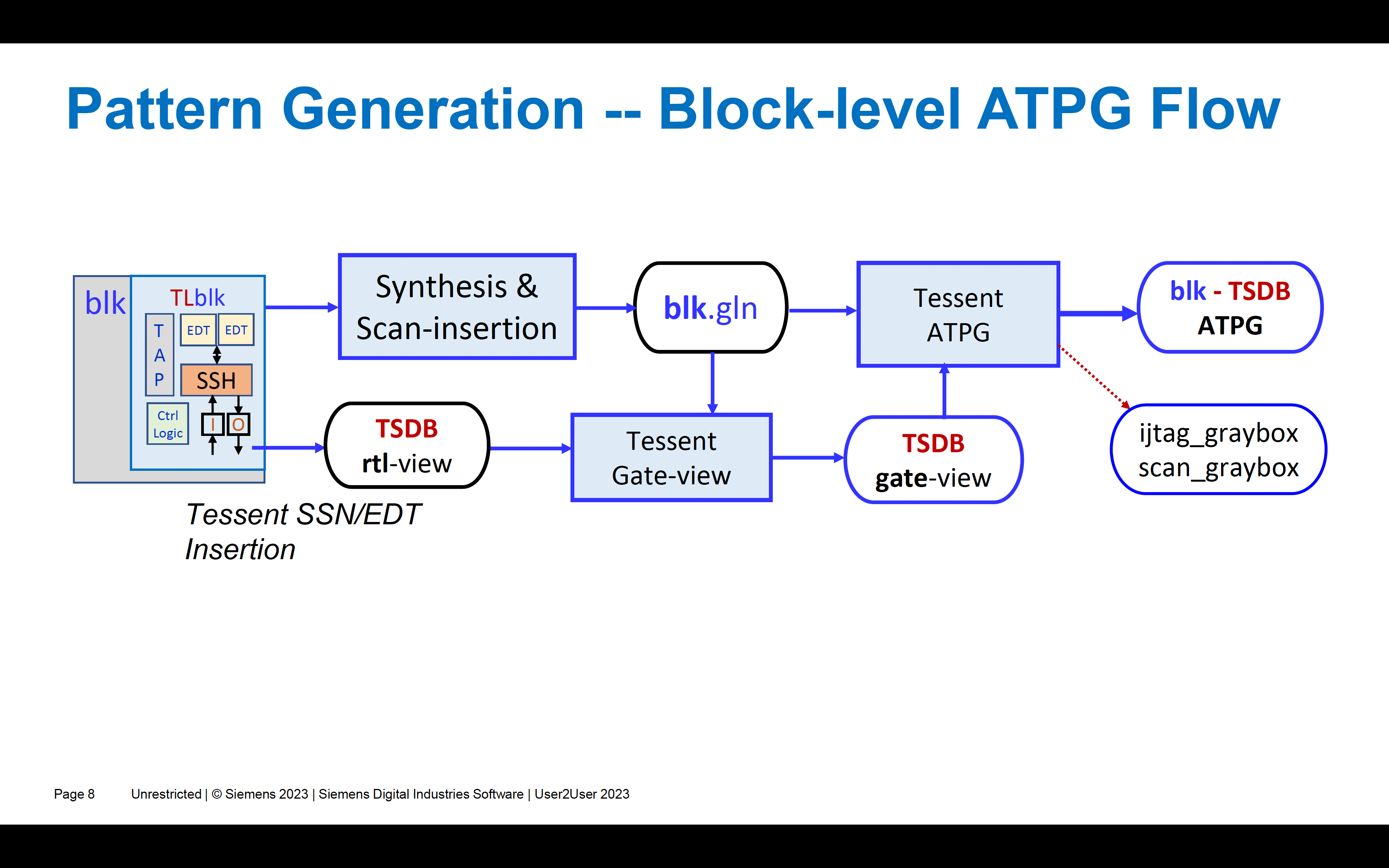

האופי ההיררכי מונחה עצמים של תשתית הבדיקה מאפשר אוטומציה קלה יותר. באמצעות תשתית Tessent, משתמש יכול להכניס בקלות לוגיקה בדיקה לשבב. התהליך מתחיל בתכנון RTL, שבו לוגיקה של בדיקת SSN מוכנסת באמצעות אוטומציה.

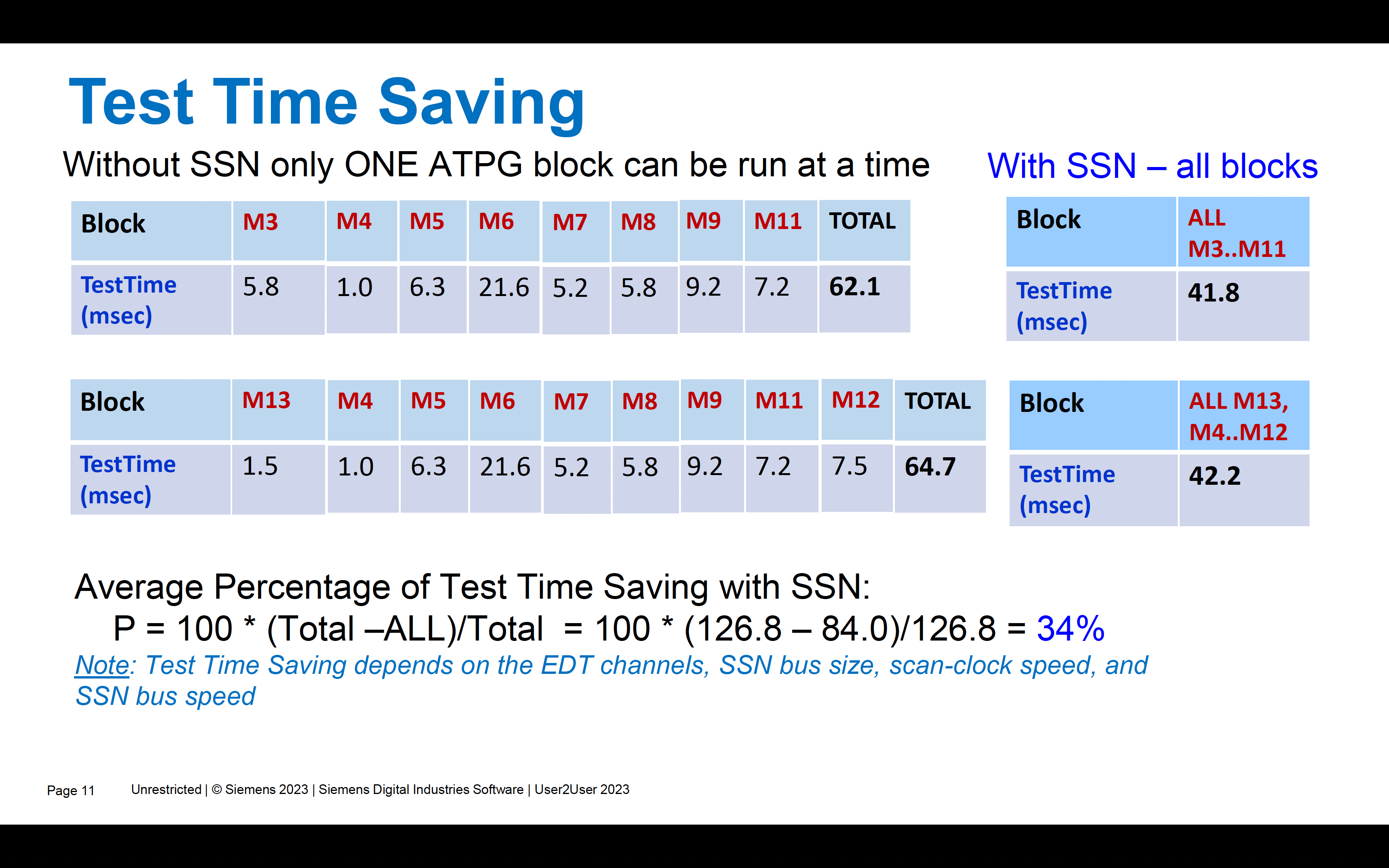

חיסכון בזמן בדיקה

באמצעות גישת ATPG מסורתית, בדרך כלל ניתן להפעיל רק בלוק בכל זמן שמאריך את זמן הבדיקה הכולל. עם גישת Tessent SSN ATPG, ניתן להפעיל מספר בלוקים במקביל, ובכך להפחית מאוד את זמן הבדיקה הכולל. הטבלה הבאה מציגה את החיסכון בזמן הבדיקה שהושג על ידי הצוות של Toai בעיצוב שלהם.

<br> סיכום

הצוות של Toai מצא שקל מאוד לעבור מערוץ ATPG מבוסס בדיקה דטרמיניסטית (EDT) מסורתית ל-ATPG מבוסס מנות עם SSN. פתרון SSN של Tessent הפחית במידה ניכרת את המאמץ ההנדסי והסיליקון לקח זמן. והפחתת זמן הבדיקה הייתה משמעותית בהשוואה לפתרון מסורתי לבדיקה. במילים של Toai Vo, זה בהחלט פתרון בדיקה חדשני וזה באמת עובד.

לפרטים נוספים, בקר בדף המוצר של Tessent SSN.

גם לקרוא:

השגת PPA אופטימלי בהשמה וביצועו עד לסיום

הפחתת ההשפעות של הפצת שגיאות DFE על קישורי SerDes במהירות גבוהה

שתף את הפוסט הזה באמצעות:

- הפצת תוכן ויחסי ציבור מופעל על ידי SEO. קבל הגברה היום.

- PlatoAiStream. Web3 Data Intelligence. הידע מוגבר. גישה כאן.

- הטבעת העתיד עם אדריאן אשלי. גישה כאן.

- קנה ומכירה של מניות בחברות PRE-IPO עם PREIPO®. גישה כאן.

- מקור: https://semiwiki.com/eda/328395-tessent-ssn-enables-significant-test-time-savings-for-soc-atpg/

- :הוא

- :לֹא

- :איפה

- $ למעלה

- a

- בהחלט

- גישה

- הושג

- אלגוריתמים

- תעשיות

- גם

- an

- ו

- כל

- גישה

- ARE

- סביב

- AS

- At

- אוטומטי

- מכני עם סלילה אוטומטית

- אוטומציה

- רכב

- מבוסס

- BE

- להיות

- הופך להיות

- הטבות

- מיליארדים

- קצת

- לחסום

- אבני

- להביא

- מביא

- נבנה

- אבל

- by

- CAN

- נושאת

- שרשראות

- לאתגר

- האתגרים

- אתגר

- ערוץ

- שבב

- שבבי

- לעומת

- מורכב

- מורכבות

- כנס

- תְצוּרָה

- ליבה

- עלות

- מכוסה

- קריטי

- מכריע

- לקוחות

- נתונים

- מוקדש

- למסור

- אספקה

- מספק

- עיצוב

- מעוצב

- עיצובים

- פרטים

- מתפתח

- קשה

- ישירות

- גיוון

- באופן דרמטי

- ראוי

- בְּמַהֲלָך

- כל אחד

- קל יותר

- בקלות

- קל

- אפקטיבי

- יעילות

- תופעות

- יעיל

- יעילות

- מאמץ

- מוטבע

- מאפשר

- מה שמאפשר

- הנדסה

- שיפור

- שגיאה

- במיוחד

- ניסיון

- מאוד

- תקלות

- ראשון

- גמישות

- תזרים

- הבא

- בעד

- מצא

- החל מ-

- לגמרי

- פונקציונלי

- מייצר

- דור

- גנרטור

- יותר

- מאוד

- לטפל

- יש

- גָבוֹהַ

- שֶׁלוֹ

- אולם

- HTTPS

- IEEE

- if

- השפעות

- הפעלה

- in

- כלול

- יותר ויותר

- תשתית

- חדשני

- משולב

- אינטל

- פנימי

- אל תוך

- IT

- עצמו

- מפתח

- גָדוֹל

- עוֹפֶרֶת

- לִלמוֹד

- רמה

- הגיון

- ארוך

- עשייה

- ניהול

- דרך

- ייצור

- רב

- max-width

- נודד

- מזעור

- יותר

- רוב

- מספר

- טבע

- צורך

- רשת

- צמתים

- בדרך כלל

- מספר

- אובייקט

- להתבונן

- of

- מוצע

- on

- ONE

- רק

- אופטימלי

- אפשרויות

- להזמין

- תפוקה

- עמוד

- מקביל

- חלק

- תבנית

- דפוסי

- אפלטון

- מודיעין אפלטון

- אפלטון נתונים

- נקודות

- הודעה

- מוצג

- תהליך

- תהליך

- המוצר

- פִּריוֹן

- מבטיח

- הוכחה

- מספק

- חומר עיוני

- בֶּאֱמֶת

- לאחרונה

- להפחית

- מופחת

- הפחתה

- הפחתה

- חזר

- דרישות

- תגובות

- שורש

- הפעלה

- חיסכון

- בקרת מערכות ותקשורת

- להרחבה

- סריקה

- תרחישים

- זז

- הופעות

- סימנס

- משמעותי

- סיליקון

- פִּתָרוֹן

- כמה

- תֶקֶן

- נהירה

- תומך

- שולחן

- המשימות

- נבחרת

- מבחן

- בדיקות

- זֶה

- השמיים

- שֶׁלָהֶם

- אותם

- שם.

- בכך

- אלה

- זֶה

- דרך

- זמן

- דורש זמן רב

- פִּי

- ל

- היום

- כלי

- כלים

- סה"כ

- מסורתי

- לְהַעֲבִיר

- סומך

- להשתמש

- מְשׁוּמָשׁ

- משתמש

- משתמשים

- באמצעות

- מאוד

- באמצעות

- כֶּרֶך

- היה

- מה

- אשר

- בזמן

- עם

- בתוך

- לַחֲזוֹר עַל

- מילים

- עובד

- זפירנט