קודם לכן כתבתי על אימות תפקודי IC ו-ASIC, אז היום הגיע הזמן לסיים את זה עם מצב האימות הפונקציונלי של FPGA. קבוצת המחקר של וילסון עורכת דוח FPGA כל שנתיים מאז 2018, כך שזו הפעם השלישית שהם מתמקדים בפלח העיצוב הזה. במחיר של 5.8 מיליארד דולר, שוק ה-FPGA גדול, וצפוי לגדול ל-8.1 מיליארד דולר עד 2025. רכיבי FPGA התחילו את דרכו ב-1984 עם קיבולת שערים מוגבלת, וכעת גדלו וכוללים מיליוני שערים, מעבדים ופרוטוקולי נתונים סטנדרטיים.

יישומים בנפח נמוך נהנים מה-NRE של התקני FPGA, ומהנדסים יכולים במהירות אבטיפוס של העיצובים שלהם על ידי אימות ואימות במהירות. FPGAs כוללים כעת מעבדים, כמו: Xilinx Zynq UltraSCALE, אינטל סטרטיקס, Microchip SmartFusion. מבין 980 המשתתפים במחקר האימות הפונקציונלי, סגנונות העיצוב של FPGA וה-SoC FPGA הניתנים לתכנות הם הפופולריים ביותר.

מכיוון שגודלם של FPGAs גדל לאחרונה, הסיכוי לשחרור ייצור ללא באגים ירד ל-17% בלבד, וזה אפילו יותר גרוע מ-30% מפרויקטי IC ו-ASIC עבור סיליקון ראשון נכון. ברור שאנו זקוקים לאימות פונקציונלית טובה יותר עבור מערכות FPGA מורכבות.

סוגי הבאגים שנמצאו בייצור מתחלקים למספר קטגוריות:

- 53% - הגיוני או פונקציונלי

- 31% - קושחה

- 29% - שעון

- 28% - תזמון, נתיב איטי מדי

- 21% - תזמון, נתיב מהיר מדי

- 18% - ממשק אות מעורב

- 9% - תכונת בטיחות

- 8% - תכונת אבטחה

בהתקרבות לקטגוריה הגדולה ביותר של כשל, הגיוני או פונקציונלי, ישנן חמש סיבות שורש.

פרויקטים של FGPA לרוב לא הסתיימו בזמן, שוב בגלל הגודל הגדול יותר של המערכות, מורכבות ההיגיון ואפילו שיטות האימות בהן נעשה שימוש.

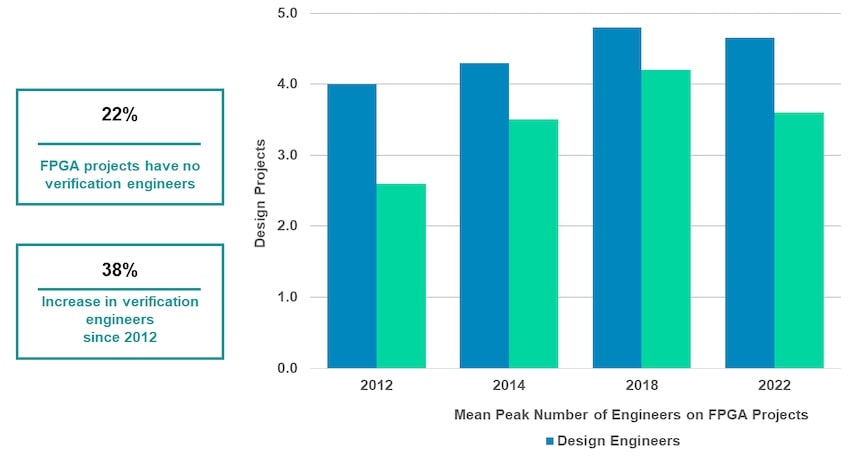

למהנדסים בצוות FPGA יכולים להיות כותרות ברורות כמו מהנדס תכנון או מהנדס אימות, אך ב-22% מהפרויקטים לא היו מהנדסי אימות - כלומר שמהנדסי התכנון עשו חובה כפולה ואימתו את ה-IP שלהם. במהלך 10 השנים האחרונות חלה עלייה של 38% במספר מהנדסי האימות בפרויקט FPGA, כך שזו התקדמות לקראת ייצור נטול באגים.

מהנדסי אימות בפרויקטי FPGA השקיעו את רוב זמנם במשימות ניפוי באגים ב-47%:

- 47% - ניפוי באגים

- 19% - יצירת הדמיית בדיקה והרצה

- 17% - פיתוח Testbench

- 11% - תכנון מבחן

- 6% - אחר

מספר המעבדים המשובצים גדל בהתמדה לאורך זמן, כך של-65% מתכנוני FPGA יש כיום ליבת מעבד אחת או יותר, מה שמגדיל את כמות האימות בין ממשקי חומרה ותוכנה; וניהול רשתות על שבב.

מעבד ה-RISC-V הפופולרי מתמיד מוטבע ב-22% מה-FPGA, ומאיצי בינה מלאכותית משמשים ב-23% מהפרויקטים. ישנם מספר ממוצע של 3-4 תחומי שעון בשימוש ב-FPGAs, והם דורשים סימולציות תזמון ברמת השער לאימות, בתוספת שימוש בכלים סטטיים של Clock Domain Crossing (CDC) לאימות.

תכונות אבטחה מתווספות ל-49% מתכנוני FPGA כדי להחזיק נתונים רגישים, בנוסף 42% מפרויקטי FPGA עומדים בתקנים או הנחיות קריטיות לבטיחות. ב-SemiWiki כתבנו לא פעם על בלוגים ISO 26262 ו DO-254 תקנים. מאמצי התכנון של בטיחות תפקודית (FuSa) לוקחים בין 25% ל-50% מזמן הפרויקט הכולל.

שלוש שפות האימות המובילות הן VHDL, SystemVerilog ו-Verilog; אבל שימו לב גם לקפיצות האחרונות בשפות Python ו-C/C++.

מתודולוגיות ה-FPGA הפופולריות ביותר וספריות הבסיס של ספסל הבדיקה הן: Accellera UVM ,OSVVM ו-UVVM. מבוסס פייתון cocotb אפילו נוספה כקטגוריה חדשה לשנת 2022.

שפות הטענה מובלות על ידי SystemVerilog Assertions (SVA) ב-45%, ואחריה Accellera Open Verification Library (OVL) ב-13% ו-PSL ב-11%. עיצובי FPGA עשויים לשלב VHDL עבור עיצוב RTL יחד עם SVA להצהרות.

בדיקת נכסים פורמלית הולכת וגדלה בקרב פרויקטי FPGA, במיוחד כאשר אפליקציות פורמליות אוטומטיות יותר הוצגו על ידי ספקי EDA.

גישות אימות מבוססות סימולציה במהלך 10 השנים האחרונות מראות אימוץ יציב, המפורטות לפי סדר הרלוונטיות: כיסוי קוד, כיסוי פונקציונלי, הצהרות, מוגבל אקראי.

<br> סיכום

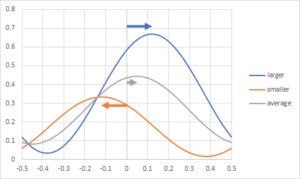

המספר הנמוך של 17% ללא באגים עבור פרויקטים של FPGA בשנת 2022 שהביא אותו לייצור היה המספר המפתיע ביותר עבורי, שכן המאמץ להיזכר או לתכנת מחדש מכשיר בשטח הוא יקר וגוזל זמן לתקן. גישת אימות פונקציונלי חזקה יותר אמורה להוביל לפחות בריחת באגים לייצור, וחלוקת משתתפי המחקר לשתי קבוצות אכן מראה את היתרון.

קרא את השלם נייר לבן בן 18 עמודים כאן.

בלוגים קשורים

שתף את הפוסט הזה באמצעות:

- הפצת תוכן ויחסי ציבור מופעל על ידי SEO. קבל הגברה היום.

- Platoblockchain. Web3 Metaverse Intelligence. ידע מוגבר. גישה כאן.

- מקור: https://semiwiki.com/eda/324651-the-state-of-fpga-functional-verification/

- 1

- 10

- 2018

- 2022

- a

- אודות

- מאיצים

- הוסיף

- לדבוק

- אימוץ

- AI

- בין היתר

- כמות

- ו

- יישומים

- גישה

- גישות

- אפליקציות

- ASIC

- מכני עם סלילה אוטומטית

- מְמוּצָע

- להיות

- תועלת

- מוטב

- בֵּין

- B

- חרק

- באגים

- קיבולת

- קטגוריות

- קטגוריה

- לגרום

- גרם

- גורמים

- ה-CDC

- סיכוי

- בדיקה

- בבירור

- שעון

- קוד

- לשלב

- להשלים

- מורכב

- מורכבות

- כיסוי

- יוצרים

- קריטי

- נתונים

- עיצוב

- עיצובים

- מכשיר

- התקנים

- DID

- מובהק

- תחום

- תחומים

- ירד

- מאמץ

- מַאֲמָצִים

- מוטבע

- מהנדס

- מהנדסים

- במיוחד

- אֲפִילוּ

- כל

- יקר

- כשלון

- ליפול

- תכונות

- שדה

- ראשון

- מרוכז

- בעקבות

- רִשְׁמִי

- מצא

- FPGA

- החל מ-

- פונקציונלי

- גייטס

- קְבוּצָה

- קבוצה

- לגדול

- גדל

- מְגוּדָל

- הנחיות

- חומרה

- להחזיק

- HTML

- HTTPS

- in

- לכלול

- להגדיל

- גדל

- גדל

- אינטל

- ממשקים

- הציג

- IP

- IT

- קפיצות

- שפות

- גדול יותר

- הגדול ביותר

- עוֹפֶרֶת

- הוביל

- ספריות

- סִפְרִיָה

- מוגבל

- ברשימה

- נמוך

- עשוי

- ניהול

- שוק

- max-width

- משמעות

- מתודולוגיות

- שיטות

- מיליונים

- יותר

- רוב

- הכי פופולארי

- צורך

- רשתות

- חדש

- מספר

- ONE

- לפתוח

- להזמין

- מקיף

- שֶׁלוֹ

- מאמר

- המשתתפים

- עבר

- נתיב

- אפלטון

- מודיעין אפלטון

- אפלטון נתונים

- ועוד

- פופולרי

- הודעה

- מעבד

- מעבדים

- הפקה

- התקדמות

- פּרוֹיֶקט

- פרויקטים

- רכוש

- פרוטוקולים

- אב טיפוס

- פיתון

- מהירות

- אקראי

- לאחרונה

- לאחרונה

- לשחרר

- הרלוונטיות

- לדווח

- לדרוש

- מחקר

- קבוצת מחקר

- חָסוֹן

- שורש

- עגול

- ריצה

- בְּטִיחוּת

- אבטחה

- קטע

- רגיש

- כמה

- צריך

- לְהַצִיג

- הופעות

- סימנס

- סיליקון

- since

- במידה ניכרת

- מידה

- So

- תוכנה

- מְהִירוּת

- בילה

- תקנים

- החל

- מדינה

- יציב

- לימוד

- מפתיע

- מערכות

- לקחת

- משימות

- נבחרת

- טכניקות

- מבחן

- השמיים

- המדינה

- שֶׁלָהֶם

- שְׁלִישִׁי

- שְׁלוֹשָׁה

- זמן

- תזמון

- כותרות

- ל

- היום

- גַם

- כלים

- חלק עליון

- לקראת

- סוגים

- להשתמש

- ספקים

- אימות

- מְאוּמָת

- אימות

- באמצעות

- כֶּרֶך

- אשר

- לבן

- נייר לבן

- וילסון

- שנים

- זפירנט