שתי טכנולוגיות אלגוריתמיות מבוססות תוכנה עדכניות - נהיגה אוטונומית (ADAS/AD) ובינה מלאכותית (GenAI) - שומרות על קהילת הנדסת המוליכים למחצה ערה בלילה.

בעוד ADAS ברמה 2 ורמה 3 נמצאת במסלול, AD ברמות 4 ו-5 רחוקות מהמציאות, מה שגורם לירידה בהתלהבות ההון סיכון ובכסף. כיום, GenAI זוכה לתשומת הלב, וחברות הון סיכון משקיעים בשקיקה מיליארדי דולרים.

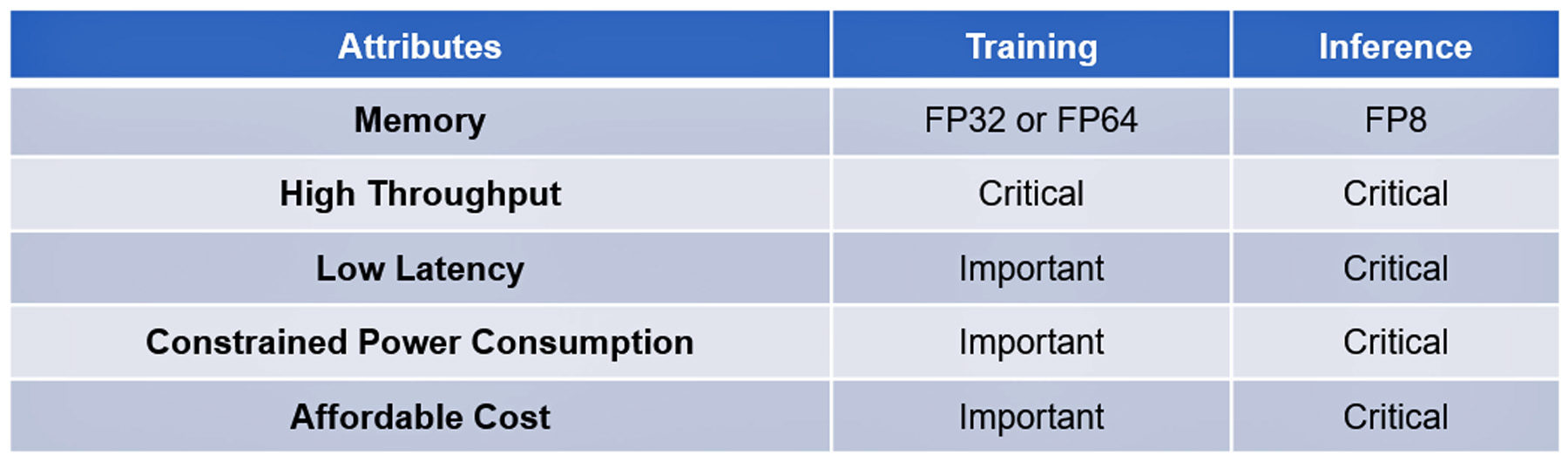

שתי הטכנולוגיות מבוססות על אלגוריתמים מודרניים ומורכבים. עיבוד ההכשרה וההסקה שלהם חולקים כמה תכונות, חלקן קריטיות, אחרות חשובות אך לא חיוניות: ראה טבלה I.

התקדמות התוכנה המדהימה בטכנולוגיות אלו לא שוכפלה עד כה על ידי התקדמות בחומרה אלגוריתמית כדי להאיץ את ביצוען. לדוגמה, למעבדים אלגוריתמיים מתקדמים אין את הביצועים לענות על שאילתות ChatGPT-4 בשניה אחת או שתיים בעלות של ¢2 לשאילתה, המדד שנקבע על ידי חיפוש Google, או לעבד את הנתונים המאסיביים נאסף על ידי חיישני AD תוך פחות מ-20 מילישניות.

זאת עד שהסטארט-אפ הצרפתי VSORA השקיע כוח מוח כדי לטפל בצוואר הבקבוק של הזיכרון המכונה חומת הזיכרון.

קיר הזיכרון

קיר הזיכרון של המעבד תואר לראשונה על ידי וולף ומקי בשנת 1994. מאז, גישה לזיכרון הפכה לצוואר הבקבוק של ביצועי מחשוב. ההתקדמות בביצועי המעבד לא באה לידי ביטוי בהתקדמות הגישה לזיכרון, מה שגרם למעבדים להמתין זמן רב יותר לנתונים שנמסרו על ידי זיכרונות. בסופו של דבר, יעילות המעבד יורדת הרבה מתחת ל-100% ניצול.

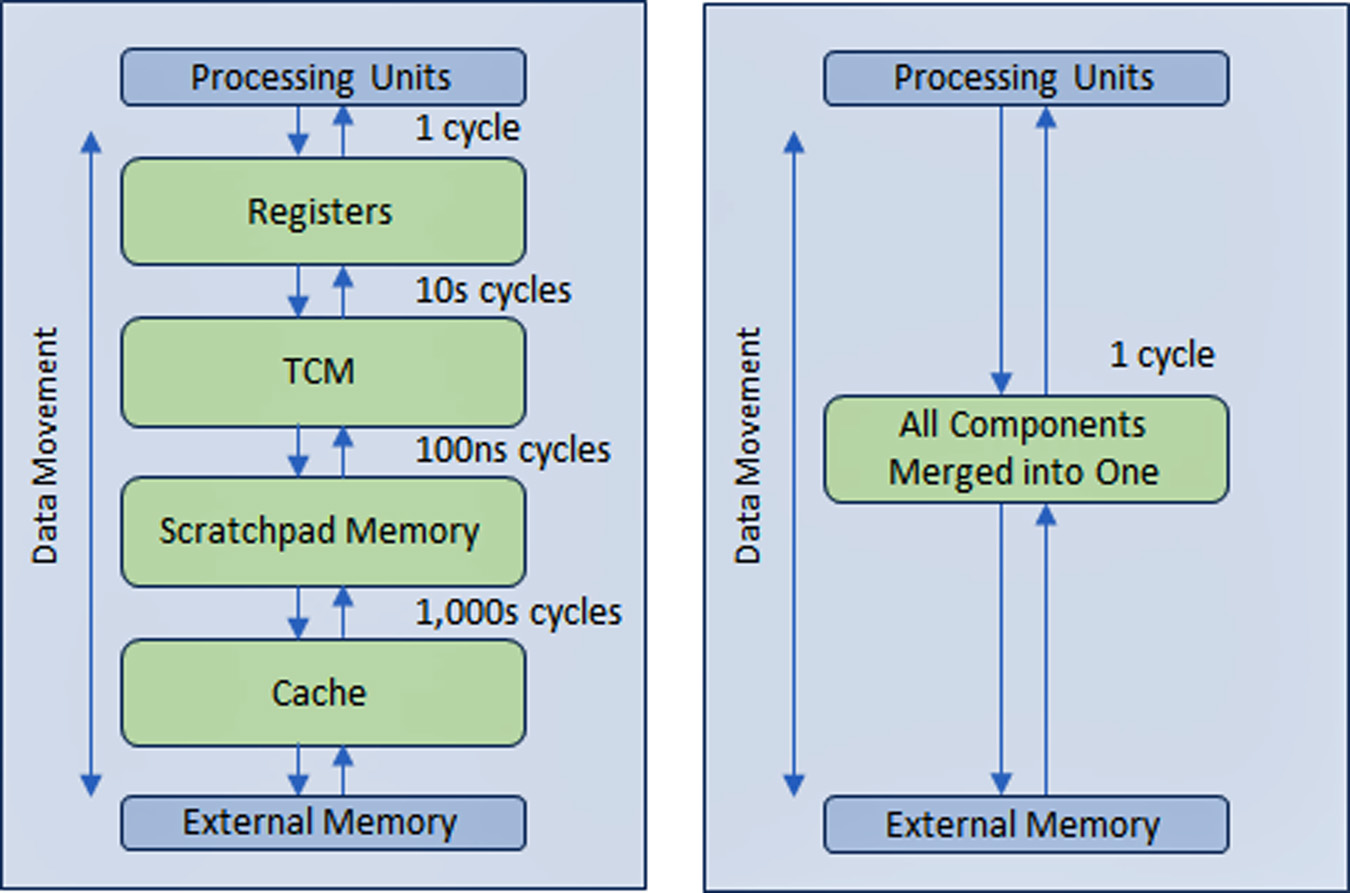

כדי לפתור את הבעיה, תעשיית המוליכים למחצה יצרה מבנה זיכרון היררכי רב-רמות עם מספר רמות של מטמון קרוב יותר למעבד שמפחית את כמות התעבורה עם הזיכרון הראשי והחיצוני האיטי יותר.

הביצועים של מעבדי AD ו-GenAI תלויים יותר מסוגים אחרים של התקני מחשוב ברוחב פס זיכרון רחב.

VSORA, שנוסדה ב-2015 כדי להתמקד ביישומי 5G, המציאה ארכיטקטורת פטנט שממוטטת את מבנה הזיכרון ההיררכי לתוך רוחב פס גדול וזיכרון צמוד הדוק (TCM) שאליו ניתן לגשת במחזור שעון אחד.

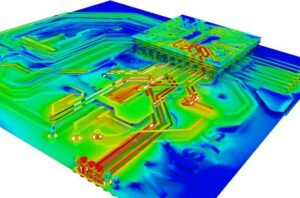

מנקודת המבט של ליבות המעבד, ה-TCM נראה ומתנהג כמו ים של רגיסטרים בכמות של MBytes לעומת kBytes של אוגרים פיזיים בפועל. היכולת לגשת לכל תא זיכרון ב-TMC במחזור אחד מניבה מהירות ביצוע גבוהה, חביון נמוך וצריכת חשמל נמוכה. זה גם דורש פחות שטח סיליקון. טעינת נתונים חדשים מזיכרון חיצוני ל-TCM בזמן שהנתונים הנוכחיים מעובדים אינה משפיעה על תפוקת המערכת. בעיקרון, הארכיטקטורה מאפשרת ניצול של 80+% של יחידות העיבוד באמצעות העיצוב שלה. ובכל זאת, ישנה אפשרות להוסיף זיכרון מטמון ו-Sratchpad אם מעצב מערכת ירצה בכך. ראה איור 1.

באמצעות מבנה זיכרון דמוי אוגר המיושם כמעט בכל הזיכרונות בכל היישומים, לא ניתן להפריז ביתרון של גישת הזיכרון VSORA. בדרך כלל, מעבדי GenAI מתקדמים מספקים אחוזי יעילות חד ספרתיות. לדוגמה, מעבד GenAI עם תפוקה נומינלית של Petaflops אחד בביצועים נומינליים אך פחות מ-5% יעילות מספק ביצועים שמישים של פחות מ-50 Teraflops. במקום זאת, ארכיטקטורת VSORA משיגה יעילות גדולה יותר מפי 10.

המאיצים האלגוריתמיים של VSORA

VSORA הציגה שתי מחלקות של מאיצים אלגוריתמיים - משפחת Tyr עבור יישומי AD ומשפחת Jotunn עבור האצת GenAI. שניהם מספקים תפוקה מדהימה, זמן השהייה מינימלי, צריכת חשמל נמוכה בטביעת רגל קטנה של סיליקון.

עם ביצועים נומינליים של עד שלושה Petaflops, הם מתהדרים ביעילות יישום טיפוסית של 50-80% ללא קשר לסוג האלגוריתם, וצריכת חשמל שיא של 30 וואט/Petaflops. אלו הן תכונות כוכבות, שעדיין לא דווח על ידי אף מאיץ AI תחרותי.

Tyr ו-Jotunn ניתנים לתכנות מלאים ומשלבים יכולות בינה מלאכותית ו-DSP, אם כי בכמויות שונות, ותומכים בבחירה תוך כדי תנועה של אריתמטיקה מ-8 סיביות ל-64 סיביות על בסיס מספר שלם או נקודה צפה. יכולת התכנות שלהם מתאימה ליקום של אלגוריתמים, מה שהופך אותם לאגנוסטיים של האלגוריתמים. נתמכים גם כמה סוגים שונים של דלילות.

התכונות של מעבדי VSORA דוחפות אותם לחזית נוף העיבוד האלגוריתמי התחרותי.

תוכנת תמיכה של VSORA

VSORA עיצבה פלטפורמת קומפילציה/אימות ייחודית המותאמת לארכיטקטורת החומרה שלה כדי להבטיח שלמכשירי ה-SoC המורכבים ובעלי הביצועים הגבוהים יש שפע של תמיכה בתוכנה.

נועדו להכניס את המעצב האלגוריתמי לתא הטייס, מגוון רמות אימות/אימות היררכיות – ESL, היברידי, RTL ו-gate – מספקים משוב בלחיצת כפתור למהנדס האלגוריתמי בתגובה לחקר החלל התכנון. זה עוזר לו או לה לבחור את הפשרה הטובה ביותר בין ביצועים, חביון, כוח ושטח. ניתן למפות קוד תכנות שנכתב ברמת הפשטה גבוהה תוך מיקוד ליבות עיבוד שונות בשקיפות למשתמש.

ניתן ליישם ממשק בין הליבות בתוך אותו סיליקון, בין שבבים על אותו PCB או דרך חיבור IP. סנכרון בין הליבות מנוהל באופן אוטומטי בזמן הקומפילציה ואינו מצריך פעולות תוכנה בזמן אמת.

מחסום דרכים לנהיגה אוטונומית L4/L5 והסקת בינה מלאכותית בקצה

פתרון מוצלח צריך לכלול גם יכולת תכנות בשטח. אלגוריתמים מתפתחים במהירות, מונעים על ידי רעיונות חדשים שהתיישנו בן לילה מהמצב החדש של אתמול. היכולת לשדרג אלגוריתם בשטח היא יתרון ראוי לציון.

בעוד שחברות היפר-סקאל הרכיבו חוות מחשוב ענקיות עם המוני מעבדי הביצועים הגבוהים ביותר שלהן כדי לטפל באלגוריתמי תוכנה מתקדמים, הגישה היא מעשית רק לאימון, לא להסקת מסקנות בקצה.

אימון מתבסס בדרך כלל על אריתמטיקה של נקודה צפה של 32 סיביות או 64 סיביות שיוצרות נפחי נתונים גדולים. הוא אינו מטיל זמן השהייה מחמיר וסובל צריכת חשמל גבוהה כמו גם עלות משמעותית.

ההסקה בקצה מבוצעת בדרך כלל על חשבון נקודה צפה של 8 סיביות שמייצר כמויות נתונים פחותות, אך מחייב השהייה בלתי מתפשרת, צריכת אנרגיה נמוכה ועלות נמוכה.

השפעת צריכת האנרגיה על האחזור והיעילות

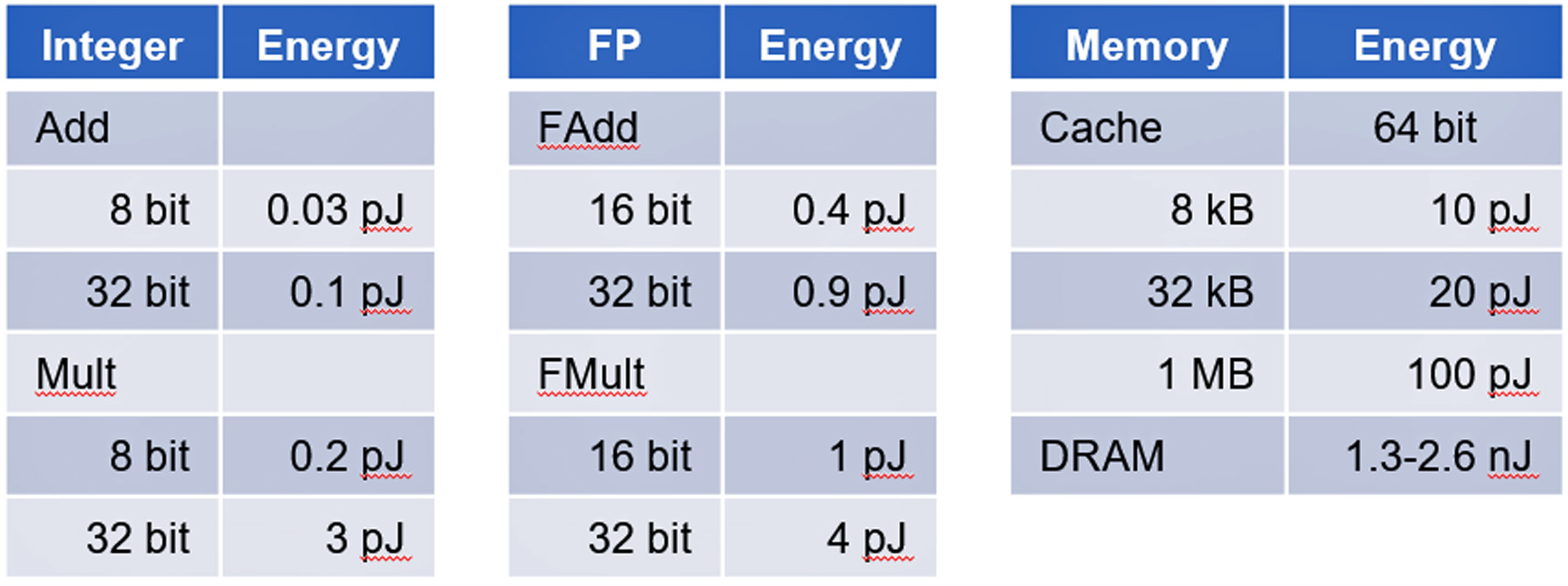

צריכת החשמל ב-CMOS IC נשלטת על ידי תנועת נתונים ולא עיבוד נתונים.

מחקר של אוניברסיטת סטנפורד בראשות פרופסור מארק הורוביץ הראה שצריכת החשמל של גישה לזיכרון צורכת סדרי גודל יותר אנרגיה מאשר חישובי לוגיקה דיגיטלית בסיסית. ראה טבלה II.

מאיצי AD ו-GenAI הם דוגמאות מובילות להתקנים הנשלטים על ידי תנועת נתונים המהווים אתגר להכיל את צריכת החשמל.

סיכום

מסקנות AD ו- GenAI מציבות אתגרים לא טריוויאליים להשגת יישומים מוצלחים. VSORA יכולה לספק פתרון חומרה מקיף ותוכנה תומכת כדי לעמוד בכל הדרישות הקריטיות לטיפול AD L4/L5 ו-GenAI כמו האצת GPT-4 בעלויות משתלמות מבחינה מסחרית.

פרטים נוספים על VSORA וה-Tyr ו-Jotunn שלה ניתן למצוא בכתובת www.vsora.com.

על לאורו ריזאטי

Lauro Rizzatti הוא יועץ עסקי של VSORA, סטארטאפ חדשני המציע פתרונות סיליקון IP ושבבי סיליקון, ויועץ אימות ידוע ומומחה בתעשייה לאמולציית חומרה. בעבר מילא תפקידים בניהול, שיווק מוצרים, שיווק טכני והנדסה.

גם לקרוא:

Soitec היא הנדסת העתיד של תעשיית המוליכים למחצה

ISO 21434 לפיתוח SoC מודע לאבטחת סייבר

תחזוקה חזויה בהקשר של בטיחות תפקודית לרכב

שתף את הפוסט הזה באמצעות:

- הפצת תוכן ויחסי ציבור מופעל על ידי SEO. קבל הגברה היום.

- PlatoData.Network Vertical Generative Ai. העצים את עצמך. גישה כאן.

- PlatoAiStream. Web3 Intelligence. הידע מוגבר. גישה כאן.

- PlatoESG. פחמן, קלינטק, אנרגיה, סביבה, שמש, ניהול פסולת. גישה כאן.

- PlatoHealth. מודיעין ביוטכנולוגיה וניסויים קליניים. גישה כאן.

- מקור: https://semiwiki.com/automotive/336201-long-standing-roadblock-to-viable-l4-l5-autonomous-driving-and-generative-ai-inference-at-the-edge/

- :יש ל

- :הוא

- :לֹא

- $ למעלה

- 000

- 1

- 10

- 1800

- 1994

- 20

- 30

- 50

- 5G

- a

- יכולת

- אודות

- הפשטה

- להאיץ

- האצה

- מאיץ

- מאיצים

- גישה

- נצפה

- גישה

- להשיג

- משיגה

- לרוחב

- מעשים

- ממשי

- Ad

- ADAs

- להוסיף

- כתובת

- מתקדם

- התקדמות

- יתרון

- יועץ

- להשפיע על

- AI

- אַלגוֹרִיתְם

- אלגוריתמי

- אלגוריתמים

- תעשיות

- מאפשר

- גם

- כמות

- כמויות

- an

- ו

- לענות

- כל

- יישומים

- גישה

- ארכיטקטורה

- ARE

- AREA

- אמנות

- AS

- At

- תשומת לב

- תכונות

- באופן אוטומטי

- רכב

- אוטונומי

- רוחב פס

- מבוסס

- בסיסי

- בעיקרון

- BE

- להיות

- היה

- להלן

- בנצ 'מרק

- הטוב ביותר

- בֵּין

- מיליארדים

- שניהם

- עסקים

- אבל

- by

- מטמון

- CAN

- לא יכול

- יכולות

- הון

- גורם

- תא

- לאתגר

- האתגרים

- שבבי

- כיתות

- שעון

- תא טייס

- קוד

- מתמוטט

- מסחרית

- קהילה

- חברות

- תחרותי

- מורכב

- מסובך

- מַקִיף

- פשרה

- חישובים

- לחשב

- מחשוב

- הקשר

- יועץ

- צְרִיכָה

- להכיל

- הקשר

- עלות

- עלויות

- יחד

- CPU

- נוצר

- קריטי

- נוֹכְחִי

- שיא הטכנולוגיה

- מחזור

- נתונים

- עיבוד נתונים

- למסור

- נתן

- מספק

- צפוף

- תלוי

- מְתוּאָר

- עיצוב

- מעוצב

- מְעַצֵב

- פרטים

- התקנים

- אחר

- דיגיטלי

- ספרות

- do

- עושה

- דולר

- מונע

- נהיגה

- ירידה

- טיפות

- בשקיקה

- אדג '

- יְעִילוּת

- או

- סוף

- אנרגיה

- צריכת אנרגיה

- מהנדס

- הנדסה

- לְהַבטִיחַ

- התלהבות

- ESL

- חיוני

- נוסד

- אי פעם

- להתפתח

- דוגמה

- דוגמאות

- הוצאת להורג

- מומחה

- חיצוני

- משפחה

- רחוק

- חוות

- מָשׁוֹב

- מעטים

- שדה

- תרשים

- ראשון

- צף

- עָקֵב

- בעד

- בחזית

- מצא

- נוסד

- צרפתית

- החל מ-

- לגמרי

- פונקציונלי

- עתיד

- מייצר

- גנרטטיבית

- AI Generative

- חיפוש Google

- יותר

- לטפל

- חומרה

- יש

- he

- הוחזק

- עוזר

- לה

- גָבוֹהַ

- ביצועים גבוהים

- הגבוה ביותר

- לו

- הורוביץ

- http

- HTTPS

- עצום

- היברידי

- i

- ICS

- רעיונות

- if

- ii

- הפעלה

- יישומים

- יושם

- חשוב

- שהוטל

- in

- לכלול

- תעשייה

- מומחה בתעשייה

- חדשני

- למשל

- במקום

- לשלב

- אל תוך

- הציג

- בדוי

- להשקיע

- מוּשׁקָע

- IP

- IT

- שֶׁלָה

- jpg

- קפיצות

- שמירה

- ידוע

- נוף

- גָדוֹל

- חֶבִיוֹן

- הוביל

- פחות

- רמה

- רמות

- כמו

- טוען

- הגיון

- ותיק

- עוד

- נראה

- נמוך

- ראשי

- תחזוקה

- עשייה

- הצליח

- ניהול

- מנדטים

- סימן

- שיווק

- מסיבי

- max-width

- לִפְגוֹשׁ

- זכרונות

- זכרון

- מילי שניות

- מינימלי

- מודרני

- כסף

- יותר

- תנועה

- מספר

- המונים

- חדש

- לילה

- ציין

- ראוי לציון

- עַכשָׁיו

- מְיוּשָׁן

- of

- הצעה

- on

- ONE

- רק

- תפעול

- or

- להזמין

- הזמנות

- אחר

- אחרים

- יותר

- בין לילה

- מוגזמים

- פטנט

- שִׂיא

- עבור

- אחוזים

- ביצועים

- ביצעתי

- פרספקטיבה

- גופני

- פלטפורמה

- אפלטון

- מודיעין אפלטון

- אפלטון נתונים

- שפע

- נקודה

- עמדות

- אפשרות

- הודעה

- כּוֹחַ

- מעשי

- קוֹדֶם

- ראשוני

- בעיה

- תהליך

- מעובד

- תהליך

- מעבד

- מעבדים

- המוצר

- פרופסור

- ניתן לתכנות

- תכנות

- התקדמות

- להניע

- גם

- שאילתות

- רכס

- מהר

- חומר עיוני

- זמן אמת

- מציאות

- לאחרונה

- מפחית

- ללא קשר

- רושמים

- ראוי לציון

- משוכפל

- דווח

- לדרוש

- דרישות

- דורש

- תגובה

- אותו

- SEA

- חיפוש

- שניות

- לִרְאוֹת

- מבחר

- סמיקונדקטור

- חיישנים

- כמה

- שיתוף

- שיתופים

- צריך

- הראה

- סיליקון

- since

- יחיד

- קטן

- So

- תוכנה

- פִּתָרוֹן

- פתרונות

- לפתור

- כמה

- במידה מסוימת

- מָקוֹר

- מֶרחָב

- מְהִירוּת

- בילה

- סטנפורד

- אוניברסיטת סטנפורד

- סטארט - אפ

- מדינה

- מדינה-of-the-art

- כוכב

- עוד

- זִרמִי

- מחמירות

- מִבְנֶה

- לימוד

- ניכר

- מוצלח

- תמיכה

- נתמך

- מסייע

- סִנכְּרוּן

- מערכת

- שולחן

- מותאם

- יעד

- מיקוד

- טכני

- טכנולוגיות

- מֵאֲשֶׁר

- זֶה

- השמיים

- העתיד

- שֶׁלָהֶם

- אותם

- שם.

- אלה

- הֵם

- זֶה

- שְׁלוֹשָׁה

- דרך

- תפוקה

- בחוזקה

- זמן

- פִּי

- ל

- היום

- לעקוב

- מסורתי

- תְנוּעָה

- הדרכה

- בשקיפות

- שתיים

- סוג

- סוגים

- טיפוסי

- בדרך כלל

- ייחודי

- יחידות

- עולם

- אוניברסיטה

- עד

- שדרוג

- שָׁמִישׁ

- משתמש

- באמצעות

- תעודות סל

- מיזם

- הון סיכון

- אימות

- נגד

- באמצעות

- בַּר חַיִים

- כמעט

- כרכים

- לחכות

- קיר

- היה

- דֶרֶך..

- טוֹב

- מתי

- בזמן

- רָחָב

- משאלות

- עם

- בתוך

- כתוב

- עוד

- תשואות

- זפירנט