Sono in fase di sviluppo nuove strutture bump per consentire densità di interconnessione più elevate negli imballaggi flip-chip, ma sono complesse, costose e sempre più difficili da produrre.

Per i prodotti con un numero elevato di pin, flip-chip [1] I package sono da tempo una scelta popolare perché utilizzano l'intera area del die per l'interconnessione. La tecnologia è in uso dagli anni '1970, a partire dal C4 di IBM (connessione del chip a collasso controllato), ma è diventata davvero diffusa negli anni '1990.

Da allora, la tecnologia bump si è evoluta per gestire la crescente densità di connessione di potenza e segnale richiesta dalla memoria, dall'elaborazione ad alte prestazioni e dai dispositivi informatici mobili. Soddisfare tale domanda richiede una nuova tecnologia di interconnessione che consenta bump pitch più piccoli, attualmente in produzione.

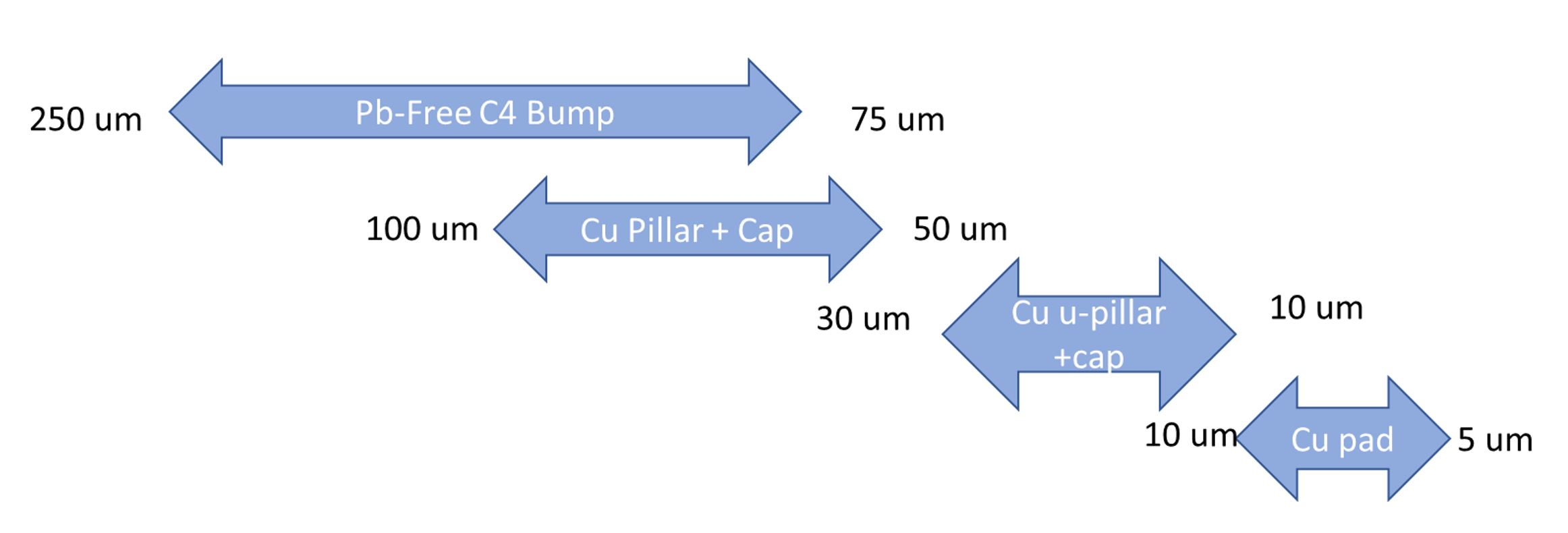

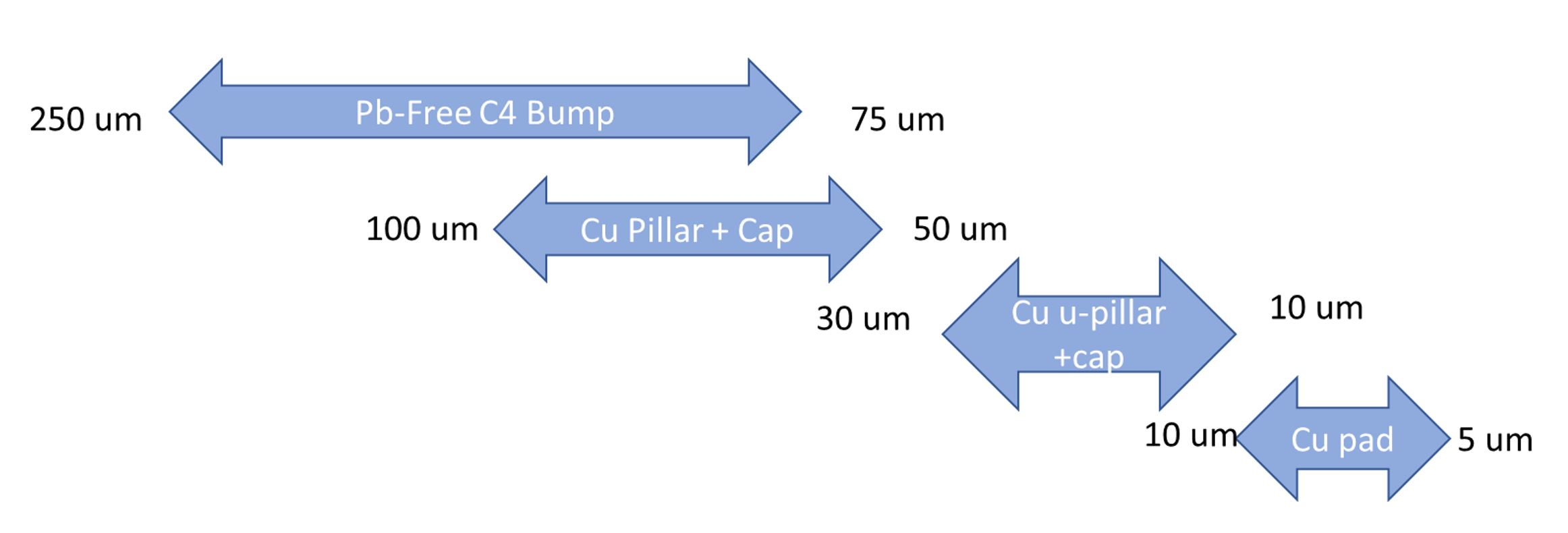

Considerata nel tempo, la tabella di marcia per l'interconnessione flip-chip progredisce dai bump senza piombo ai pilastri in rame, quindi ai microbump in rame. Le dimensioni del passo continuano a ridursi, il che a sua volta ha creato sfide di produzione per il bumping e l'incollaggio.

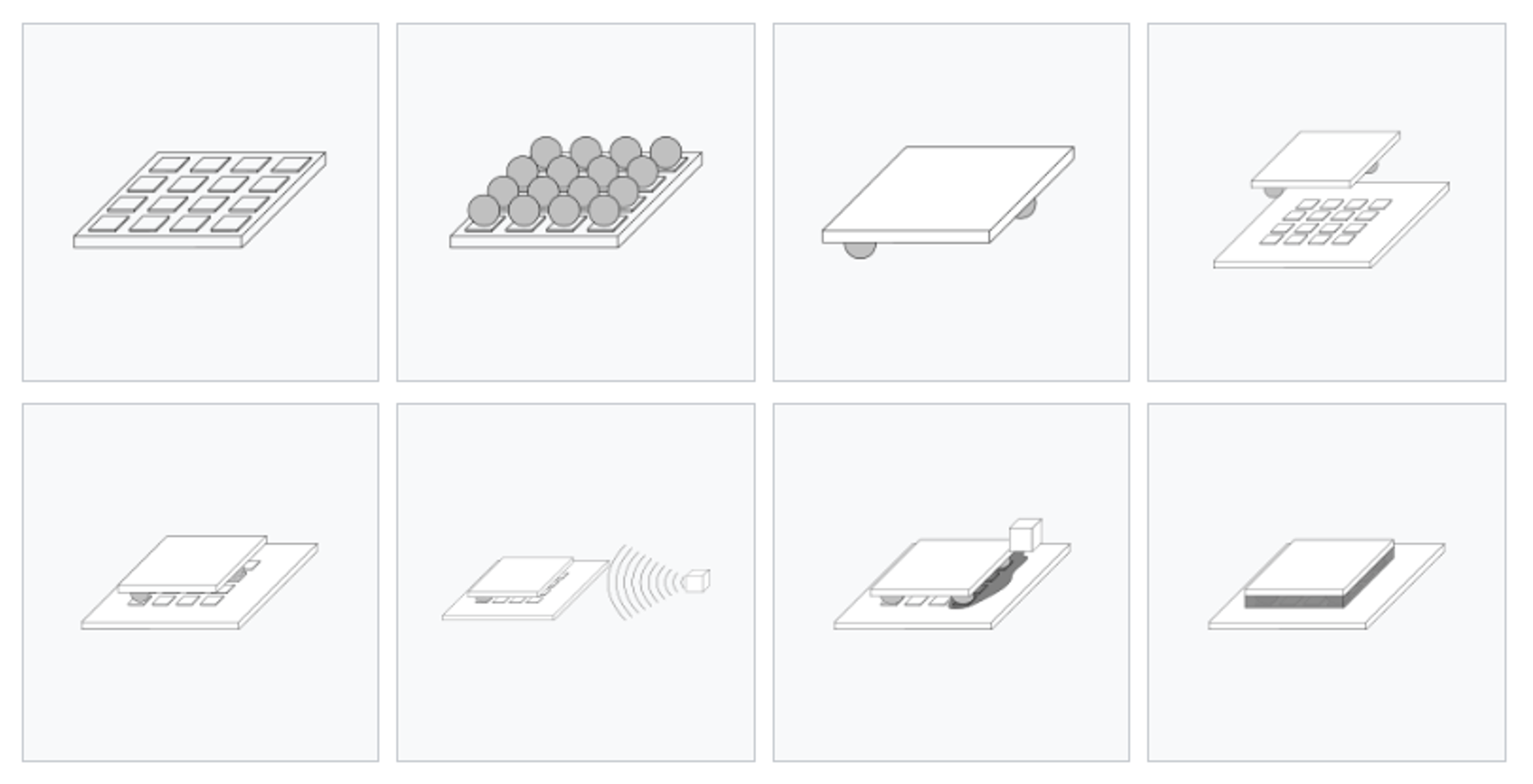

Fig. 1: Intervalli di passo della tecnologia Flip-chip. Fonte: A. Meixner/Semiconductor Engineering

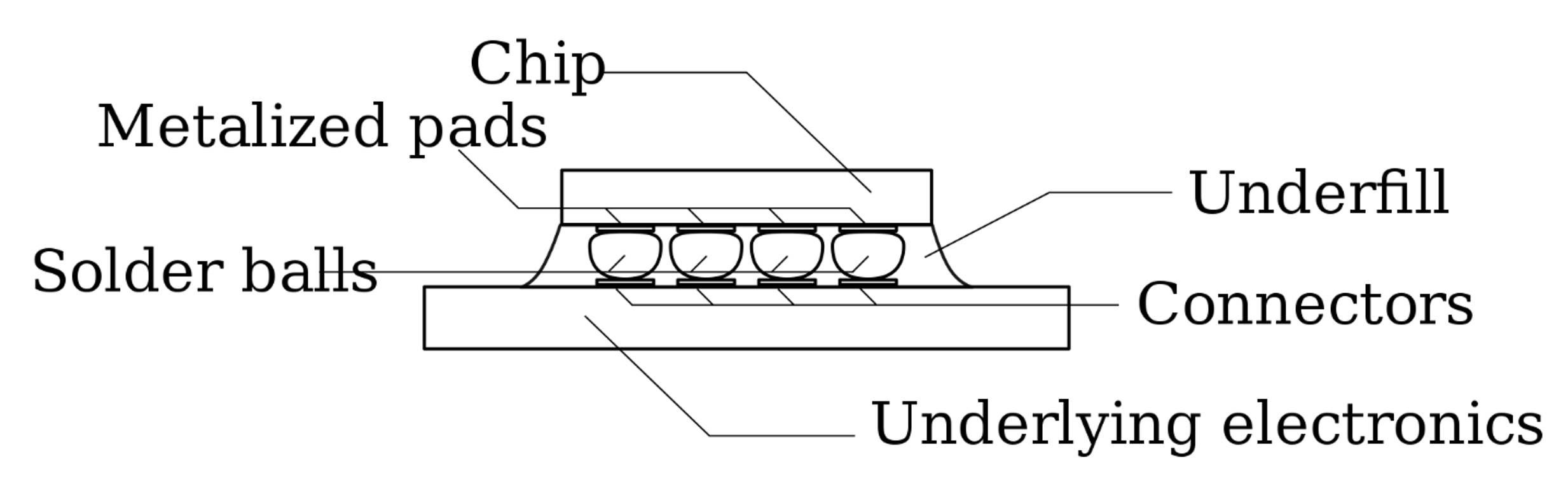

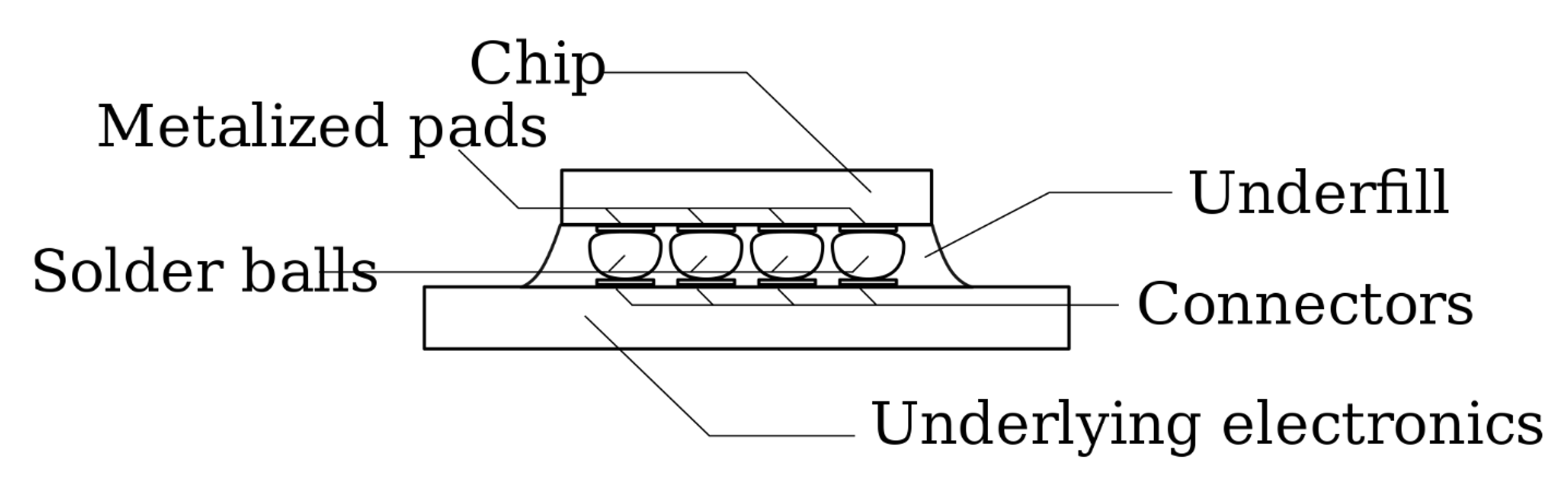

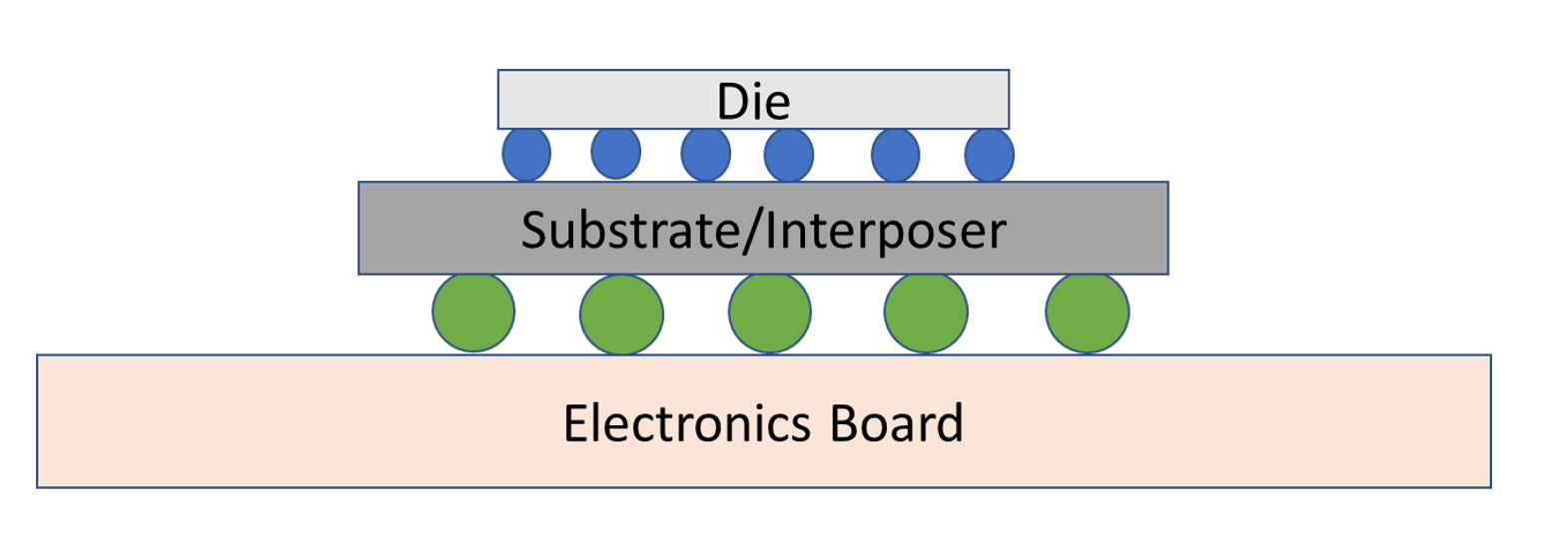

Fig. 2: Componenti del flip-chip. Fonte: wikipedia

“Nel campo dei flip-chip – con passo di 250 micron e inferiore – originariamente si trattava di protuberanze di piombo e stagno, e una delle grandi mosse è stata quella senza piombo. Ma quando si iniziano a raggiungere i 100 micron o meno, si inizia a vedere più un pilastro di rame, anche se c'è una sovrapposizione poiché vediamo pilastri di rame fino a 250 micron", ha affermato Jeff Schaefer, ingegnere di processo senior presso Industrie Promex. “Con il passo da 250 micron, vediamo dimensioni di protuberanze di 130 micron o diametri dei pilastri di rame. Una volta che raggiungiamo il passo di 100 micron, il diametro è di 80 micron. Il più piccolo che ho visto è un passo da 62.5 micron con un pilastro da 40 micron. Mi aspetto di iniziare presto a vedere un passo da 50 micron”.

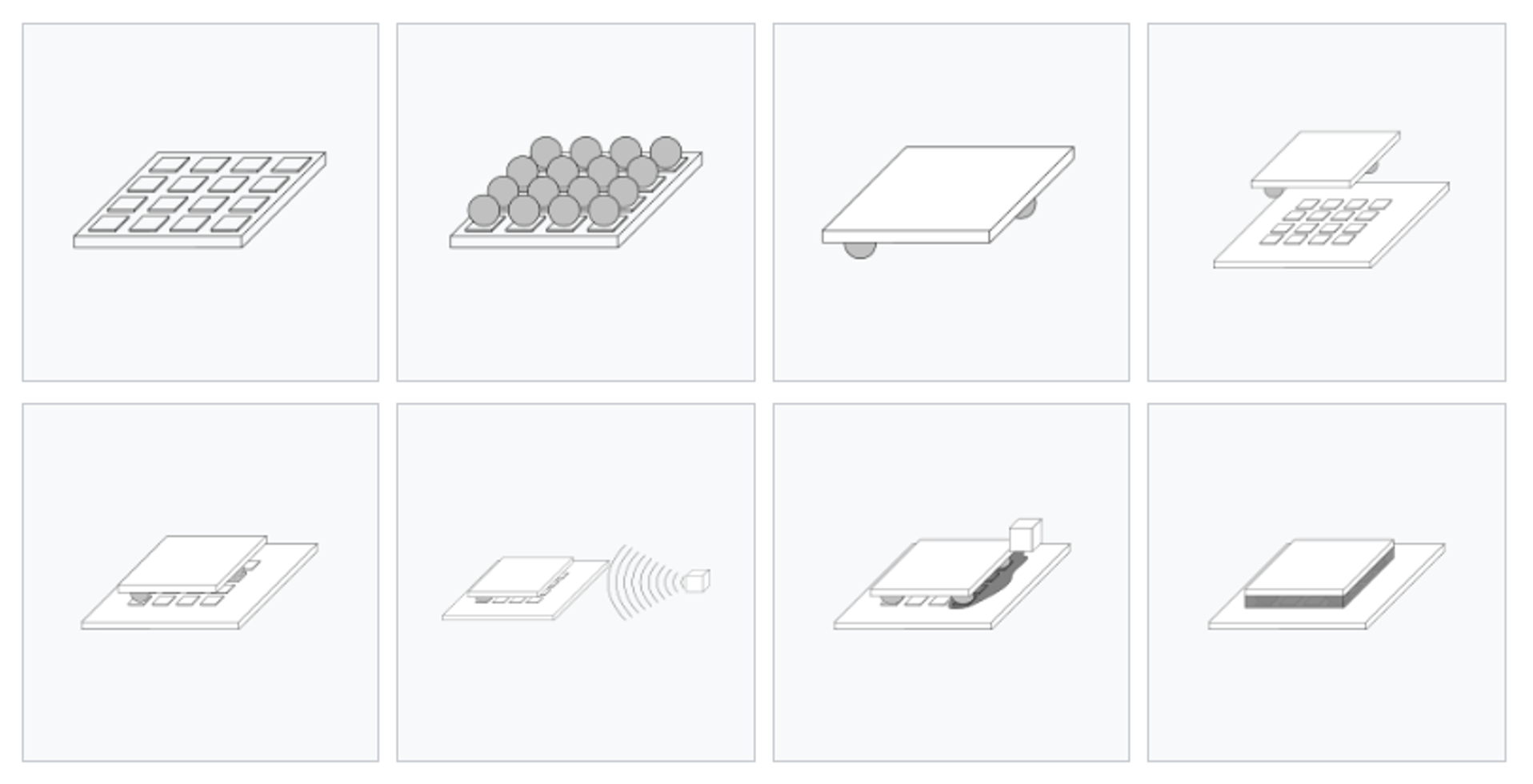

Il processo di base del flip-chip inizia dopo la fabbricazione del circuito, quando sulla superficie del die vengono creati dei cuscinetti metallici per il collegamento agli I/O. Poi c'è il wafer bumping, dove una sfera di saldatura viene depositata su ciascun pad. Il wafer viene quindi tagliato a cubetti e le matrici vengono capovolte e posizionate in modo che le sfere di saldatura si allineino con i cuscinetti del substrato. Le sfere di saldatura vengono quindi fuse/rifuse, in genere utilizzando aria calda, e una matrice montata viene riempita in modo insufficiente con un adesivo elettricamente isolante, solitamente utilizzando l'azione capillare. [1]

Fig. 3: Processo di produzione del flip-chip. Fonte:Wikipedia

Il passaggio a un pilastro o microbump in rame richiede la litografia per creare queste strutture.

"Il pilastro in rame viene generalmente utilizzato con un passo inferiore a 130 µm, perché invece di essere una protuberanza di saldatura circolare, il pilastro in rame è principalmente un pilastro in Cu con una saldatura sulla parte superiore", ha affermato Doug Scott, vicepresidente senior del confezionamento a livello di wafer presso Tecnologia Amkor. "Ciò consente di posizionare le protuberanze dei pilastri in rame più vicine tra loro senza il rischio che la saldatura si colleghi durante il riflusso dell'assemblaggio - generalmente, ~40 µm Cu + ~25 µm."

Ci sono anche variazioni sul tema. "Microbump, che è un termine comune utilizzato quando si ha un'interconnessione tra silicio e silicio, è leggermente diverso perché il CTE (coefficiente di espansione termica) è generalmente lo stesso", ha affermato Mark Gerber, direttore senior per l'ingegneria/marketing tecnico A Gruppo ASE. “Alcune delle regole generali di progettazione utilizzate per il pilastro in rame sono le stesse, ma la topografia della superficie piana e i giunti a bassa sollecitazione consentono flessibilità del sottoriempimento utilizzato. Questo può anche guidare il pitch del bump individuale. Oggi è possibile un bump full-array pitch da 35 µm, grazie alle considerazioni di routing menzionate in precedenza, per il routing a livello di wafer o di fab utilizzato”.

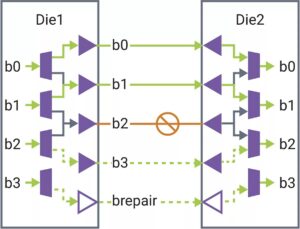

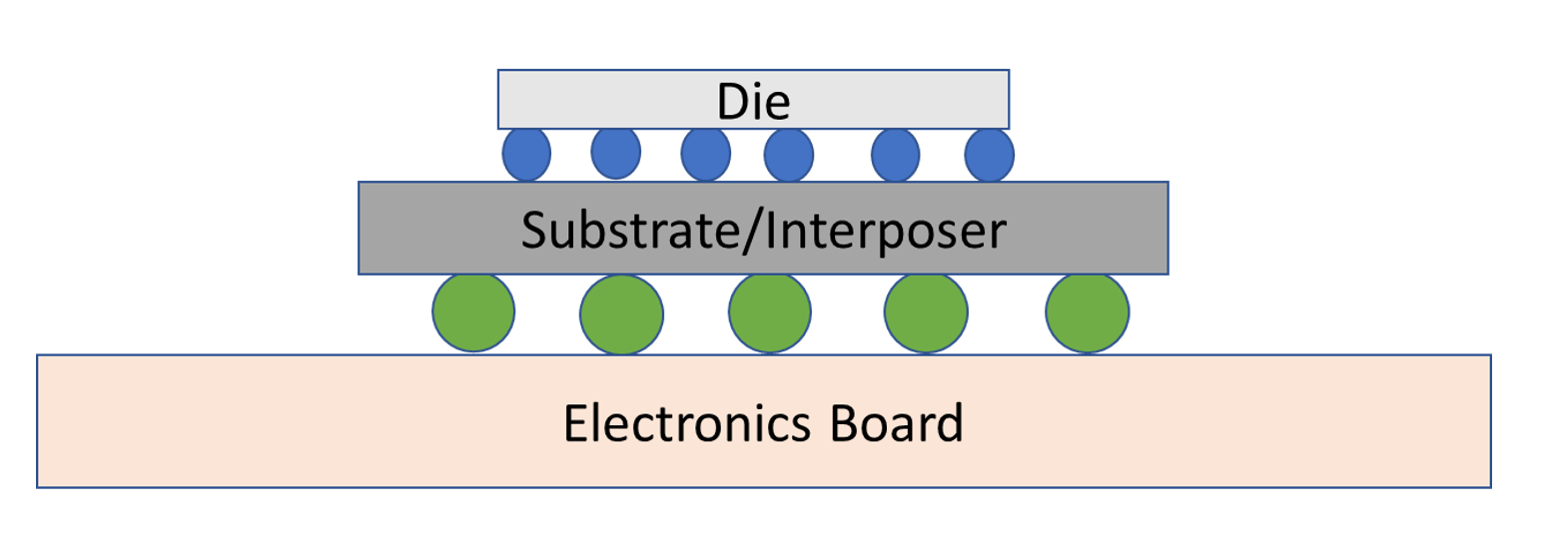

La tabella di marcia per l'integrazione eterogenea [2] descrive tutti gli aspetti del packaging, comprese le interconnessioni die-substrato che vanno dai wire-bond ai vias di silicio passante. Con i package flip-chip, le interconnessioni die-substrato, le aree di ridistribuzione del substrato e le interconnessioni substrato-scheda svolgono tutte un ruolo nei limiti di produzione.

Fig. 4: Schema concettuale dell'imballaggio flip-chip. Fonte: A. Meixner/Semiconductor Engineering

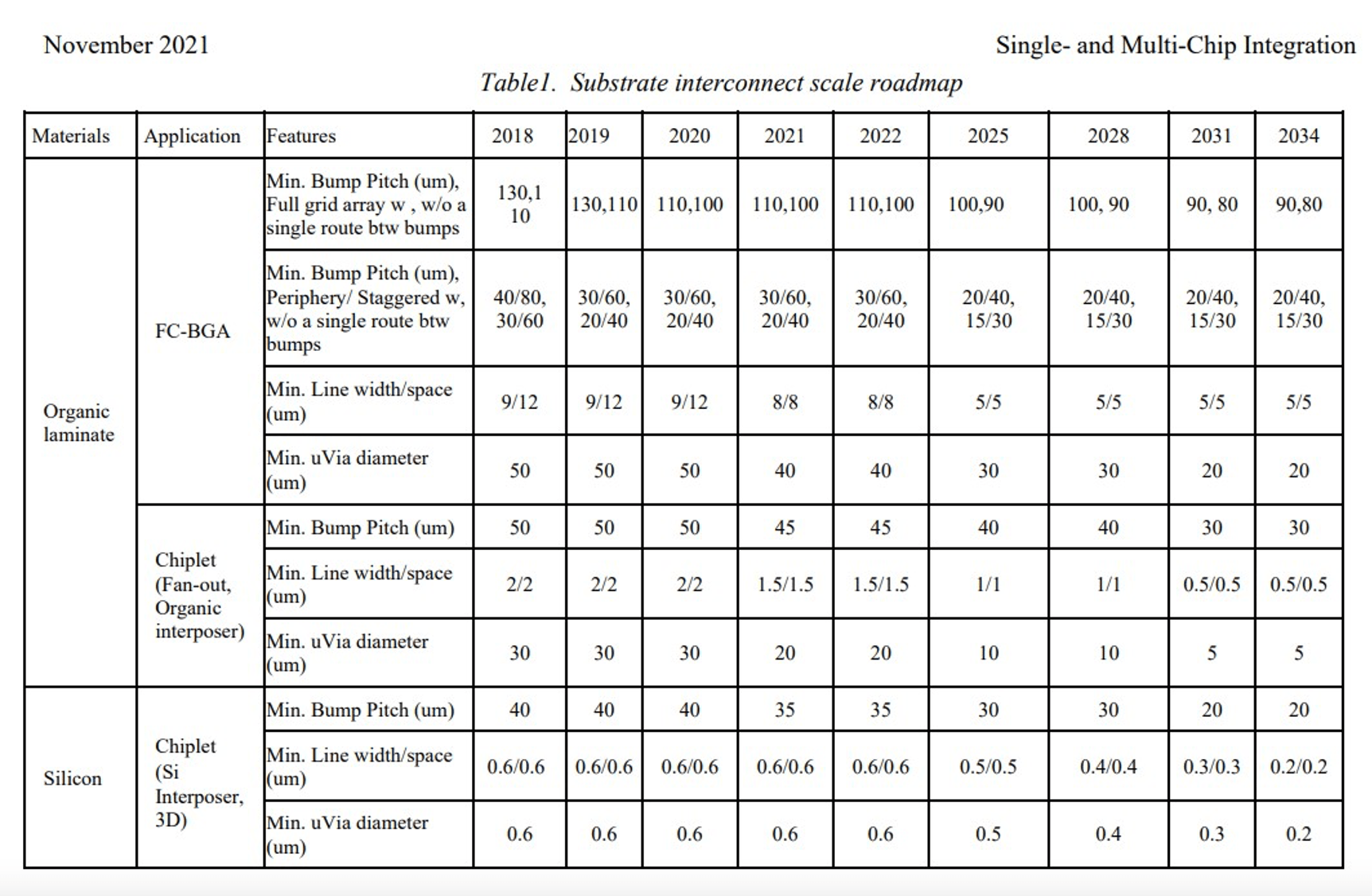

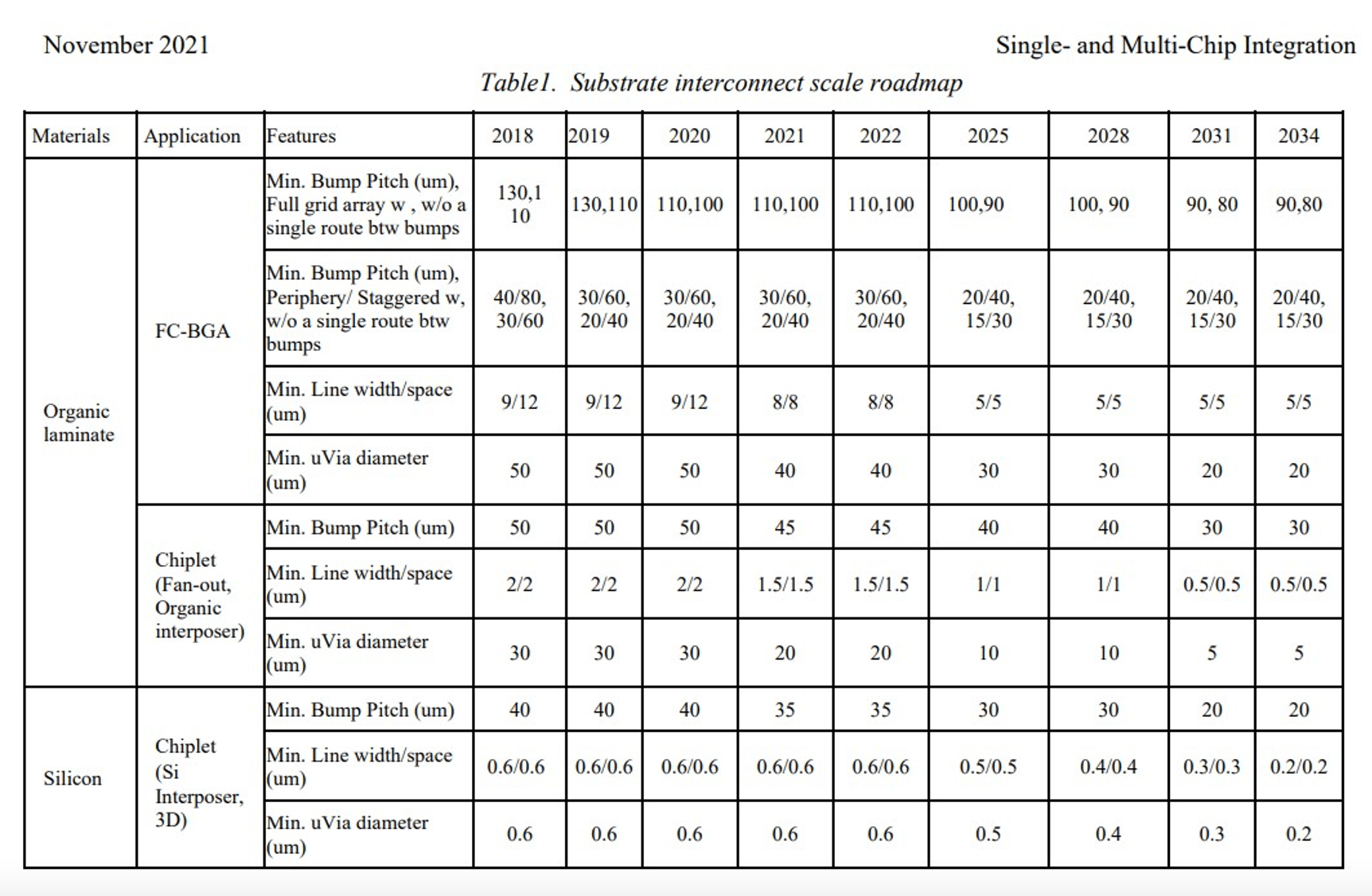

Il capitolo 8 della tabella di marcia per l'integrazione eterogenea [3] documenta il panorama delle iniziative attuali e previste sulla tecnologia di imballaggio. Il passo minimo di ciascuna tecnologia di interconnessione flip-chip è riportato nella Tabella 1 della sottosezione 8.7 (pagina 41).

![Il capitolo 8 della tabella di marcia per l'integrazione eterogenea [3] documenta il panorama delle iniziative attuali e previste sulla tecnologia di imballaggio. Il passo minimo di ciascuna tecnologia di interconnessione flip-chip è riportato nella Tabella 1 della sottosezione 8.7 (pagina 41).](https://platoaistream.com/wp-content/uploads/2023/05/challenges-grow-for-creating-smaller-bumps-for-flip-chips-7.png)

![Il capitolo 8 della tabella di marcia per l'integrazione eterogenea [3] documenta il panorama delle iniziative attuali e previste sulla tecnologia di imballaggio. Il passo minimo di ciascuna tecnologia di interconnessione flip-chip è riportato nella Tabella 1 della sottosezione 8.7 (pagina 41).](https://platoaistream.com/wp-content/uploads/2023/05/challenges-grow-for-creating-smaller-bumps-for-flip-chips-8.png)

La tabella corrispondente per l'interconnessione del substrato (la parte che collega il pacchetto alla scheda) si trova nella sottosezione 8.8 (pagina 43).

Con ogni cambiamento nella tecnologia di interconnessione arrivano nuovi processi e i relativi limiti, che guidano l'innovazione, la gestione della resa e l'ispezione dei difetti.

Superare i limiti della tecnologia

La tecnologia del bumping viene misurata in base al passo, alle dimensioni, all'altezza e alle proprietà elettriche e meccaniche. Le considerazioni termiche variano a seconda della mancata corrispondenza del CTE del materiale. La deformazione è un problema per die e wafer più grandi, che viene esacerbato dalla molatura posteriore di un wafer prima del fissaggio della matrice.

"Esistono numerosi fattori che determinano le limitazioni di passo per ciascun tipo di interconnessione", ha affermato Gerber di ASE. “A partire dalla tradizionale interconnessione bump flip chip di saldatura, la capacità del passo è determinata dall’altezza di collasso per il riempimento insufficiente, dal passo del pad di cattura per l’instradamento della traccia, dal passo del pad di cattura per il rischio corto bump-to-bump e da molte altre sensibilità legate al passo. L'altezza della protuberanza premontata ha un'altezza definita, ma come IBM ha definito il termine C4 - Connessione del chip a collasso controllato - il diametro della protuberanza di saldatura e la dimensione del pad di cattura determineranno il "collasso o l'altezza finale" dell'interconnessione. Questo è il principale fattore di limitazione del passo per l’utilizzo di protuberanze di saldatura legate al passo.

L'altezza del bump è determinata dal design, ma anche dalle scelte di lavorazione.

“Per i bump di saldatura placcati standard e i pill bump in rame, le altezze dei bump pre-assemblaggio sono generalmente comprese tra 70 µm e 75 µm, con altezze dei bump collassati dopo l’assemblaggio di ~ 50 µm per consentire lo spazio x,y,z per il flusso di riempimento insufficiente tra i bump. I microbump avranno altezze di rilievo molto inferiori e comporteranno la placcatura di molta meno saldatura. Nello specifico, i microbump possono essere alti meno di 10 µm con altezze di Cu e saldatura ridotte a seconda del passo e delle esigenze finali”, ha affermato Scott di Amkor. “I bump di saldatura placcati standard vengono generalmente utilizzati su passi che vanno da 130 µm a 250 µm. Al di sotto di 130 µm, non c’è abbastanza spazio xy tra i rilievi quando si inizia con un’altezza del rilievo pre-assemblaggio di 70 µm.

La creazione di pilastri in rame richiede più fasi di lavorazione rispetto ai dossi di saldatura.

“Quando siamo passati al mondo die-to-die, la tecnologia è diversa perché ora hai a che fare con un wafer e le planeriti sono molto buone rispetto al die-substrato. Per prima cosa si crea il pilastro di rame, sul wafer iniziale che riceverà la saldatura o il pilastro di rame c'è prima un under bump metal (UBM). È un piccolo cappuccio sopra l'apertura che scende nel silicio. Quindi costruiamo un nucleo di rame da quello e poi ci mettiamo sopra un cappuccio di stagno. Quindi, il wafer di ricezione sembra avere un pad UBM lì e di solito ha una placcatura in nichel-oro su di esso in modo che sia bello e incontaminato", ha spiegato Schaefer di Promex Industries. Quindi invece di avere una leggera rientranza come un substrato laminato, si ha una leggera estrusione. Abbiamo scoperto che siamo in grado di saldarli effettivamente ad umido senza "saldare sul pad". È così che sono progettati e costruiti. Funziona quasi come una saldatura e un pad perché è una piccola cupola invece di cercare di scendere all'interno di un foro.

Le fasi di fotolitografia necessarie per la formazione dei pilastri di Cu presentano limiti e regole di progettazione del substrato.

"Per il pilastro in rame, che consiste in un perno in rame e un cappuccio di saldatura sulla punta, l'altezza del perno in rame può essere definita limitando uno o più spessori dello strato di fotoresist e riducendo il passo, le proporzioni del L'altezza del palo in inclinazione diventa il limite insieme al materiale fotoresist e alle capacità dello strumento di imaging", ha affermato Gerber. “Una limitazione secondaria per l’interconnessione con pilastro in rame sono le regole di progettazione del substrato utilizzate. Per passo fine >110um, vengono utilizzati 2 metodi principali: BOT (Bond on Trace) o ET – Embedded Trace, in cui il cappuccio di saldatura del pilastro di rame viene posizionato sopra la traccia invece di un tradizionale pad di cattura. Le dimensioni e la forma dei pilastri in rame, comprese le limitazioni di cui sopra, possono rappresentare un limite alle capacità e alla tabella di marcia per continuare a ridurre le falde. Molte di queste limitazioni sono dovute alla capacità di instradare le tracce tra i pilastri sul lato del substrato. Man mano che saranno disponibili nuove tecnologie, come l’RDL a livello di wafer, le roadmap di interconnessione verranno spinte ulteriormente, ma ancora con limitazioni riguardo al rapporto altezza/aspetto per i processi di produzione come l’underfill”.

Altri concordano sul fatto che il processo di riempimento insufficiente comporta delle sfide. “Man mano che il passo diventa più fine, i dossi più piccoli si accorciano. Ora sta diventando difficile trovare riempimenti insufficienti per passare sotto. I riempimenti insufficienti sono stati storicamente progettati per essere inferiori a uno spazio di 5 mil, mentre ora scendono a 3 mil, ovvero 75 micron”, ha affermato Schaefer. “Ora stiamo iniziando a vedere gap di 60 e 25 micron. Sono sicuro che le persone stanno lavorando su nuovi riempimenti insufficienti. Ma ci sono molte cose su cui lavorare. Per prima cosa, man mano che si ottengono particolati più fini, diventa più simile a un fango, il che rende più difficile il flusso. Questo è un ostacolo che deve essere rimosso”.

Gestire il rendimento

Man mano che la tecnologia bumping si riduce, ulteriori fasi di lavorazione, ad esempio la litografia per la creazione di pilastri in rame, aprono nuove opportunità per i rilevatori di rendimento. Per un processo di incollaggio di successo, i particolati, i contaminanti superficiali e lo svuotamento dei rilievi della saldatura sono problematici per la resa. Questi richiedono controlli di processo, metrologia e ispezione.

È necessario controllare naturalmente la contaminazione. "Gli OSAT di livello 1 investono per ridurre il livello delle fonti di contaminazione della fabbrica e quindi ridurre le percentuali di difettosità", ha affermato Scott di Amkor. “Il tono non contribuisce alla difettosità. Livelli simili di difettosità esistono indipendentemente dal tono”.

Ma il campo aggiunge alcune delle sue sfide. “Poiché il passo si riduce e le dimensioni della protuberanza si riducono, la gestione della contaminazione delle particelle è molto importante. Per altri tipi di interconnessioni come il bonding ibrido, dove i passi sono ridotti al di sotto di 30 µm e il contatto superficie-superficie è importante, l'ambiente pulito basato su wafer è fondamentale per i rendimenti", ha affermato Gerber di ASE.

Non è da sottovalutare nemmeno la preparazione al processo di underfill.

"In genere con un laminato, si esegue un riempimento insufficiente dopo aver eseguito il flip chip", ha affermato Schaefer di Promex. “Determiniamo dove lo posizioneremo e come risistemarlo. Lo puliamo per far fuoriuscire qualsiasi materiale disossidante sotto lo spazio tra la fustella e il substrato. Quindi riempiremo in modo insufficiente con una resina epossidica che scorre. È progettato per bagnarsi e non lasciare vuoti e cose del genere. Ma c'è una sfida quando arriviamo a tiri più fini. Le protuberanze si accorciano leggermente e man mano che si accorciano lo spazio tra il chip e il substrato si riduce, quindi è più difficile da pulire. Immagina di unire due vetrini per cercare di eliminare lo sporco tra di loro.

Esigenze metrologiche e di ispezione

Per la gestione del controllo e della resa del processo, gli strumenti metrologici e di ispezione svolgono un ruolo importante. "Sul mercato sono disponibili strumenti che possono aiutare a fornire indicazioni sull'integrità dell'interconnessione, oltre all'analisi trasversale in-process utilizzata durante la configurazione e a intervalli di produzione definiti", ha affermato Gerber di ASE.

Il processo di bumping e i processi di incollaggio hanno ciascuno caratteristiche specifiche che devono essere monitorate. Per le irregolarità, la metrologia si concentra su diametro, altezza e complanarità. I passi più piccoli richiedono un controllo più rigoroso del diametro del dosso e del controllo dell'altezza. Allo stesso modo, quando l’altezza del rilievo si riduce, la finestra di complanarità diventa più piccola. In genere è consentita una variazione del 10%. Ad esempio, un'altezza di rilievo di 30 µm comporta una variazione consentita di ±3 µm. Il superamento di questo limite contribuisce a un legame inefficace o inadeguato.

"L'incollaggio viene solitamente effettuato con forni a rifusione di massa", ha affermato Mike Kelly, vicepresidente dei pacchetti avanzati e dell'integrazione tecnologica di Amkor. “La caratterizzazione iniziale del processo di rifusione viene stabilita utilizzando l’effetto moiré per quantificare la deformazione durante la rifusione e la mappatura della temperatura dei forni per garantire un controllo coerente della temperatura della parte flip-chip stessa. Durante l'installazione, viene eseguito il sollevamento meccanico dello stampo e l'ispezione per garantire una buona bagnatura della saldatura. Inoltre, il flusso viene solitamente applicato con un "flusso ad immersione", in cui i dossi dello stampo vengono "immersi" in serbatoi di flusso sottili e strettamente controllati. L’ispezione visiva di questi elementi viene effettuata su base campionaria”.

La crescente automazione dell’ispezione visiva riduce la dipendenza dagli operatori per visualizzare un’immagine e prendere una decisione. L'aumento esponenziale delle connessioni bump è un driver. Le modifiche ai processi di incollaggio ne forniscono un altro. Un processo di riflusso della saldatura autoallineato è una tecnologia matura. Con l'incollaggio a compressione termica comunemente utilizzato negli imballaggi avanzati, esistono meccanismi di affidabilità che superano i test elettrici. Ciò, a sua volta, richiede l’uso di strumenti di ispezione a raggi X e metrologici per visualizzare le irregolarità dopo l’incollaggio.

“Per gli imballaggi a bassa complessità, le strutture potrebbero farla franca con un operatore e un’ispezione manuale. Per una parte con 100 urti questo metodo è fattibile. A 1,000 colpi, è sicuramente uno sforzo. Una volta che una parte ha 10,000 rilievi, non c'è più alcuna possibilità. Andiamo oltre questo punto e dobbiamo passare al metodo successivo", ha osservato Frank Chen, direttore delle applicazioni e della gestione del prodotto presso Sta guardando. “La qualità e la complessità vanno di pari passo, perché quando provi a realizzare qualcosa di più complesso la tua resa ne risentirà e saranno necessari nuovi strumenti. E per attrezzature si intendono sia strumenti di processo che strumenti metrologici, quindi entrambi devono avanzare in parallelo. Dai nostri studi, vediamo che una volta arrivati a quei 1,000 colpi, è allora che devi iniziare a pensare 'La mia tecnica manuale è insufficiente e ho bisogno di qualcosa di nuovo.'”

Sono disponibili numerosi strumenti di ispezione e metrologia per supportare la produzione di imballaggi.

“Esistono diversi metodi che possono o dovrebbero essere utilizzati per ottenere il controllo del processo. Innanzitutto, l'ispezione 2D tradizionale (AOI) per l'ispezione del 100% dei difetti superficiali per flusso di processo (ad esempio, IQC, OQA, foto, pulizia, placcatura, ecc.). Successivamente, la metrologia 2D (AOI) può essere utilizzata per controllare le dimensioni del rilievo e il dimensionamento del diametro controllo. Inoltre, la metrologia 3D (AOI) può essere utilizzata per l'acquisizione di informazioni metrologiche di campionamento sull'altezza del rilievo/co-planarità (questo viene in genere fatto con una tecnologia basata sulla triangolazione laser)", ha affermato Nathan Peng, responsabile marketing del prodotto presso Sull'innovazione. “Inoltre, la metrologia 3D può individuare le caratteristiche individuali dell’altezza del dosso, generalmente raccolte con la tecnologia dell’interferometro a luce bianca. Inoltre, esistono metodi per consentire il rilevamento di residui organici sulla parte superiore del bump top che possono portare a guasti nel collegamento tra bump e pad."

Conclusione

I prodotti che richiedono un numero maggiore di interconnessioni continuano a guidare la tabella di marcia dell’interconnessione. Ciascuna tecnologia flip-chip presenta limiti di produzione che coinvolgono proprietà dei materiali, dimensioni ridotte che mettono in discussione le tecnologie di riempimento insufficiente e un maggiore utilizzo della litografia per creare le strutture di interconnessione. Qualsiasi cambiamento nei processi di incollaggio si traduce in un aumento delle fasi metrologiche e di ispezione per soddisfare gli obiettivi di resa e qualità.

Riferimenti

- https://en.wikipedia.org/wiki/Flip_chip

- https://eps.ieee.org/technology/heterogeneous-integration-roadmap/2021-edition.html

- HIR Capitolo 8 Integrazione a chip singolo e multi chip, https://eps.ieee.org/images/files/HIR_2021/ch08_smcfinal.pdf

Storie correlate:

La co-planarità e le incongruenze causano problemi di resa e affidabilità

Le sfide legate al confezionamento avanzato aumentano man mano che i chip e le dimensioni delle confezioni si riducono; attrezzature diverse, le tecnologie guadagnano terreno.

L'affidabilità del bump è messa alla prova da difetti latenti

Le soluzioni automatizzate sono in lavorazione, ma ci vorrà del tempo per svilupparsi.

Grandi cambiamenti in vista di alimentazione, materiali e interconnessioni

Come cambieranno la produzione e il confezionamento nei prossimi due decenni.

- Distribuzione di contenuti basati su SEO e PR. Ricevi amplificazione oggi.

- PlatoAiStream. Intelligenza dei dati Web3. Conoscenza amplificata. Accedi qui.

- Coniare il futuro con Adryenn Ashley. Accedi qui.

- Acquista e vendi azioni in società PRE-IPO con PREIPO®. Accedi qui.

- Fonte: https://semiengineering.com/challenges-grow-for-creating-smaller-bumps-for-flip-chips/

- :ha

- :È

- :non

- :Dove

- $ SU

- 000

- 1

- 10

- 100

- 250

- 2D

- 3d

- 40

- 7

- 8

- a

- capacità

- capace

- sopra

- Raggiungere

- acquisizione

- Action

- atti

- effettivamente

- aggiunta

- aggiuntivo

- Aggiunge

- avanzare

- Avanzate

- Dopo shavasana, sedersi in silenzio; saluti;

- avanti

- ARIA

- allineare

- Tutti

- consentire

- consente

- lungo

- anche

- an

- .

- ed

- Un altro

- in qualsiasi

- applicazioni

- applicato

- SONO

- RISERVATA

- aree

- in giro

- AS

- aspetto

- aspetti

- montaggio

- At

- allegare

- Automazione

- disponibile

- lontano

- precedente

- palla

- basic

- base

- BE

- perché

- diventa

- stato

- prima

- essendo

- sotto

- fra

- Al di là di

- Big

- tavola

- legame

- Bot

- entrambi

- costruire

- costruito

- ma

- by

- è venuto

- Materiale

- berretto

- funzionalità

- catturare

- Causare

- Challenge

- sfidato

- sfide

- possibilità

- il cambiamento

- Modifiche

- Capitolo

- caratteristiche

- chen

- patata fritta

- Chips

- scegliere

- scelte

- più vicino

- Crollo

- crollato

- Venire

- viene

- Uncommon

- comunemente

- rispetto

- complesso

- complessità

- componenti

- informatica

- concettuale

- Problemi della Pelle

- Connettiti

- Collegamento

- veloce

- Connessioni

- collega

- Considerazioni

- coerente

- contatti

- contaminanti

- continua

- continua

- contribuire

- di controllo

- controllata

- controllo

- controlli

- Rame

- Nucleo

- Corrispondente

- potuto

- Coppia

- creare

- creato

- Creazione

- critico

- Corrente

- Attualmente

- dati

- trattare

- decenni

- decisione

- definito

- decisamente

- consegna

- Richiesta

- densità

- Dipendente

- depositato

- Design

- progettato

- rivelazione

- Determinare

- determinato

- sviluppare

- sviluppato

- dispositivi

- *

- diverso

- difficile

- Direttore

- lo sporco

- do

- documenti

- effettua

- fatto

- giù

- guidare

- autista

- driver

- dovuto

- durante

- e

- E&T

- ogni

- o

- incorporato

- enable

- Abilita

- fine

- ingegnere

- Ingegneria

- abbastanza

- garantire

- Ambiente

- usate

- sviluppate

- eccetera

- Etere (ETH)

- si è evoluta

- esempio

- esistere

- espansione

- attenderti

- costoso

- ha spiegato

- esponenziale

- strutture

- fattore

- fabbrica

- Fallimento

- Fico

- finale

- Trovare

- sottile

- Nome

- piatto

- Flessibilità

- Capovolgere

- flusso

- flussi

- FLUSSO

- si concentra

- Nel

- per rendimento

- formazione

- essere trovato

- da

- ulteriormente

- Inoltre

- Guadagno

- divario

- lacune

- Generale

- generalmente

- ottenere

- ottenere

- vetro.

- Go

- va

- andando

- Oro

- buono

- macinazione

- Crescere

- guida

- maniglia

- Hard

- Avere

- avendo

- altezza

- altezza

- Aiuto

- Alta

- Alte prestazioni

- superiore

- storicamente

- Foro

- HOT

- Come

- Tutorial

- HTML

- HTTPS

- IBRIDO

- i

- IBM

- IEEE

- Immagine

- immagine

- Imaging

- impattato

- importante

- in

- Compreso

- Aumento

- è aumentato

- crescente

- sempre più

- individuale

- informazioni

- inizialmente

- Innovazione

- invece

- integrazione

- interezza

- interconnessioni

- ai miglioramenti

- Investire

- coinvolgere

- IT

- elementi

- SUO

- stessa

- paesaggio

- superiore, se assunto singolarmente.

- laser

- strato

- portare

- Lasciare

- meno

- Livello

- livelli

- leggera

- piace

- LIMITE

- limitazione

- limiti

- limiti

- piccolo

- Lunghi

- Guarda

- una

- lotto

- Basso

- Principale

- make

- FA

- gestione

- direttore

- gestione

- Manuale

- manualmente

- consigliato per la

- molti

- mappatura

- marchio

- Rappresentanza

- Marketing

- materiale

- Materiale

- alunni

- max-width

- si intende

- meccanico

- meccanismi di

- Soddisfare

- incontro

- Memorie

- menzionato

- metallo

- metodo

- metodi

- metrologia

- micron

- microfono

- ordine

- Mobile

- monitorati

- Scopri di più

- soprattutto

- cambiano

- si muove

- molti

- Multi

- Natura

- Bisogno

- di applicazione

- esigenze

- New

- Nuove tecnologie

- GENERAZIONE

- bello

- Nichel, Ni free

- no

- noto

- adesso

- numero

- Obiettivi d'Esame

- of

- on

- una volta

- ONE

- aprire

- apertura

- operatore

- Operatori

- Opportunità

- opposto

- or

- biologico

- originariamente

- Altro

- nostro

- su

- ancora

- proprio

- pacchetto

- Packages

- imballaggio

- sentiero

- pagina

- Parallel

- parte

- particella

- passare

- Persone

- Pilastro

- Intonazione

- piazzole

- posto

- Platone

- Platone Data Intelligence

- PlatoneDati

- Giocare

- punto

- povero

- Popolare

- scelta popolare

- posizionato

- possibile

- Post

- energia

- Presidente

- primario

- Precedente

- processi

- i processi

- lavorazione

- Prodotto

- gestione del prodotto

- Produzione

- Prodotti

- proiettato

- proprietà

- fornire

- spinto

- metti

- qualità

- che vanno

- rapporto

- raggiungendo

- veramente

- ricevente

- ridurre

- Ridotto

- riduce

- Indipendentemente

- relazionato

- problemi di

- fiducia

- rimosso

- richiedere

- necessario

- richiede

- Risultati

- Rischio

- tabella di marcia

- roadmap

- Ruolo

- Prenotazione sale

- strada

- instradamento

- norme

- Suddetto

- stesso

- secondario

- vedere

- vedendo

- visto

- semiconduttore

- anziano

- flessibile.

- alcuni

- Forma

- spostamento

- Corti

- dovrebbero

- lato

- Signal

- Silicio

- simile

- Allo stesso modo

- da

- singolo

- Taglia

- Dimensioni

- Diapositive

- leggermente diversa

- inferiore

- So

- Soluzioni

- alcuni

- qualcosa

- Arrivo

- Fonte

- fonti

- lo spazio

- specifico

- in particolare

- Standard

- inizia a

- Di partenza

- Passi

- adesivo

- Ancora

- Storie

- stress

- studi

- di successo

- tale

- supporto

- superficie

- SVG

- tavolo

- Fai

- Target

- Tecnologie

- Tecnologia

- termine

- Testing

- di

- che

- I

- Il paesaggio

- loro

- Li

- tema

- poi

- Là.

- perciò

- termico

- Strumenti Bowman per analizzare le seguenti finiture:

- di

- cose

- Pensiero

- questo

- quelli

- anche se?

- strettamente

- tempo

- tipo

- a

- oggi

- insieme

- strumenti

- top

- tracciare

- trazione

- tradizionale

- prova

- TURNO

- seconda

- Digitare

- Tipi di

- tipicamente

- per

- su

- uso

- utilizzato

- utilizzando

- generalmente

- utilizzare

- varietà

- molto

- Vicepresidente

- Visualizza

- svuotamento

- Prima

- we

- WELL

- quando

- quale

- bianca

- tutto

- molto diffuso

- wikipedia

- volere

- con

- senza

- Lavora

- lavoro

- lavori

- mondo

- X

- raggi X

- dare la precedenza

- i rendimenti

- Tu

- Trasferimento da aeroporto a Sharm

- zefiro