La resistività del rame dipende dalla sua struttura cristallina, dal volume dei vuoti, dai bordi dei grani e dal disadattamento dell'interfaccia del materiale, che diventa più significativo su scale più piccole. La formazione di fili di rame (Cu) viene tradizionalmente eseguita incidendo un modello di trincea in biossido di silicio a basso k utilizzando un processo di incisione in trincea e successivamente riempiendo la trincea con Cu tramite un flusso damasceno. Sfortunatamente, questo metodo produce strutture multicristalline con bordi di grano e vuoti significativi, che aumentano la resistenza del filo di Cu. In questo processo viene utilizzato anche un materiale di rivestimento TaN altamente resistente per prevenire la diffusione di Cu durante il processo di ricottura damascena.

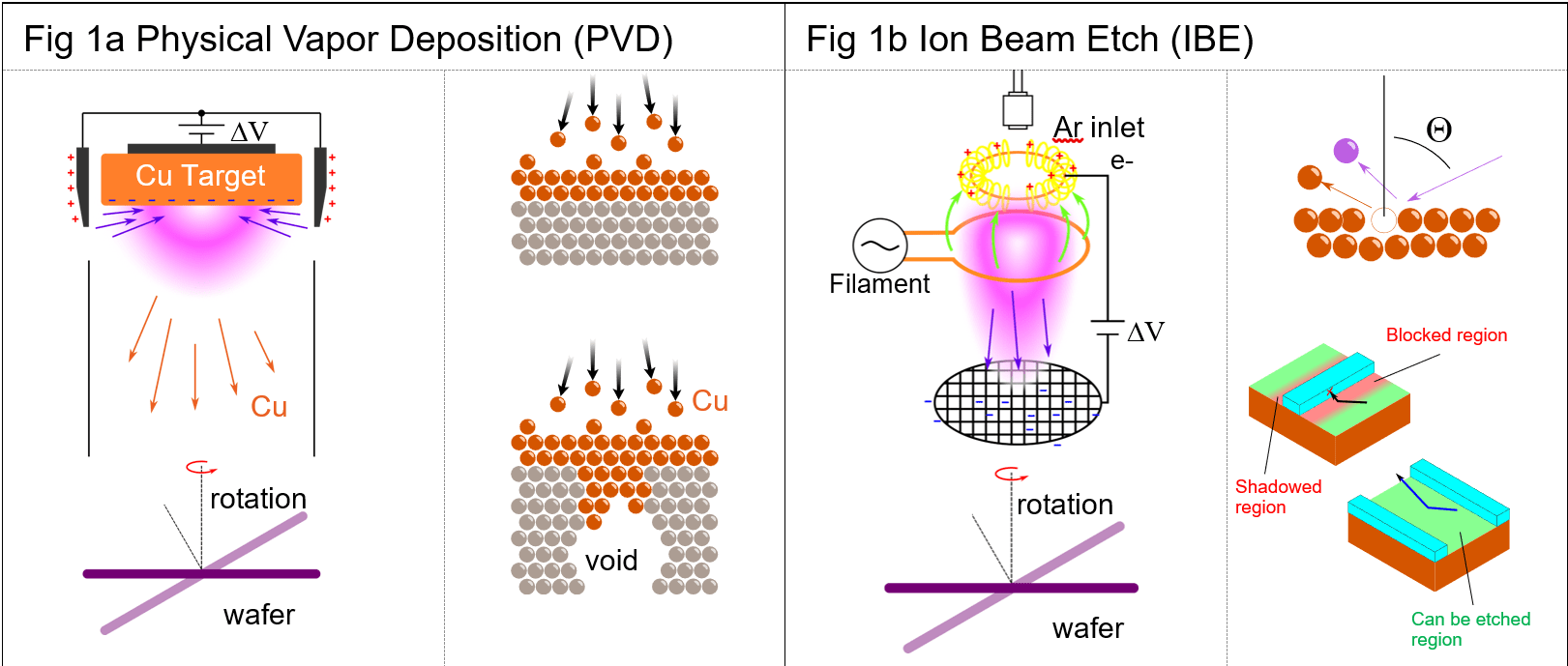

La deposizione fisica da fase vapore (PVD) può essere utilizzata per depositare il rame ad elevate energie cinetiche (tra 10 e 100 eV), formando strutture monocristalline dense e a bassa resistenza. Uno svantaggio del PVD è che la deposizione PVD ha una linea di vista diffusa e può essere depositata uniformemente solo su superfici piane. Non può essere utilizzato per riempire buche profonde o trincee (figura 1a). Per formare forme di filo isolate, uno strato uniforme di Cu deve essere depositato su una superficie piana e poi attaccato fisicamente da fasci ionici. Il Cu non forma composti volatili con i gas reattivi, quindi non è possibile utilizzare un processo di attacco con ioni reattivi. Gli ioni Ar accelerati creati durante l'attacco con fascio ionico (IBE) possono rimuovere Cu se l'angolo di incidenza è molto elevato. Sfortunatamente, le regioni attaccabili saranno limitate a causa degli effetti di ombreggiatura della maschera. La Figura 1b mostra le regioni (in rosso) in cui il materiale non può essere inciso quando la maschera è perpendicolare al fascio ionico in entrata. Questo errore di incisione si verifica a causa dell'ombreggiamento o del blocco del percorso dell'atomo espulso. Quando la maschera è parallela al percorso dello ione, tutte le regioni non mascherate possono essere incise. Pertanto, l'attacco con fascio ionico è limitato all'attacco di maschere a forma di linea di lunghezze arbitrarie.

![]()

Fig. 1: (1a) Deposizione fisica da vapore (PVD); (1b) Incisione con fascio ionico (IBE).

Fasi del processo e processo di fabbricazione virtuale

Per comprendere l'effetto della deposizione e dell'incisione sulla resistenza della linea, modelliamo ora i processi di incisione PVD e IBE utilizzando le funzioni di deposizione e incisione di visibilità di SEMulator3D. Il PVD è stato riprodotto utilizzando un processo di deposizione con visibilità diffusa angolare di 30 gradi in SEMulator3D, che modella accuratamente la natura casuale degli atomi di Cu espulsi durante il bombardamento con ioni AR. L'IBE è stato riprodotto nel modello utilizzando un'incisione di visibilità con una diffusione angolare di 2 gradi e un'inclinazione dell'angolo polare di 60 gradi, per riflettere il comportamento degli ioni accelerati dalla griglia con divergenza del raggio anabbagliante. Si presuppone che entrambi i wafer abbiano rotazione libera. Altre fasi del processo sono state adattate nel processo di fabbricazione virtuale per soddisfare i vincoli IBE e PVD. La Figura 2 mostra la stessa struttura creata utilizzando sia un riempimento Cu damascene (figura 2a) che il processo PVD/IBE (figura 2b). Sono state incluse ulteriori fasi del processo per incorporare alcune limitazioni di PVD/IBE e creare la forma equivalente per le nostre strutture finali desiderate.

![]()

Fig. 2: (2a) Fabbricazione di filo di Cu con riempimento damascato; (2b) Fabbricazione di fili PVD/IBE Cu.

Dimostriamo quindi che una cella di circuito SRAM equivalente da 16 nm può essere fabbricata con fili PVD/IBE rispettando queste limitazioni. Poiché tutti gli strati metallici sopra l'estremità centrale della linea sono fabbricati da una superficie piana, ciò lo rende un candidato ideale per i cavi PVD/IBE, a differenza delle complesse topologie di interconnessione viste in un dispositivo finFET. La Figura 3 mostra la struttura isolata di ciascuno strato metallico e i passaggi necessari per creare una struttura finFET a tre strati metallici utilizzando PVD/IBE.

![]()

Fig. 3: (3a) FinFET MEOL da 16 nm e 3 strati metallici; (3b) Fabbricazione passo dopo passo dello strato metallico tramite PVD/IBE.

Risultati della resistenza e conclusioni

Quindi misuriamo la resistenza elettrica dei fili dallo strato metallico più alto fino ai canali dei canali P e N del finFET, sia per il flusso damasceno che per la deposizione fisica del vapore. La Figura 4 mostra il punto iniziale e il punto finale della misurazione della resistenza sui canali P e N (tutti gli altri materiali isolanti sono trasparenti). Per compensare la resistenza dell'interfaccia tra il rivestimento TaN e il filo di rame, la resistività del rame è stata aumentata utilizzando una costante di decadimento esponenziale di 1 nm in funzione della distanza più vicina all'interfaccia TaN. Poiché non si prevede che una deposizione di Cu di riempimento damascena sia completamente cristallina, la resistività del Cu è stata aumentata del 50%. Il processo del rame PVD/IBE non utilizza un rivestimento TaN, quindi la funzione di decadimento esponenziale non è stata applicata e in questo modello è stata utilizzata la resistività complessiva del rame. Nella Figura 4 è inclusa una tabella di resistività che confronta un flusso damasceno con un flusso PVD.

![]()

Fig. 4: Punto iniziale e punto finale della misurazione della resistenza sui canali P e N.

I valori di resistenza calcolati dal nostro modello indicano che possiamo ottenere una diminuzione del 67% della resistenza utilizzando il metodo di fabbricazione IBE/PVD rispetto ad un attacco convenzionale in trincea seguito da deposizione damascena. Ciò si verifica poiché non è necessario alcun rivestimento TaN in IBE/PVD e durante questo processo la resistività CU è inferiore. I nostri risultati indicano che è possibile ottenere miglioramenti di resistività utilizzando IBE/PVD rispetto al riempimento damascato durante la formazione della linea metallica, al costo di un processo di fabbricazione più complesso.

Timoteo Yang

(tutti i post)

Timothy Yang è un ingegnere di applicazioni software presso Coventor, una società di ricerca Lam. Lavora nello sviluppo di processi, nell'integrazione e nelle applicazioni di miglioramento della resa, con esperienza nelle tecnologie di memoria. Prima del suo lavoro presso Coventor, Yang ha lavorato presso Tokyo Electron sviluppando schemi di incisione, tecniche di miglioramento dei modelli post-litografia, controllo del flusso di processo per applicazioni di modellazione SADP e SAQP e tecnologia EUV e fotoresist per litografia ad immersione. Yang ha conseguito la laurea in fisica presso l'UCLA, un master in scienze dei materiali presso il Chiba Institute of Technology e un dottorato di ricerca. laurea in Scienze dei Materiali presso l'Università di Tohoku.

- Distribuzione di contenuti basati su SEO e PR. Ricevi amplificazione oggi.

- Platoblockchain. Web3 Metaverse Intelligence. Conoscenza amplificata. Accedi qui.

- Coniare il futuro con Adryenn Ashley. Accedi qui.

- Fonte: https://semiengineering.com/a-deposition-and-etch-technique-to-lower-resistance-of-semiconductor-metal-lines/

- :ha

- :È

- ][P

- 1

- 10

- 100

- a

- sopra

- accelerata

- ospitare

- con precisione

- Raggiungere

- raggiunto

- aggiuntivo

- Rettificato

- Tutti

- Tutti i messaggi

- ed

- Angular

- applicazioni

- applicato

- AR

- SONO

- AS

- assunto

- At

- atomo

- BE

- Larghezza

- diventa

- stato

- fra

- confini

- by

- calcolato

- Materiale

- candidato

- non può

- certo

- canali

- azienda

- rispetto

- confronto

- complesso

- costante

- vincoli

- di controllo

- convenzionale

- Rame

- Costo

- creare

- creato

- Cristallo

- dati

- diminuire

- deep

- Laurea

- dimostrare

- dipende

- deposito

- depositato

- desiderato

- in via di sviluppo

- Mercato

- dispositivo

- Emittente

- display

- distanza

- Divergenza

- giù

- durante

- ogni

- effetto

- effetti

- o

- ingegnere

- Equivalente

- EV

- previsto

- competenza

- esponenziale

- Fallimento

- figura

- riempire

- piatto

- flusso

- seguito

- Nel

- modulo

- formazione

- forme

- Gratis

- da

- completamente

- function

- funzioni

- Griglia

- Avere

- he

- Alta

- vivamente

- Fori

- HTTPS

- idea

- immersione

- miglioramento

- miglioramenti

- in

- incidente

- incluso

- In arrivo

- incorporare

- è aumentato

- Aumenta

- indicare

- Istituto

- integrazione

- Interfaccia

- isolato

- IT

- SUO

- jpg

- Lam

- strato

- galline ovaiole

- limiti

- Limitato

- linea

- Linee

- Lunghi

- Basso

- FA

- mask

- Mascherine

- materiale

- Materiale

- max-width

- misurare

- Memorie

- metallo

- metodo

- In mezzo

- modello

- modelli

- Scopri di più

- Natura

- necessaria

- di applicazione

- of

- on

- minimo

- Altro

- nostro

- Parallel

- sentiero

- Cartamodello

- Fisico

- Fisicamente

- Fisica

- Platone

- Platone Data Intelligence

- PlatoneDati

- punto

- polare

- Post

- Post

- prevenire

- Precedente

- processi

- i processi

- casuale

- ricevuto

- Rosso

- riflettere

- regioni

- rimuovere

- riparazioni

- resistenza all'usura

- Risultati

- s

- stesso

- bilancia

- schemi

- Scienze

- semiconduttore

- Forma

- a forma di

- forme

- Spettacoli

- Vista

- significativa

- Silicio

- da

- singolo

- inferiore

- So

- Software

- diffondere

- Di partenza

- Regione / Stato

- step

- Passi

- La struttura

- Successivamente

- superficie

- tavolo

- tecniche

- Tecnologie

- Tecnologia

- che

- Il

- Strumenti Bowman per analizzare le seguenti finiture:

- tre

- miniature

- a

- Tokyo

- più in alto

- tradizionalmente

- trasparente

- ucla

- capire

- Università

- uso

- utilizzato

- utilizzati

- Valori

- via

- virtuale

- visibilità

- volatile

- volume

- vs

- quale

- while

- volere

- Wire

- con

- Lavora

- lavorato

- lavori

- dare la precedenza

- zefiro