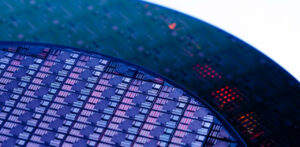

Banias Labs è un'azienda di semiconduttori che sviluppa soluzioni infrastrutturali per le comunicazioni di prossima generazione. Il suo mercato di riferimento è il mercato delle infrastrutture informatiche ad alte prestazioni, tra cui data center iperscala, reti, intelligenza artificiale, moduli ottici e SoC switch Ethernet per progetti emergenti di elaborazione ad alte prestazioni. Questi SoC richiedono progetti Ethernet ad alta velocità e soluzioni a bassa latenza per fornire prestazioni di sistema migliorate e accelerare il time-to-market. L'azienda ha sviluppato un SoC DSP ottico con tecnologia di processo a 5 nm per soddisfare le esigenze di questo mercato.

![]()

Un SoC DSP ottico è un tipo specializzato di system-on-chip (SoC) progettato per l'uso in sistemi di comunicazione ottica ad alta velocità. Oltre al DSP, il SoC DSP ottico include in genere blocchi IP di interfaccia ad alta velocità, come Ethernet PHY IP, PCIe IP e controller di memoria DDR. Questi tipi di SoC consentono trasferimenti di dati ad alta velocità a basse latenze per l'elaborazione del segnale in tempo reale. Sono inoltre progettati per ridurre al minimo il consumo energetico, rendendoli ideali per applicazioni che richiedono un funzionamento efficiente con problemi termici ridotti. Con i vantaggi arrivano anche le sfide. I requisiti specializzati dei sistemi di comunicazione ottica rendono la progettazione di un SoC DSP ottico più impegnativa rispetto alla progettazione di un SoC normale.

Sfide di implementazione

Le sfide ruotano attorno alla complessità del progetto, ai rigidi requisiti di potenza e prestazioni e alla necessità di soddisfare vari standard di settore. L'integrazione di più blocchi IP tra cui il processore DSP, Ethernet PHY IP e altri blocchi personalizzati richiede un'attenta progettazione e convalida. Ulteriori interfacce ad alta velocità come PCIe e DDR aggiungono ulteriore complessità al progetto. Le interfacce ad alta velocità e i molteplici blocchi IP nel sistema possono creare distorsioni del segnale, diafonia e interferenze elettromagnetiche, che possono influire sulle prestazioni e sull'affidabilità del sistema. L'analisi e l'ottimizzazione dell'integrità del segnale e dell'alimentazione devono essere eseguite nelle prime fasi del ciclo di progettazione per garantire che il sistema possa soddisfare i requisiti di prestazioni e affidabilità. Infine, soddisfare i requisiti di time-to-market può essere impegnativo. Il mercato delle infrastrutture informatiche ad alte prestazioni è in rapida evoluzione e i team di sviluppo SoC devono consegnare rapidamente i propri progetti per stare al passo con la concorrenza.

Arrivare al successo del silicio di primo passaggio

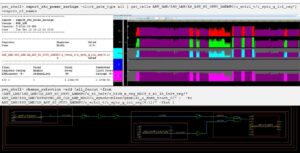

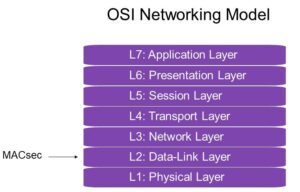

Superare le sfide sopra menzionate richiede un approccio globale. Uno dei componenti critici delle soluzioni ad alte prestazioni e a bassa latenza è Ethernet PHY IP. L'IP Ethernet PHY è responsabile dell'interfaccia del livello fisico tra il SoC e la rete Ethernet. L'IP deve supportare le interfacce Ethernet ad alta velocità, incluse 10G, 25G, 40G, 50G, 100G, 200G, 400G e 800G, e fornire bassa latenza e basso consumo energetico. Inoltre, l'IP deve supportare vari standard, tra cui IEEE 802.3 ed Ethernet Alliance. Un altro componente importante è la suite di progettazione EDA. La suite di progettazione EDA deve fornire una soluzione completa per la progettazione e la verifica del SoC, inclusa l'ottimizzazione della potenza, l'analisi delle prestazioni, l'ottimizzazione dell'area e l'analisi della resa. Nella misura in cui, la suite di progettazione EDA include funzionalità avanzate, come l’intelligenza artificiale (AI) e l’apprendimento automatico (ML), il meglio per una maggiore produttività e un time-to-market ridotto.

Synopsys accelera il successo del silicio di primo passaggio

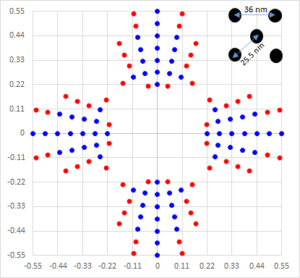

Synopsys offre soluzioni che affrontano le sfide uniche dello sviluppo di SoC per il mercato delle infrastrutture informatiche ad alte prestazioni. L'azienda fornisce una soluzione IP completa che include uno studio di fattibilità del routing, linee guida per i substrati di packaging, modelli di integrità del segnale e dell'alimentazione e un'analisi approfondita della diafonia. Ciò è fondamentale per affrontare le sfide relative all'integrità del segnale e dell'alimentazione affrontate durante lo sviluppo di un SoC DSP ottico. L'IP PHY Ethernet 112G di Synopsys offre bassa latenza, lunghezze di portata flessibili e maturità sulla tecnologia di processo a 5 nm, rendendolo una soluzione ideale per data center iperscalabili, reti, intelligenza artificiale, moduli ottici e SoC switch Ethernet. Inoltre, Synopsys offre una suite di progettazione EDA che fornisce risultati di alta qualità con potenza, prestazioni, area e rendimento ottimizzati. La EDA Design Suite basata sull'intelligenza artificiale di Synopsys fornisce soluzioni per migliorare le prestazioni del sistema e accelerare il time-to-market, rendendola una componente essenziale di una soluzione di successo per il mercato delle infrastrutture informatiche ad alte prestazioni.

Sommario

Synopsys fornisce soluzioni ad alte prestazioni e a bassa latenza che accelerano lo sviluppo di switch Ethernet avanzati e SoC di rete. Per saperne di più sulle soluzioni IP complete di Synopsys, sulla loro suite di progettazione EDA completa e sulla suite EDA potenziata dall'intelligenza artificiale, visita le pagine seguenti.

Le soluzioni IP complete di Synopsys

La suite EDA completa di Synopsys

Suite di progettazione EDA basata sull'intelligenza artificiale di Synopsys

Leggi anche:

Sistemi multi-die: la più grande interruzione dell'informatica da anni

Alimentare la crescente fame di larghezza di banda con Ethernet ad alta velocità

Condividi questo post tramite:

- Distribuzione di contenuti basati su SEO e PR. Ricevi amplificazione oggi.

- Platoblockchain. Web3 Metaverse Intelligence. Conoscenza amplificata. Accedi qui.

- Coniare il futuro con Adryenn Ashley. Accedi qui.

- Fonte: https://semiwiki.com/ip/327703-synopsys-accelerates-first-pass-silicon-success-for-banias-labs-networking-soc/

- :ha

- :È

- a

- Chi siamo

- sopra

- accelerare

- accelera

- aggiunta

- aggiuntivo

- Inoltre

- indirizzo

- Avanzate

- vantaggi

- avanti

- AI

- alleanza

- anche

- an

- .

- ed

- Un altro

- applicazioni

- approccio

- SONO

- RISERVATA

- in giro

- artificiale

- intelligenza artificiale

- Intelligenza artificiale (AI)

- AS

- At

- Larghezza di banda

- BE

- Meglio

- fra

- Maggiore

- Blocchi

- Incremento

- Materiale

- attento

- centro

- sfide

- impegnativo

- Venire

- Comunicazione

- Comunicazioni

- azienda

- concorrenza

- complessità

- componente

- componenti

- globale

- informatica

- consumo

- creare

- critico

- costume

- ciclo

- dati

- Banca dati

- consegnare

- fornisce un monitoraggio

- Design

- progettato

- progettazione

- disegni

- sviluppato

- in via di sviluppo

- Mercato

- sviluppa

- Rottura

- Presto

- efficiente

- emergenti del mondo

- enable

- migliorata

- garantire

- essential

- evoluzione

- di fronte

- FAST

- Caratteristiche

- Infine

- Nome

- flessibile

- i seguenti

- Nel

- da

- ulteriormente

- Crescita

- linee guida

- Alte prestazioni

- alta qualità

- HTML

- HTTPS

- fame

- ideale

- IEEE

- Immagine

- Impact

- imperativo

- importante

- in

- inclusi

- Compreso

- è aumentato

- industria

- standard di settore

- Infrastruttura

- integrazione

- interezza

- Intelligence

- Interfaccia

- interfacce

- IP

- sicurezza

- IT

- SUO

- Labs

- Latenza

- strato

- IMPARARE

- apprendimento

- Basso

- macchina

- machine learning

- make

- Fare

- Rappresentanza

- maturità

- max-width

- Soddisfare

- incontro

- Memorie

- menzionato

- ML

- modelli

- modulo

- Scopri di più

- multiplo

- Bisogno

- Rete

- internazionale

- prossima generazione

- of

- Offerte

- on

- ONE

- operazione

- ottimizzazione

- ottimizzati

- Altro

- proprio

- imballaggio

- passare

- performance

- Fisico

- Platone

- Platone Data Intelligence

- PlatoneDati

- Post

- energia

- processi

- lavorazione

- Processore

- della produttività

- fornire

- fornisce

- rapidamente

- rapidamente

- raggiungere

- Leggi

- tempo reale

- Ridotto

- Basic

- problemi di

- richiedere

- Requisiti

- richiede

- responsabile

- Risultati

- Rischio

- semiconduttore

- Signal

- Silicio

- soluzione

- Soluzioni

- specializzata

- standard

- soggiorno

- Studio

- il successo

- di successo

- tale

- suite

- supporto

- Interruttore

- sistema

- SISTEMI DI TRATTAMENTO

- Target

- le squadre

- Tecnologia

- di

- che

- Il

- loro

- Li

- termico

- Strumenti Bowman per analizzare le seguenti finiture:

- di

- questo

- a

- pure

- trasferimenti

- Tipi di

- tipicamente

- unico

- uso

- convalida

- vario

- verifica

- via

- Visita

- quale

- con

- dare la precedenza

- Trasferimento da aeroporto a Sharm

- zefiro