Il mese scorso si è svolto l'annuale International Electron Devices Meeting (IEDM). Una delle presentazioni del corso breve è stata quella di Matthew Metz di Intel intitolata Nuovi sistemi di materiali per la continuazione della legge di Moore. In sostanza si trattava di uno sguardo ad alcune delle possibilità per ciò che accadrà dopo che il silicio avrà esaurito le sue forze.

![]()

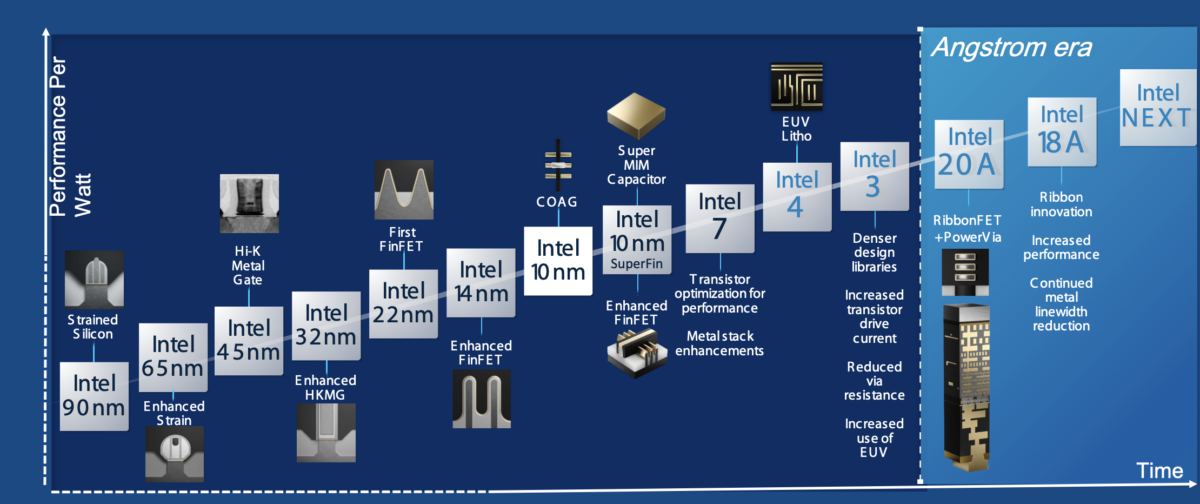

Matthew ha iniziato analizzando il modo in cui il transistor ha cambiato il mondo e, in particolare, le innovazioni dei materiali che hanno guidato la roadmap dei processi di Intel nel corso dei decenni. A 90 nm avevamo il silicio deformato, seguito dal gate metallico HiK. Intel è stata la prima a commercializzare FinFET (anche se allora lo chiamava TriGate). All'Intel 4 è stata introdotta per la prima volta la litografia EUV.

![]()

Come probabilmente saprai, Intel sta sviluppando la tecnologia di 5 processi in 4 anni, il che è ovviamente aggressivo, ma a quanto pare è ancora tutto sulla buona strada. Intel 20A sarà il primo processo con gate-all-around (GAA) che Intel chiama RibbonFET. Intel ha anche una roadmap aggressiva per il packaging avanzato, ma la tralascerò poiché il focus del discorso era cosa metteremo sui wafer in futuro, non come li metteremo insieme.

![]()

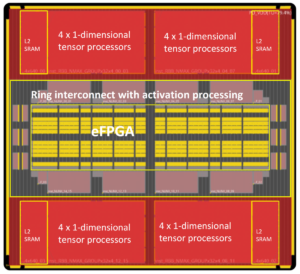

Intel non è la sola a optare per il gate-all-around. Negli ultimi due anni, in occasione di conferenze come IEDM, tutti i principali produttori e organizzazioni di ricerca hanno pubblicato alcune versioni dei risultati globali del nanosheet gate. Vedere le sezioni trasversali sopra.

La prossima grande innovazione pianificata è FET o CFET complementare, con n-transistor rispetto a p-transistor. In effetti questo era quasi il tema dell'IEDM di quest'anno con molte persone che annunciavano varie innovazioni nella produzione di CFET per ottenere un ridimensionamento dell'area da 1.5X a 2X.

![]()

Un'altra innovazione che Intel sta perseguendo (insieme a tutti gli altri) è la rete di distribuzione dell'energia sul retro (backside PDN) insieme a ciò che Intel chiama PowerVia. Queste tecnologie consentono di separare segnali e potenza e di non interferire più tra loro come è avvenuto storicamente, quando tutta l'interconnessione era sul lato anteriore (beh, l'unico lato fino a poco tempo fa).

La sfida più grande è il muro di potere. È molto difficile ottenere più di 100 W per centimetro quadrato di raffreddamento. Ci sono varie possibilità su come migliorare le cose:

- Miglioramenti MOSFET convenzionali

- Nanonastri di silicio-germanio (SiGe) filtrati

- Nanonastri di Ge o InGaAs

- FET a tunnel

- FET Dirac (grafene e 2D)

- Capacità negativa NCFET

- Elaborazione in memoria con FerroTunnel Junction o FerroFET

![]()

Ci sono molte attrazioni nel realizzare materiali 2D invece di attenersi al 3D. Ma ci sono grandi sfide nel trovare buoni materiali. Sono sicuro che avrete sentito parlare di nanotubi di carbonio (CNT), ma nonostante l'attrattiva non vi è stato alcun reale progresso nella sfida di produrli in modo affidabile negli ultimi dieci anni. Il grafene è 2D ma non ha alcun gap di banda, rendendo la costruzione degli interruttori una sfida. Il fosforene è volatile alle alte temperature, rendendo impossibile la produzione di un transistor completo.

![]()

La soluzione più interessante sembra essere lo sviluppo di dichalcogenuri di metalli di transizione o TMD. Confesso che era la prima volta che ne sentivo parlare, almeno sotto questo nome. È uno degli approcci più promettenti che utilizzano materiali 2D. I TMD sono un singolo monostrato che offre un buon controllo del gate, quindi una potenza inferiore. Hanno una mobilità migliore rispetto al silicio, quindi buone prestazioni. Inoltre, un ampio gap di banda limita il tunneling source-drain.

Matthew è entrato in molti dettagli sulle sfide e le promesse della produzione di transistor TMD a 2 strati, in particolare sulla crescita dei transistor 2D a strato singolo, e su come contattarli. Per i componenti del transistor n i materiali più attraenti sembrano essere l'antimonio (Sb) e il bismuto (Bi). Per il transistor p, rutenio (Ru).

![]()

L'ultima sezione riguardava la riduzione dei requisiti energetici e la commutazione avanzata, in particolare i dispositivi spin-orbitali magnetoelettrici (MESO). La commutazione può essere effettuata a circa 0.1 V con la corrispondente riduzione di potenza.

La conclusione di Matthew è che il lavoro in corso presso Intel con TMD mostra la promessa di un continuo scaling CMOS, e i dispositivi MESO hanno molte promesse per una drastica riduzione della potenza. Ma questa è una ricerca relativamente iniziale e c’è ancora molto lavoro da fare per rendere una di queste tecnologie una realtà pratica.

Leggi anche:

La grande corsa del 2024 è TSMC N2 e Intel 18A

Buzz IEDM: Intel presenta in anteprima la nuova innovazione di scalabilità verticale dei transistor

Intel inaugura una nuova era di packaging avanzato con substrati in vetro

Condividi questo post tramite:

- Distribuzione di contenuti basati su SEO e PR. Ricevi amplificazione oggi.

- PlatoData.Network Generativo verticale Ai. Potenzia te stesso. Accedi qui.

- PlatoAiStream. Intelligenza Web3. Conoscenza amplificata. Accedi qui.

- PlatoneESG. Carbonio, Tecnologia pulita, Energia, Ambiente, Solare, Gestione dei rifiuti. Accedi qui.

- Platone Salute. Intelligence sulle biotecnologie e sulle sperimentazioni cliniche. Accedi qui.

- Fonte: https://semiwiki.com/semiconductor-manufacturers/340336-iedm-what-comes-after-silicon/

- :ha

- :È

- :non

- 01

- 1

- 14

- 15%

- 2024

- 27

- 29

- 2D

- Materiali 2D

- 30

- 3d

- 40

- 50

- 53

- 58

- 8

- a

- WRI

- sopra

- avanzare

- Avanzate

- Dopo shavasana, sedersi in silenzio; saluti;

- aggressivo

- Tutti

- consentire

- quasi

- da solo

- lungo

- anche

- Sebbene il

- am

- an

- ed

- annunciando

- annuale

- approcci

- SONO

- RISERVATA

- in giro

- AS

- At

- attrazione

- attrazioni

- attraente

- precedente

- BE

- stato

- Meglio

- Big

- Maggiore

- Costruzione

- ma

- by

- detto

- Bandi

- Materiale

- carbonio

- nanotubi di carbonio

- Custodie

- Challenge

- sfide

- cambiato

- viene

- comparativamente

- complementare

- completamento di una

- Calcolare

- conclusione

- conferenze

- contatti

- continua

- Corrispondente

- Coppia

- corso

- Cross

- decenni

- consegna

- Nonostante

- dettaglio

- Mercato

- dispositivi

- difficile

- fare

- fatto

- giù

- spinto

- ogni

- Presto

- o

- altro

- epoca

- essenza

- tutti

- fatto

- FET

- ricerca

- Nome

- prima volta

- Focus

- seguito

- Nel

- anteriore

- futuro

- gate

- ottenere

- Dare

- vetro.

- andando

- buono

- Grafene

- Crescita

- ha avuto

- Avere

- sentito

- Alta

- storicamente

- Come

- Tutorial

- HTTPS

- i

- impossibile

- competenze

- in

- Innovazione

- innovazioni

- invece

- Intel

- interferire

- Internazionale

- ai miglioramenti

- introdotto

- IT

- Sapere

- grandi

- Cognome

- Legge

- strato

- meno

- piace

- Limitato

- più a lungo

- Guarda

- lotto

- inferiore

- maggiore

- make

- Fare

- Produttori

- consigliato per la

- molti

- molte persone

- Rappresentanza

- Materiale

- matthew

- max-width

- incontro

- metallo

- mobilità

- Mese

- Scopri di più

- maggior parte

- Nome

- Rete

- New

- GENERAZIONE

- no

- of

- on

- ONE

- esclusivamente

- or

- organizzazioni

- Altro

- su

- ancora

- proprio

- imballaggio

- particolare

- Persone

- per

- performance

- posto

- previsto

- Platone

- Platone Data Intelligence

- PlatoneDati

- possibilità

- Post

- energia

- Pratico

- presentazioni

- Anteprime

- probabilmente

- processi

- i processi

- PROMETTIAMO

- promette

- promettente

- pubblicato

- perseguendo

- metti

- abbastanza

- Gara

- Leggi

- di rose

- Realtà

- recentemente

- riduzione

- Requisiti

- riparazioni

- Risultati

- tabella di marcia

- RU

- corre

- scala

- allo

- Sezione

- sezioni

- vedere

- sembrare

- sembra

- Corti

- tiro

- Spettacoli

- lato

- Segnali

- Silicio

- da

- singolo

- So

- soluzione

- alcuni

- quadrato

- iniziato

- Steam

- adesivo

- Ancora

- sicuro

- SISTEMI DI TRATTAMENTO

- Parlare

- Tecnologie

- Tecnologia

- Sviluppo tecnologico

- carnagione

- di

- che

- Il

- Il futuro

- il mondo

- Li

- tema

- poi

- Là.

- Strumenti Bowman per analizzare le seguenti finiture:

- di

- cose

- questo

- tempo

- titolato

- a

- insieme

- ha preso

- pista

- transizione

- tsmc

- per

- fino a quando

- uscieri

- utilizzando

- vario

- versione

- verticale

- molto

- via

- volatile

- Muro

- Prima

- we

- WELL

- è andato

- Che

- quando

- quale

- volere

- con

- Lavora

- mondo

- anni

- Tu

- zefiro