Fuzzing adalah verifikasi perangkat lunak, sedangkan pengacakan adalah verifikasi perangkat keras. Dapatkah pendekatan fuzzing meningkatkan pengujian keamanan perangkat keras? Paul Cunningham (GM, Verifikasi di Cadence), Raúl Camposano (Silicon Catalyst, pengusaha, mantan CTO Synopsys) dan saya melanjutkan seri ide penelitian kami. Seperti biasa, masukan diterima.

Inovasi

Pilihan bulan ini adalah HyperFuzzing untuk Validasi Keamanan SoC. Penulis mempresentasikan makalah ini di ICCAD 2020. Mereka berasal dari IIT Kanpur.

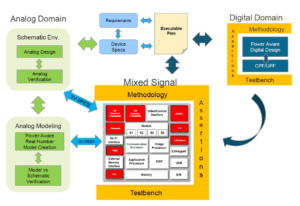

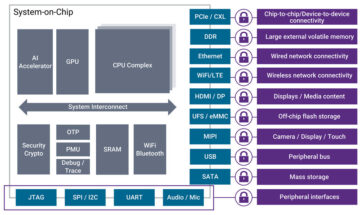

Ini adalah pendekatan fuzzing yang menarik, diadaptasi secara khusus untuk desain SoC modern. Itu membangun properti hiper memeriksa simulasi dinamis. Alasan hiper-properti ini tentang perilaku berakhir kumpulan jejak, sebuah pendekatan yang cocok untuk pemeriksaan keamanan. Penulis menawarkan contoh pemeriksaan aliran informasi (katakanlah data istimewa tidak boleh bocor dari A ke B) dan pemeriksaan non-interferensi (tindakan permusuhan tidak boleh mengganggu aliran komputasi). Keamanan kemudian diperiksa dengan membandingkan kumpulan jejak simulasi dengan dan tanpa gangguan.

Merusak pendekatan ini dapat memodelkan berbagai jenis kerentanan terhadap sumber yang tidak tepercaya. Dengan mengacak instruksi firmware, menulis instruksi dari komponen ke NoC, atau membalik bit dalam memori. Penulis juga mengusulkan beberapa metrik liputan baru. Ini dirancang untuk memandu iterasi untuk melakukan gangguan pada kasus yang paling dipengaruhi oleh proses gangguan sebelumnya.

Testcase mereka adalah SoC yang kecil namun representatif (detailnya ada di GitHub) menjalankan pengujian firmware terhadap blok kriptografi, memeriksa non-interferensi dan kerentanan lainnya. Mereka juga menjalankan boot aman dengan pemeriksaan blok data. Mereka menemukan beberapa pelanggaran keamanan di blok kripto, kecuali blok tersebut menyertakan perlindungan ECC.

pandangan Paulus

Verifikasi keamanan adalah topik yang sangat penting, dan ada banyak pekerjaan yang sedang dilakukan baik di dunia akademis maupun industri. Makalah ini dengan baik menyatukan cakupan berbasis mutasi acak dengan “properti hiper” pada serangkaian jejak simulasi untuk menciptakan solusi inovatif yang terukur dan efektif dalam menunjukkan kelemahan keamanan.

Beberapa properti keamanan hanya dapat didefinisikan secara formal melalui serangkaian jejak simulasi. Misalnya, “non-interferensi” berarti bahwa penyerang tidak dapat mengganggu komputasi tertentu yang dilindungi dalam suatu desain. Untuk mendemonstrasikan interferensi, Anda perlu membandingkan dua jejak yang identik dalam stimulus masukan, kecuali adanya beberapa tindakan penyerang dalam satu jejak. Jika perhitungan yang dilindungi pada jejak yang diserang berbeda dengan perhitungan pada jejak emas, maka telah terjadi gangguan.

Penulis menciptakan bahasa khusus mereka sendiri untuk pernyataan atas beberapa jejak dan menggunakannya untuk merumuskan properti keamanan untuk non-interferensi dan kerahasiaan. Mereka membangun alur kustom untuk mengutak-atik simulasi secara acak dan memeriksa properti keamanannya antara simulasi yang dirusak dan tidak dirusak. Algoritme gangguan acak mereka juga memiliki heuristik pembelajaran berbasis cakupan yang elegan untuk memandunya menemukan kelemahan keamanan dengan lebih efisien.

Gagasan tentang pernyataan atas beberapa simulasi sangatlah kuat. Saya ingin tahu apakah mungkin untuk memperluas SystemVerilog dengan bersih untuk mendukung pernyataan semacam ini. Hal ini dapat membuka pintu bagi beberapa perluasan asli yang menarik untuk simulasi komersial dan alat formal. Kemungkinan lainnya adalah memperluas Standar Stimulus Portabel (PSS) yang baru dengan menyertakan pernyataan yang mencakup beberapa pengujian yang dihasilkan.

Makalah ini adalah bacaan yang mudah dan menyenangkan, meskipun saya menginginkan lebih banyak rincian tentang hasilnya. Para penulis mengklaim bahwa solusi mereka menemukan celah keamanan pada testcase SoC open-source mereka, namun tidak ada rincian tentang apa itu lubang tersebut atau bagaimana pendekatan mereka dibandingkan dengan pendekatan lain dalam literatur yang dapat diterapkan untuk menemukan lubang yang sama.

Pandangan Raul

Saya akan melihat hal ini terlebih dahulu dari sudut kematangan teknologi. Saya menyukai ide secara umum, pendekatan yang sangat menarik untuk menilai keamanan dalam sebuah desain. Meskipun demikian, setiap desain mengharuskan desainer untuk memberikan pengujian awal, gangguan, dan spesifikasi keamanan dalam bahasa pernyataan baru. Bagi saya, hal ini membatasi pendekatan terhadap ranah akademis saat ini. Cocok untuk disertasi dan makalah, belum mendekati sesuatu yang dapat digunakan untuk aplikasi komersial.

Saya akan angkat topi sebagai investor untuk tantangan kedua. Keamanan adalah topik penting, tidak diragukan lagi. Namun di luar beberapa domain yang sudah kita ketahui – misalnya dirgantara, pertahanan, sistem pembayaran, dan pemroses/server. Ini masih bukan masalah nyata bagi sebagian besar OEM dan pembuat komponen. Mereka bersedia mencentang kotak jika diharapkan secara umum. Namun hanya jika dampaknya terhadap biaya atau waktu pemasaran kecil. Karena pelanggan mereka umumnya tidak akan membayar lebih untuk keamanan. Hal ini membuat keamanan sebagian besar pasar masih bergantung pada IP turnkey, seperti akar kepercayaan perangkat keras, dan aplikasi yang mudah digunakan. Solusi yang dikemas dalam salah satu cara ini akan dapat diinvestasikan, jika tidak maka tidak akan terlalu banyak.

Pandangan saya

Paul dan Raúl membahas sebagian besar saran saya. Saya menyukai gagasan Paul untuk memperluas SVA, setidaknya untuk mendorong eksperimen dengan properti hiper. Hal ini harus membuka kelas tes baru yang menarik, yang pada akhirnya mengarah pada metode verifikasi gabungan yang baru.

Bagikan postingan ini melalui: Sumber: https://semiwiki.com/eda/299391-fuzzing-to-validate-soc-security-innovation-in-verification/

- 100

- 2020

- 2021

- Aerospace

- algoritma

- Aplikasi

- aplikasi

- sekitar

- penulis

- Bit

- Kotak

- membangun

- Irama

- kasus

- menantang

- memeriksa

- Cek

- komersial

- komponen

- terus

- kripto

- CTO

- pelanggan

- data

- Pertahanan

- Mendesain

- domain

- Efektif

- Pengusaha

- ekstensi

- menemukan

- Pertama

- kekurangan

- aliran

- Umum

- GM

- besar

- membimbing

- Perangkat keras

- di sini

- Seterpercayaapakah Olymp Trade? Kesimpulan

- HTTPS

- ide

- IEEE

- gambar

- Dampak

- industri

- informasi

- Innovation

- investor

- IP

- IT

- melompat

- bahasa

- terkemuka

- bocor

- pengetahuan

- literatur

- Pasar

- pasar

- Metrik

- model

- menawarkan

- Buka

- Lainnya

- kertas

- Membayar

- pembayaran

- Sistem Pembayaran

- mengusulkan

- perlindungan

- Acak

- penelitian

- Hasil

- Run

- berjalan

- keamanan

- pengujian keamanan

- benih

- Seri

- set

- simulasi

- kecil

- So

- Perangkat lunak

- Solusi

- rangsangan

- mendukung

- sistem

- Teknologi

- pengujian

- tes

- waktu

- Kepercayaan

- Verifikasi

- Kerentanan

- Kerja