Struktur benjolan baru sedang dikembangkan untuk memungkinkan kepadatan interkoneksi yang lebih tinggi dalam kemasan flip-chip, namun struktur tersebut rumit, mahal, dan semakin sulit untuk diproduksi.

Untuk produk dengan jumlah pin yang tinggi, flip-chip [1] paket telah lama menjadi pilihan populer karena memanfaatkan seluruh area die untuk interkoneksi. Teknologi ini telah digunakan sejak tahun 1970-an, dimulai dengan C4 (koneksi chip runtuh terkontrol) IBM, tetapi teknologi ini mulai digunakan secara luas pada tahun 1990-an.

Sejak itu, teknologi bump telah berevolusi untuk menangani peningkatan kepadatan koneksi daya dan sinyal yang dibutuhkan oleh memori, komputasi kinerja tinggi, dan perangkat komputasi seluler. Memenuhi permintaan tersebut memerlukan teknologi interkoneksi baru yang memungkinkan bump pitch yang lebih kecil, yang saat ini sedang dalam tahap produksi.

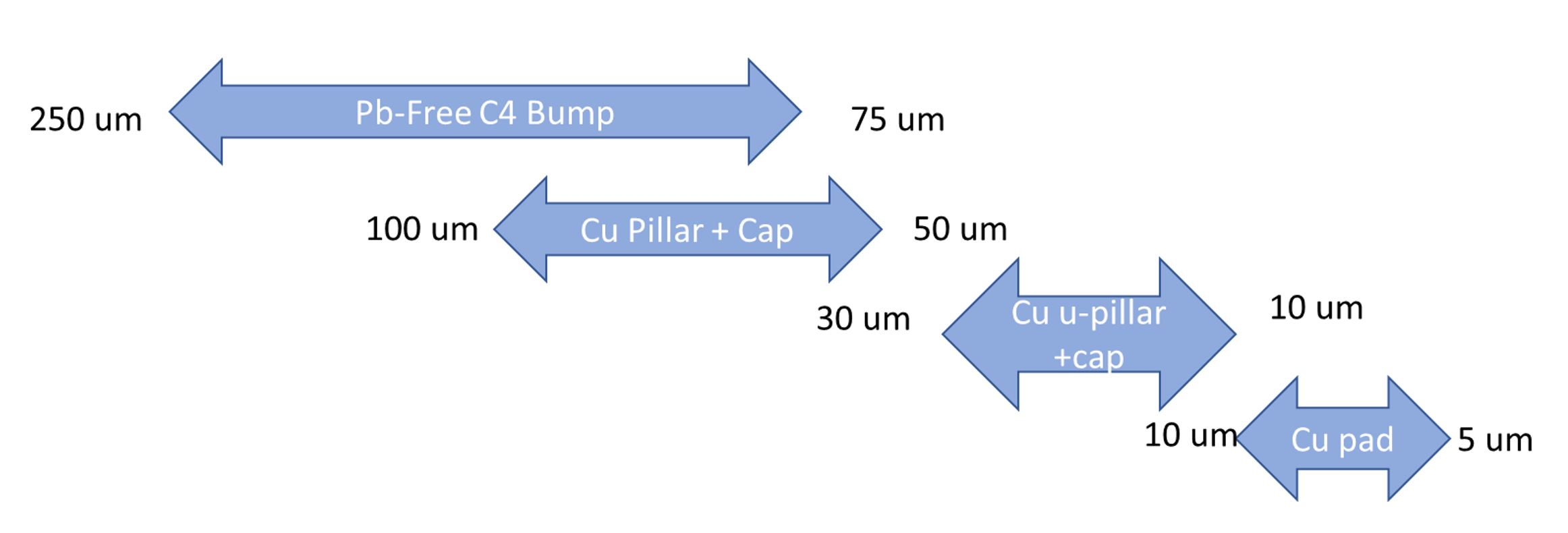

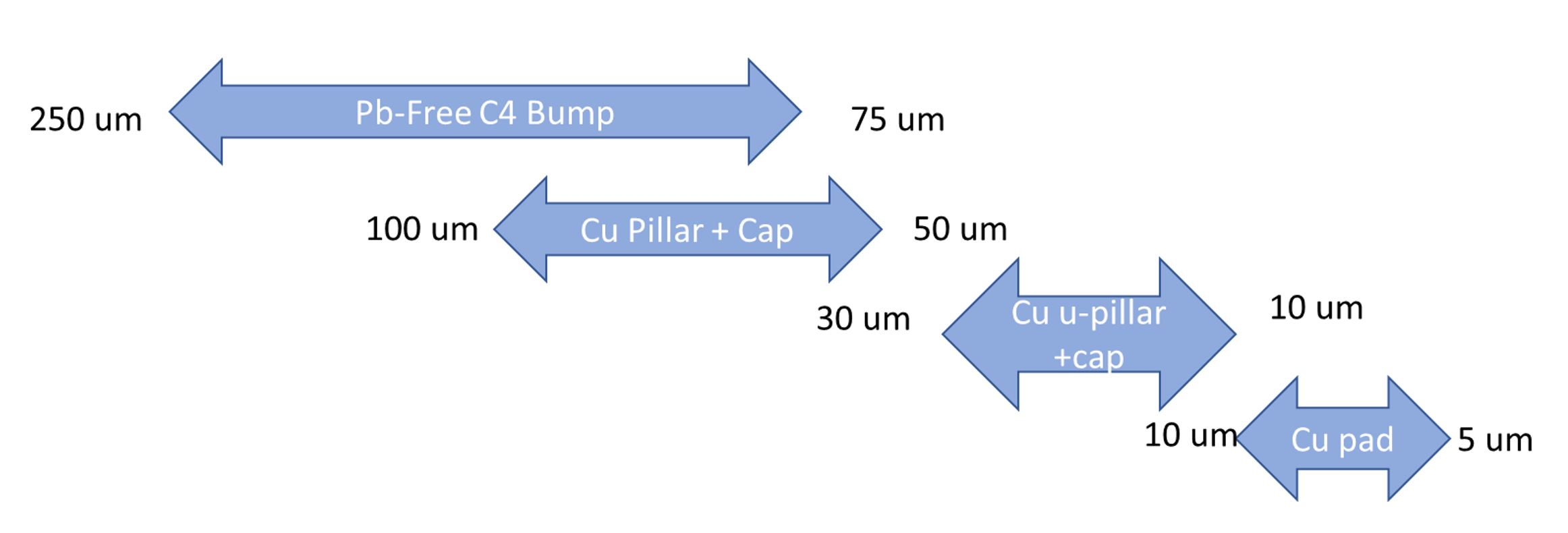

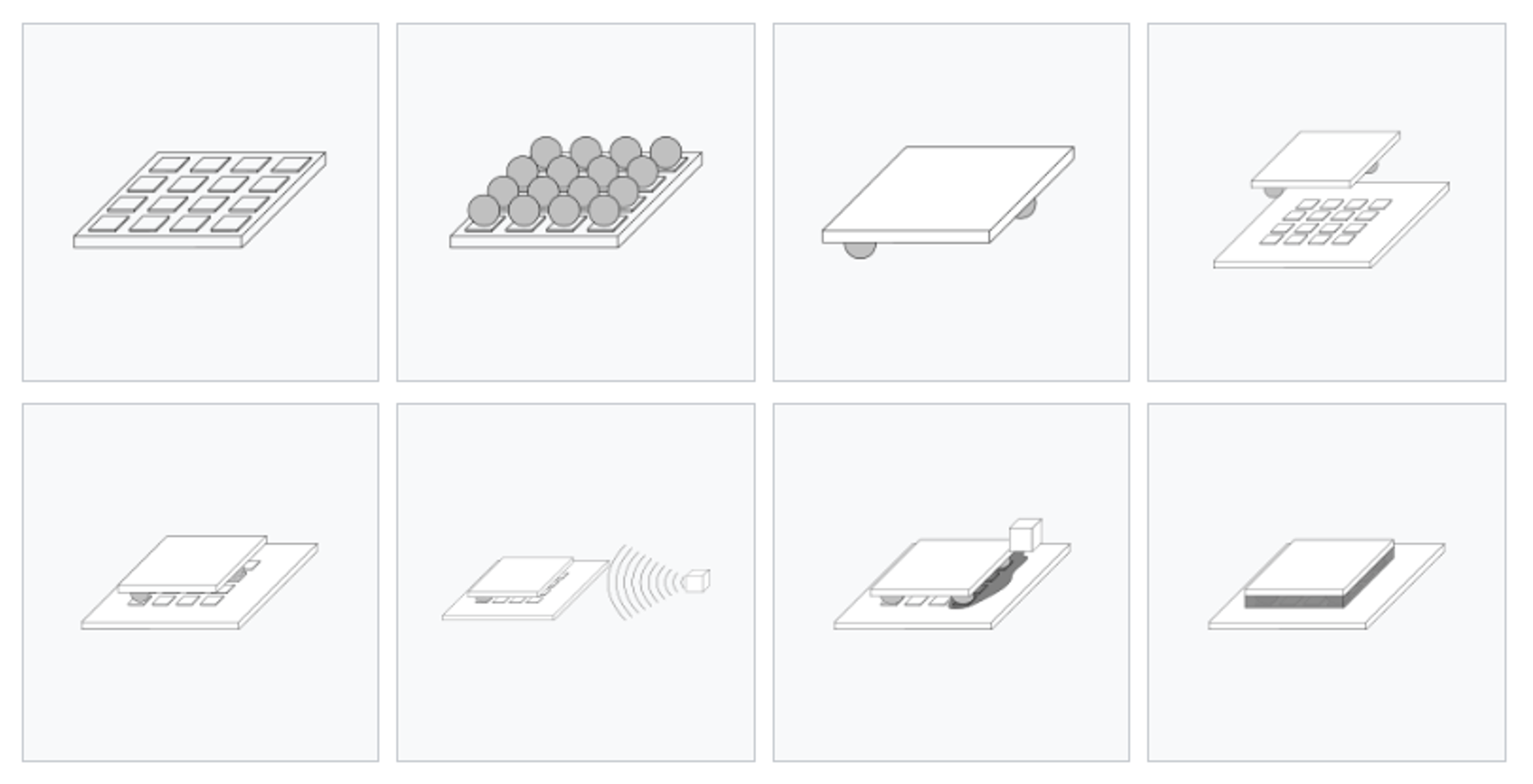

Dilihat dari waktu ke waktu, peta jalan untuk interkoneksi flip-chip berkembang dari benjolan bebas timbal ke pilar tembaga, dan kemudian ke benjolan mikro tembaga. Ukuran pitch terus menyusut, yang pada gilirannya menciptakan tantangan manufaktur untuk bumping dan bonding.

Gambar 1: Rentang nada teknologi flip-chip. Sumber: A. Meixner/Teknik Semikonduktor

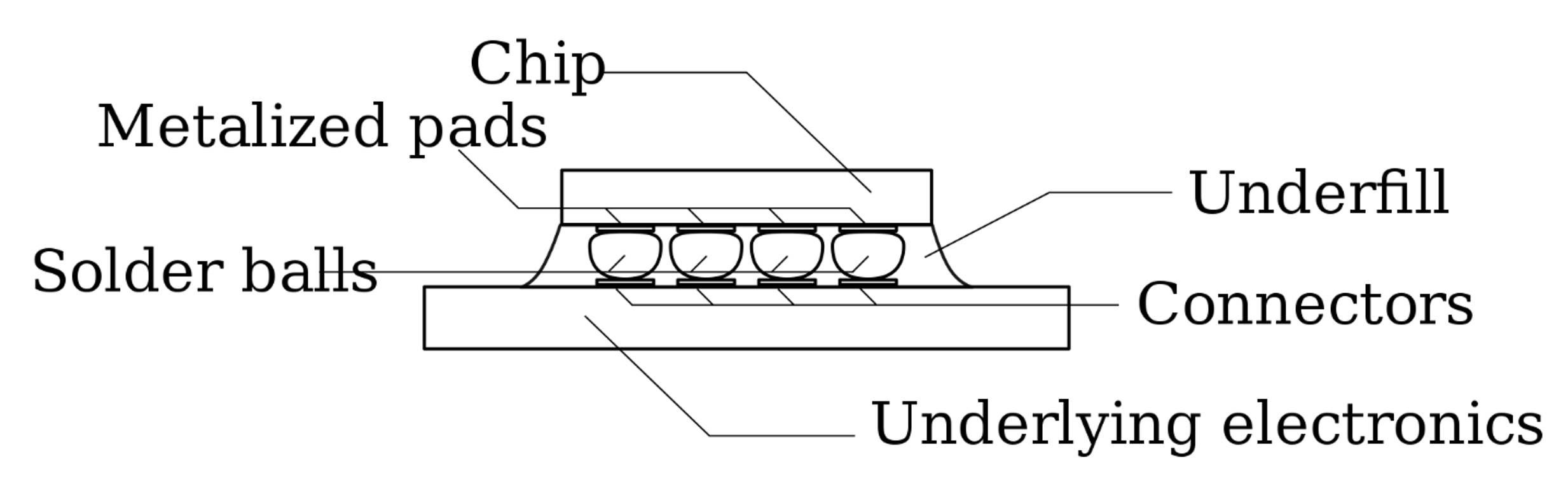

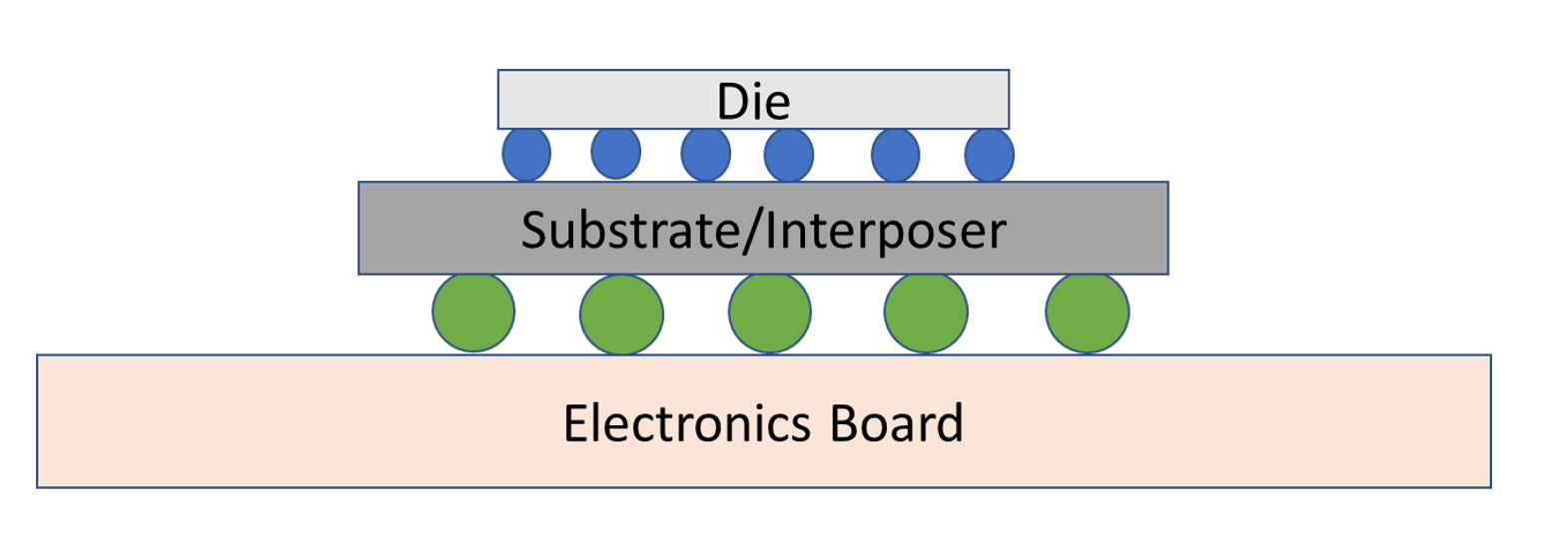

Gambar 2: Komponen flip-chip. Sumber: Wikipedia

“Di arena flip-chip – pitch 250 mikron ke bawah – awalnya merupakan benjolan timah, dan salah satu langkah besarnya adalah bebas timah. Namun ketika Anda mulai mencapai 100 mikron atau lebih rendah, Anda mulai melihat lebih banyak pilar tembaga, meskipun ada tumpang tindih karena kita melihat pilar tembaga hingga 250 mikron,” kata Jeff Schaefer, insinyur proses senior di Industri Promex. “Dengan pitch 250 mikron, kita melihat ukuran benjolan atau diameter pilar tembaga sebesar 130 mikron. Setelah kita mencapai jarak 100 mikron, diameternya menjadi 80 mikron. Yang terkecil yang pernah saya lihat adalah pitch 62.5 mikron dengan pilar 40 mikron. Saya berharap untuk segera melihat nada 50 mikron.”

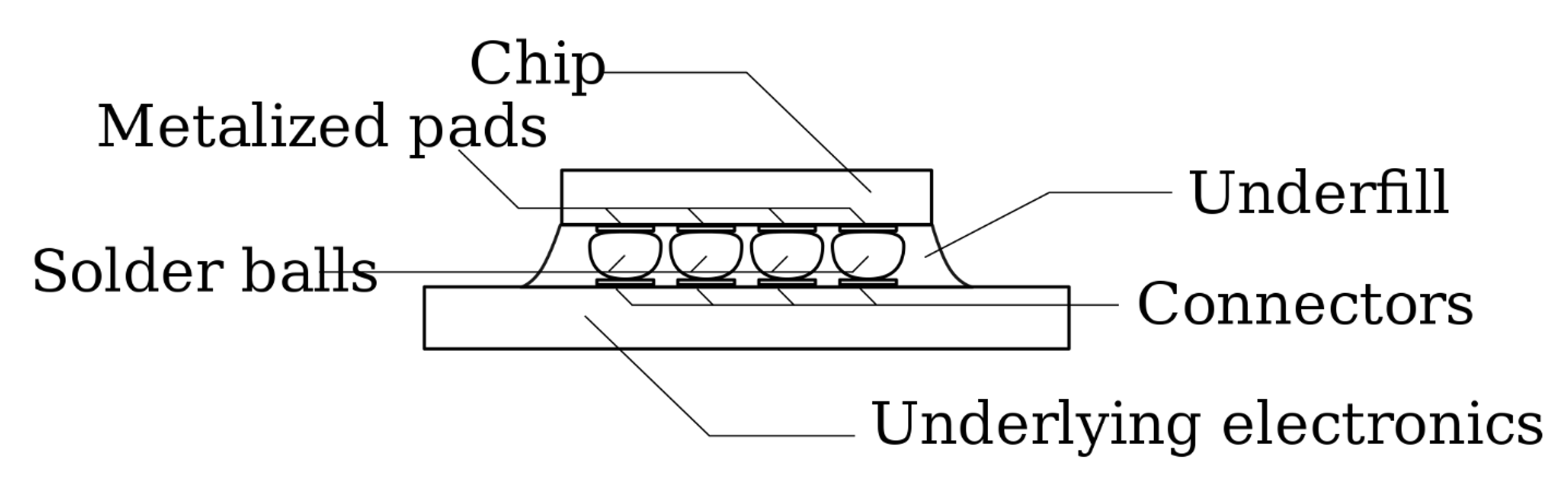

Proses dasar flip-chip dimulai setelah fabrikasi sirkuit, ketika bantalan logam dibuat pada permukaan cetakan untuk dihubungkan ke I/Os. Berikutnya adalah wafer bumping, di mana bola solder diendapkan pada setiap bantalan. Wafer kemudian dipotong dadu, dan cetakan tersebut dibalik dan diposisikan sehingga bola solder sejajar dengan bantalan media. Bola solder kemudian dicairkan / dialirkan kembali, biasanya menggunakan udara panas, dan cetakan yang dipasang diisi dengan perekat isolasi listrik, biasanya menggunakan aksi kapiler. [1]

Gambar 3: Proses pembuatan flip-chip. Sumber: Wikipedia

Pindah ke pilar tembaga atau microbump memerlukan litografi untuk membuat struktur ini.

“Pilar tembaga umumnya digunakan dengan pitch di bawah 130µm, karena alih-alih menjadi tonjolan solder melingkar, pilar tembaga sebagian besar berupa tiang Cu dengan solder di atasnya,” kata Doug Scott, wakil presiden senior pengemasan tingkat wafer di Teknologi Amkor. “Hal ini memungkinkan tonjolan pilar tembaga ditempatkan berdekatan tanpa risiko solder tersambung selama reflow perakitan — umumnya, ~40 µm Cu + ~25 µm.”

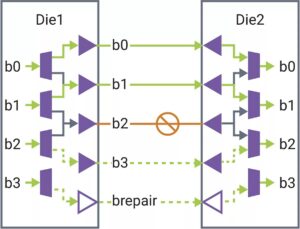

Ada variasi tema juga. “Microbump, yang merupakan istilah umum yang digunakan ketika Anda memiliki interkoneksi antara silikon-ke-silikon, sedikit berbeda karena CTE (koefisien ekspansi termal) secara umum sama,” kata Mark Gerber, direktur senior untuk teknik/pemasaran teknis pada Grup ASE. “Beberapa aturan desain umum yang digunakan untuk pilar tembaga adalah sama, namun topografi permukaan datar dan sambungan tegangan rendah memungkinkan fleksibilitas penggunaan lapisan bawah. Hal ini juga dapat mendorong bump pitch individu. Saat ini, pitch full-array bump 35µm dimungkinkan, karena pertimbangan perutean yang disebutkan sebelumnya, untuk perutean tingkat wafer atau tingkat luar biasa yang digunakan.”

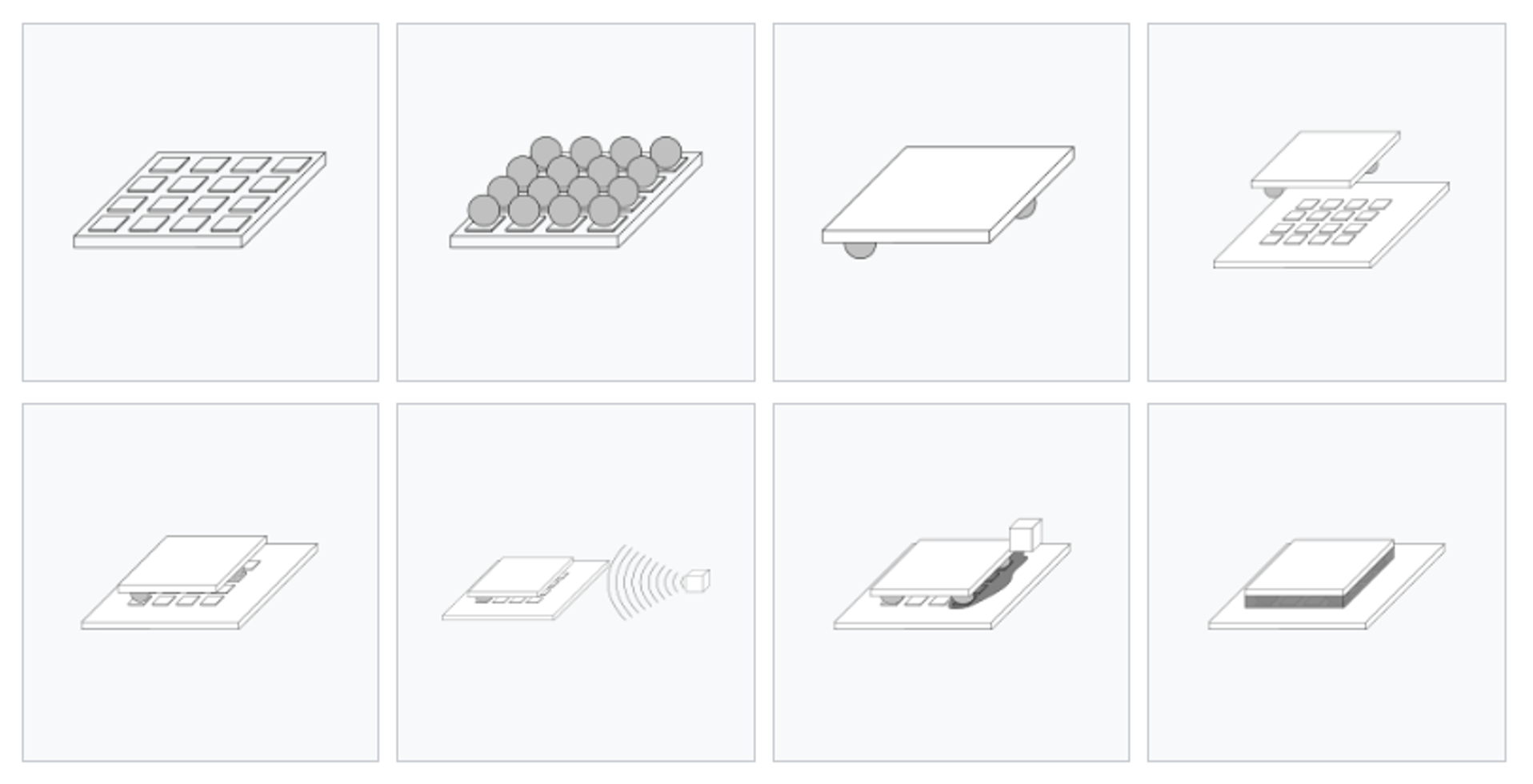

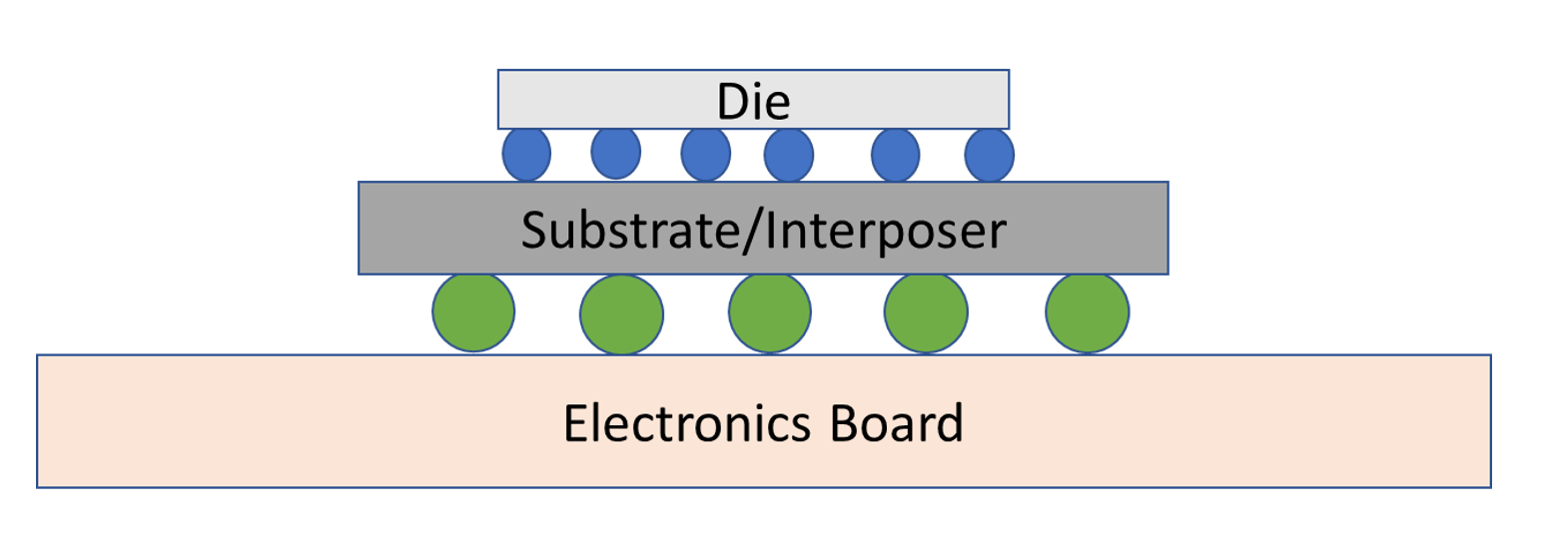

Peta Jalan Integrasi Heterogen [2] menjelaskan semua aspek pengemasan, termasuk interkoneksi mati-ke-substrat mulai dari ikatan kawat hingga via silikon tembus. Dengan paket flip-chip, interkoneksi die-to-substrat, area redistribusi substrat, dan interkoneksi substrat-ke-board, semuanya berperan dalam batasan produksi.

Gambar 4: Diagram konseptual kemasan flip-chip. Sumber: A. Meixner/Teknik Semikonduktor

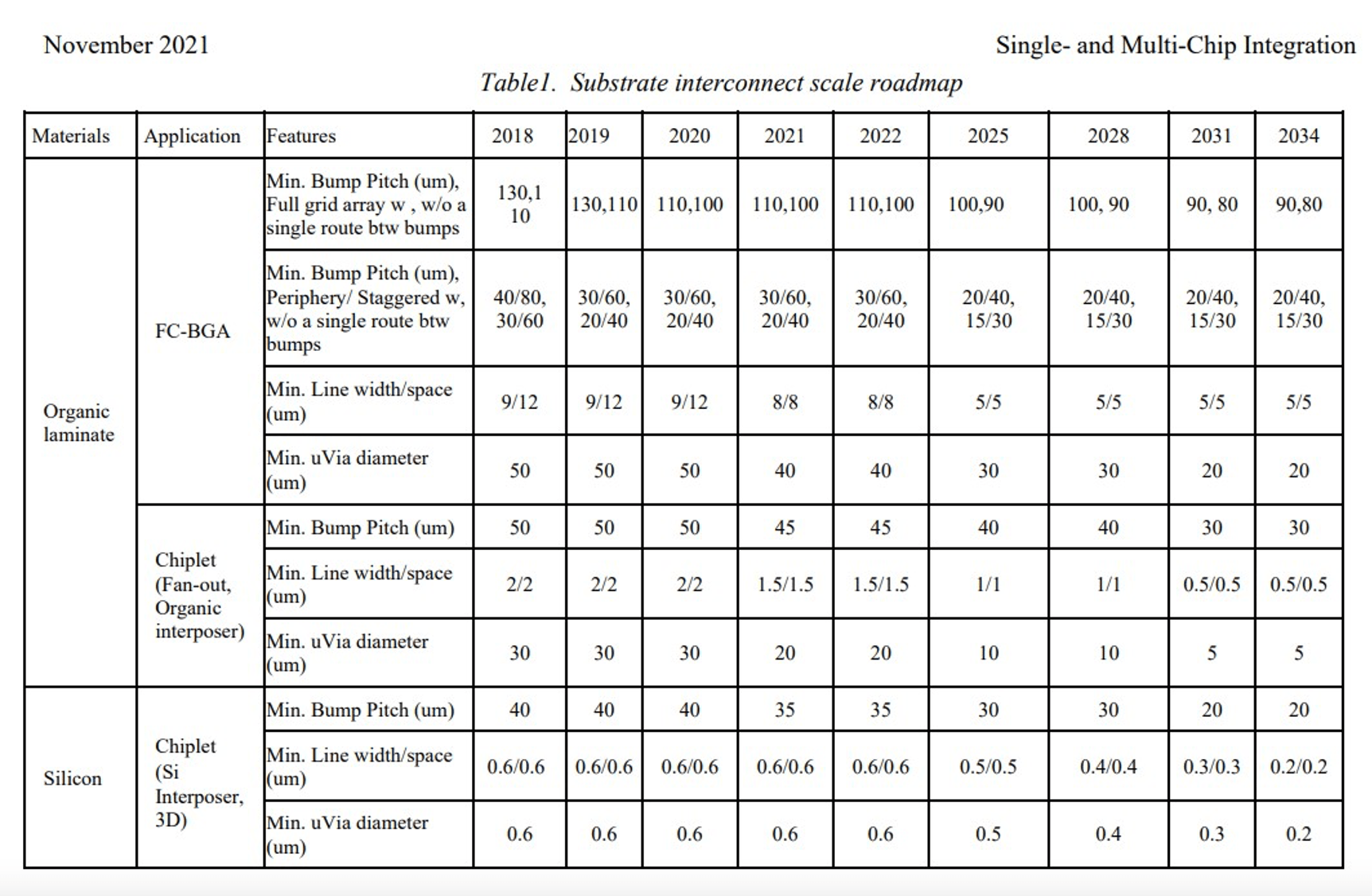

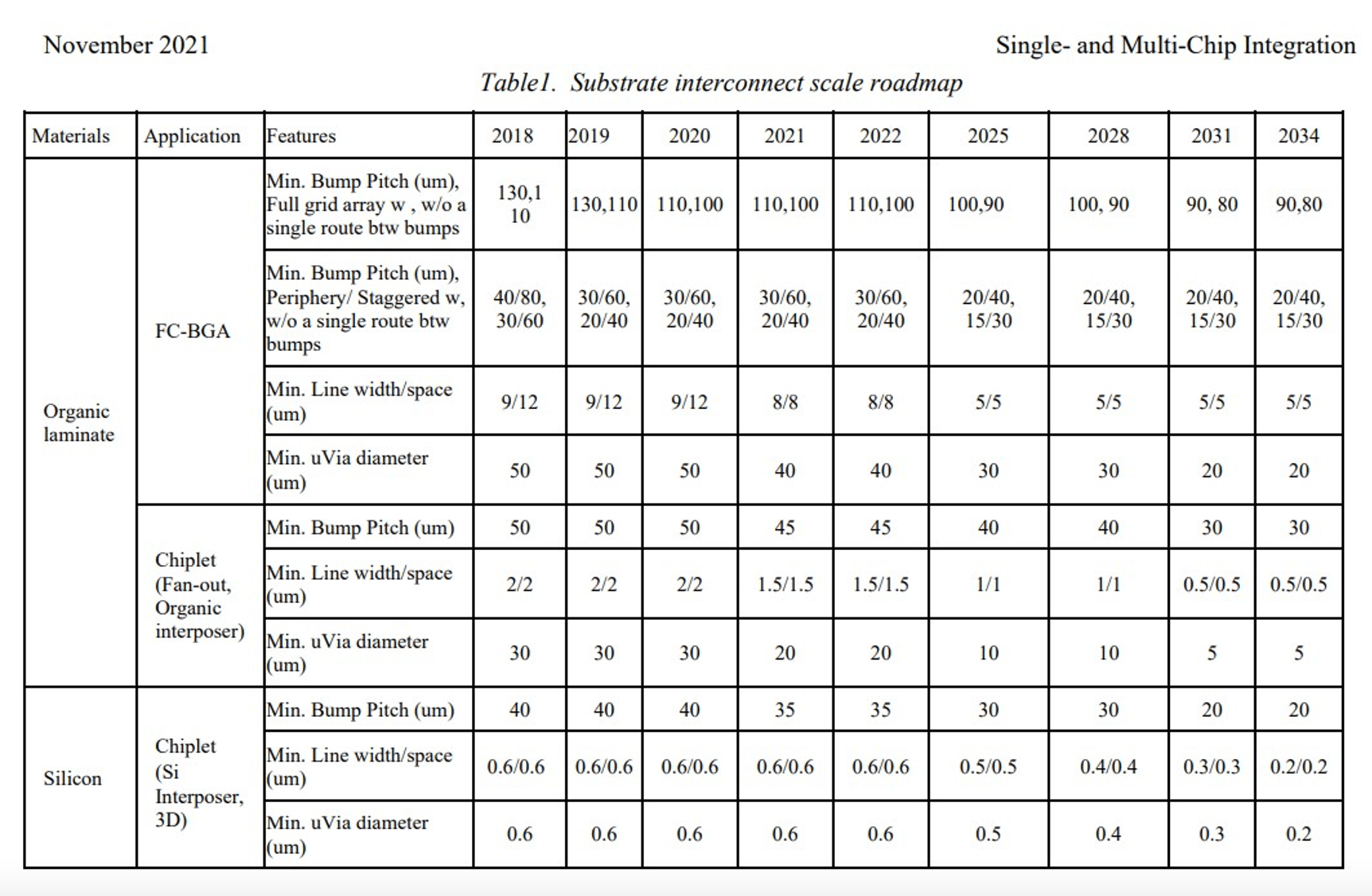

Bab 8 dari Peta Jalan Integrasi Heterogen [3] mendokumentasikan lanskap teknologi pengemasan saat ini dan yang diproyeksikan. Pitch minimum dari setiap teknologi interkoneksi flip-chip ditampilkan pada Tabel 1 subbagian 8.7 (halaman 41).

![Bab 8 dari Peta Jalan Integrasi Heterogen [3] mendokumentasikan lanskap teknologi pengemasan saat ini dan yang diproyeksikan. Pitch minimum dari setiap teknologi interkoneksi flip-chip ditampilkan pada Tabel 1 subbagian 8.7 (halaman 41).](https://platoaistream.com/wp-content/uploads/2023/05/challenges-grow-for-creating-smaller-bumps-for-flip-chips-7.png)

![Bab 8 dari Peta Jalan Integrasi Heterogen [3] mendokumentasikan lanskap teknologi pengemasan saat ini dan yang diproyeksikan. Pitch minimum dari setiap teknologi interkoneksi flip-chip ditampilkan pada Tabel 1 subbagian 8.7 (halaman 41).](https://platoaistream.com/wp-content/uploads/2023/05/challenges-grow-for-creating-smaller-bumps-for-flip-chips-8.png)

Tabel terkait untuk interkoneksi media (bagian yang menghubungkan paket ke papan) terdapat di subbagian 8.8 (halaman 43).

Dengan setiap perubahan dalam teknologi interkoneksi, muncullah proses baru dan batasannya, yang mendorong inovasi, manajemen hasil, dan pemeriksaan cacat.

Menabrak batas teknologi

Teknologi menabrak diukur berdasarkan nada, ukuran, tinggi, dan sifat listrik dan mekanik. Pertimbangan termal bervariasi tergantung pada ketidakcocokan material CTE. Warpage merupakan kekhawatiran terhadap cetakan dan wafer yang lebih besar, yang diperburuk dengan penggilingan balik wafer sebelum cetakan dipasang.

“Ada sejumlah faktor pendorong batasan pitch untuk setiap jenis interkoneksi,” kata Gerber dari ASE. “Dimulai dengan interkoneksi chip bump flip solder tradisional, kemampuan pitch ditentukan oleh ketinggian keruntuhan untuk underfill, capture pad pitch untuk routing jejak, capture pad pitch untuk risiko pendek bump-to-bump dan beberapa sensitivitas terkait pitch lainnya. Ketinggian tonjolan yang telah dipasang sebelumnya memiliki ketinggian yang ditentukan, tetapi sebagaimana IBM mendefinisikan istilah C4 — Koneksi Chip Runtuh Terkendali — diameter tonjolan solder dan ukuran bantalan penangkap akan menentukan 'runtuh atau tinggi akhir' interkoneksi. Ini adalah faktor pembatas nada utama dalam penggunaan tonjolan solder yang terkait dengan nada.”

Ketinggian benjolan ditentukan oleh desain, tetapi juga pilihan pemrosesan.

“Untuk tonjolan solder berlapis standar dan tonjolan pilar tembaga, ketinggian tonjolan sebelum perakitan umumnya sekitar 70µm hingga 75 µm, dengan tinggi tonjolan yang runtuh setelah perakitan ~50 µm untuk memberikan ruang x,y,z untuk aliran underfill di antara tonjolan. Microbumps akan memiliki ketinggian benjolan yang jauh lebih rendah dan melibatkan lebih sedikit pelapisan solder. Secara khusus, microbumps bisa berukuran kurang dari 10µm dengan pengurangan ketinggian Cu dan solder tergantung pada kebutuhan pitch dan ujung,” kata Scott dari Amkor. “Bonjolan solder berlapis standar umumnya digunakan pada pitch yang berkisar antara 130µm hingga 250µm. Di bawah 130µm, tidak terdapat cukup ruang xy di antara tonjolan saat memulai dengan ketinggian tonjolan sebelum perakitan 70µm.”

Membuat pilar tembaga memerlukan lebih banyak langkah pemrosesan daripada tonjolan solder.

“Saat kita bertransisi ke dunia die-to-die, teknologinya berbeda karena sekarang Anda berurusan dengan wafer dan planeritnya sangat bagus dibandingkan die-to-substrat. Pertama anda buat pilar tembaganya, pada wafer awal yang akan mendapat solder atau pilar tembaga tersebut terlebih dahulu ada under bump metal (UBM). Ini adalah penutup kecil pada bukaan yang masuk ke dalam silikon. Kemudian kita membuat inti tembaga dari situ dan memasang tutup timah di atasnya. Jadi wafer penerimanya, sepertinya ada bantalan UBM di sana dan biasanya ada lapisan jenis emas nikel sehingga bagus dan murni,” jelas Schaefer dari Promex Industries. Jadi, alih-alih memiliki sedikit lekukan seperti substrat laminasi, Anda memiliki sedikit ekstrusi. Kami telah menemukan bahwa kami dapat menyoldernya dalam keadaan basah tanpa 'solder pada bantalan'. Begitulah cara mereka dirancang dan dibangun. Ini hampir berfungsi seperti solder dan bantalan karena berbentuk kubah kecil, bukan mencoba masuk ke dalam lubang.”

Langkah-langkah fotolitografi yang diperlukan untuk pembentukan pilar Cu memiliki batasan serta aturan desain substrat.

“Untuk pilar tembaga, yang terdiri dari tiang tembaga dan tutup solder di ujungnya, tinggi tiang tembaga dapat ditentukan dengan batasan satu atau lebih ketebalan lapisan tahan foto dan saat Anda mengurangi nada, rasio aspek dari tiang tersebut cu post height to pitch menjadi batasan seiring dengan material tahan foto dan kemampuan alat pencitraan,” kata Gerber. “Batasan sekunder untuk interkoneksi pilar tembaga adalah aturan desain media yang digunakan. Untuk nada halus >110um, 2 metode utama digunakan - BOT (Bond on Trace) atau ET - Jejak Tertanam, di mana tutup solder pilar tembaga ditempatkan di atas jejak, bukan pada bantalan penangkap tradisional. Ukuran dan bentuk pilar tembaga, termasuk batasan-batasan di atas, dapat memberikan batasan pada kemampuan dan peta jalan untuk terus mengecilkan lapangan. Banyak dari keterbatasan ini disebabkan oleh kemampuan untuk mengarahkan jejak di antara pilar pada sisi substrat. Dengan tersedianya teknologi baru, seperti RDL tingkat wafer, peta jalan interkoneksi akan didorong lebih jauh, namun masih dengan batasan seputar rasio tinggi/aspek untuk proses manufaktur seperti underfill.”

Yang lain setuju bahwa proses pengisian yang kurang memiliki tantangan. “Saat Anda mendapatkan nada yang lebih halus, gundukan yang lebih kecil akan menjadi lebih pendek. Sekarang semakin sulit untuk menemukan lapisan bawah untuk masuk ke bawahnya. Pengisian bagian bawah secara historis dirancang untuk mencapai jarak kurang dari 5 mil, dan sekarang turun menjadi 3 mil, yaitu 75 mikron,” kata Schaefer. “Sekarang kita mulai melihat kesenjangan 60 dan 25 mikron. Saya yakin orang-orang sedang mengerjakan bagian bawah yang baru. Tapi ada banyak hal yang harus dikerjakan. Pertama, semakin halus partikulatnya, partikel tersebut menjadi lebih seperti lumpur, sehingga semakin sulit mengalir. Ini adalah hambatan yang perlu dihilangkan.”

Mengelola hasil

Seiring dengan semakin kecilnya teknologi bumping, langkah pemrosesan tambahan — misalnya, litografi untuk membuat pilar tembaga — membuka peluang baru bagi detektor hasil. Agar proses pengikatan berhasil, partikulat, kontaminan permukaan, dan pelepasan tonjolan solder merupakan masalah dalam hasil. Hal ini memerlukan pengendalian proses, metrologi, dan inspeksi.

Pengendalian kontaminasi secara alami diperlukan. “OSAT Tingkat 1 berinvestasi untuk mengurangi tingkat sumber kontaminasi pabrik, dan oleh karena itu mengurangi persentase kecacatan,” kata Scott dari Amkor. “Pitch tidak berkontribusi terhadap cacat. Tingkat kecacatan serupa terjadi terlepas dari nadanya.”

Namun pitch menambahkan beberapa tantangan tersendiri. “Saat pitch menjadi lebih kecil dan ukuran benjolan berkurang, pengelolaan kontaminasi partikel menjadi sangat penting. Untuk jenis interkoneksi lain seperti ikatan hibrid, yang jarak pitchnya dikurangi hingga di bawah 30µm dan kontak permukaan-ke-permukaan penting, lingkungan ruang bersih berbasis wafer sangat penting untuk hasil panen,” kata Gerber dari ASE.

Mempersiapkan proses underfill juga tidak boleh dianggap remeh.

“Umumnya dengan laminasi, Anda akan melakukan underfilling setelah Anda melakukan flip chip,” kata Schaefer dari Promex. “Kami menentukan di mana kami akan menempatkannya dan bagaimana melakukan reflow. Kami membersihkannya untuk mengeluarkan material fluks di bawah celah antara cetakan dan substrat. Lalu kita akan mengisinya dengan epoksi yang mengalir. Ini dirancang untuk membasahi dan tidak meninggalkan rongga dan hal-hal semacam itu. Namun ada tantangan saat kita mencapai nada yang lebih baik. Benjolan menjadi lebih pendek, dan semakin pendek, jarak antara chip dan media semakin kecil, sehingga lebih sulit untuk dibersihkan. Bayangkan menempelkan dua slide kaca untuk mencoba menghilangkan kotoran di antara keduanya.”

Kebutuhan metrologi dan inspeksi

Untuk mengelola kontrol proses dan hasil, alat metrologi dan inspeksi memainkan peran penting. “Ada alat yang tersedia di pasar yang dapat membantu memberikan panduan mengenai integritas interkoneksi, selain analisis cross-sectional dalam proses yang digunakan pada saat penyiapan dan pada interval produksi yang ditentukan,” kata Gerber dari ASE.

Proses bumping dan proses bonding masing-masing memiliki karakteristik khusus yang perlu dipantau. Untuk gundukan, metrologi berfokus pada diameter, tinggi, dan ko-planaritas. Pitch yang lebih kecil memerlukan kontrol yang lebih ketat terhadap diameter benjolan dan kontrol ketinggian. Demikian pula, dengan menyusutnya tinggi benjolan, jendela koplanaritas menjadi lebih kecil. Biasanya, variasi 10% diperbolehkan. Misalnya, tinggi tonjolan 30µm menghasilkan variasi yang diizinkan sebesar ±3µm. Melebihi jumlah ini akan menyebabkan ikatan tidak berhasil atau buruk.

“Pengikatan biasanya dilakukan dengan oven reflow massal,” kata Mike Kelly, wakil presiden paket lanjutan dan integrasi teknologi di Amkor. “Karakterisasi awal dari proses reflow dilakukan dengan menggunakan shadow-moire untuk mengukur lengkungan selama reflow, dan pemetaan suhu oven untuk memastikan kontrol suhu yang konsisten pada bagian flip-chip itu sendiri. Selama penyetelan, pengangkatan cetakan mekanis dan inspeksi dilakukan untuk memastikan pembasahan solder yang baik. Selain itu, fluks biasanya diaplikasikan dengan 'dip flux', dimana die bump 'dicelupkan' ke dalam reservoir flux yang tipis dan dikontrol dengan ketat. Inspeksi visual terhadap barang-barang ini dilakukan berdasarkan pengambilan sampel.”

Peningkatan otomatisasi inspeksi visual mengurangi ketergantungan pada operator untuk melihat gambar dan mengambil keputusan. Peningkatan eksponensial dalam koneksi bump adalah salah satu pendorongnya. Perubahan pada proses pengikatan memberikan hal lain. Proses reflow solder yang selaras adalah teknologi yang matang. Dengan ikatan kompresi termal yang biasa digunakan dalam pengemasan tingkat lanjut, terdapat mekanisme keandalan yang lulus pengujian kelistrikan. Hal ini, pada gilirannya, mendorong penggunaan pemeriksaan sinar-X dan alat metrologi untuk melihat benjolan setelah pengikatan.

“Untuk pengemasan dengan kompleksitas rendah, fasilitas dapat ditangani oleh operator dan pemeriksaan secara manual. Untuk bagian dengan 100 benjolan, metode ini bisa dilakukan. Pada 1,000 gundukan, itu pasti merupakan ketegangan. Sekali suatu bagian mempunyai 10,000 benjolan, tidak ada peluang. Kami telah melampaui titik ini dan kami perlu beralih ke metode berikutnya,” kata Frank Chen, direktur aplikasi dan manajemen produk di Pengguna. “Kualitas dan kompleksitas berjalan seiring, karena ketika Anda mencoba membuat sesuatu yang lebih kompleks, hasil Anda akan terpengaruh dan akan diperlukan beberapa peralatan baru. Dan perkakas berarti alat proses dan alat metrologi, sehingga keduanya perlu dikembangkan secara paralel. Dari penelitian kami sendiri, kami melihat bahwa begitu Anda mencapai 1,000 tantangan tersebut, saat itulah Anda perlu mulai berpikir 'Teknik manual saya tidak cukup dan saya memerlukan sesuatu yang baru.'”

Berbagai alat inspeksi dan metrologi tersedia untuk mendukung pembuatan paket.

“Ada beberapa metode yang dapat atau harus digunakan untuk mencapai pengendalian proses. Pertama, inspeksi 2D tradisional (AOI) untuk inspeksi cacat permukaan 100% per aliran proses (yaitu, IQC, OQA, foto, pembersihan, pelapisan, dll.) Berikutnya, metrologi 2D (AOI) dapat digunakan untuk mengontrol ukuran benjolan dan ukuran diameter kontrol. Selain itu, metrologi 3D (AOI) dapat digunakan untuk perolehan informasi metrologi ketinggian benjolan/keplanaritas pengambilan sampel (hal ini biasanya dilakukan dengan teknologi berbasis triangulasi laser),” kata Nathan Peng, manajer pemasaran produk di Ke Inovasi. “Selanjutnya, metrologi 3D dapat menargetkan karakteristik ketinggian benjolan individu, yang biasanya dikumpulkan dengan teknologi interferometer cahaya putih. Selain itu, terdapat metode yang memungkinkan pendeteksian residu organik pada bagian atas yang dapat menyebabkan kegagalan sambungan dari bagian atas ke bantalan.”

Kesimpulan

Produk-produk yang menuntut jumlah interkoneksi yang lebih tinggi terus mendorong peta jalan interkoneksi. Setiap teknologi flip-chip memiliki batasan produksi yang melibatkan sifat material, penyusutan ukuran yang menantang teknologi underfill, dan peningkatan penggunaan litografi untuk menciptakan struktur interkoneksi. Setiap perubahan dalam proses pengikatan menghasilkan peningkatan metrologi dan langkah-langkah inspeksi untuk memenuhi tujuan hasil dan kualitas.

Referensi

- https://en.wikipedia.org/wiki/Flip_chip

- https://eps.ieee.org/technology/heterogeneous-integration-roadmap/2021-edition.html

- HIR Bab 8 Integrasi Chip Tunggal dan Multi Chip, https://eps.ieee.org/images/files/HIR_2021/ch08_smcfinal.pdf

Cerita Terkait:

Co-Planaritas dan Inkonsistensi Menyebabkan Masalah Hasil dan Keandalan

Tantangan pengemasan yang canggih semakin meningkat seiring dengan menyusutnya ukuran chip dan kemasan; peralatan yang berbeda, teknologi mendapatkan daya tarik.

Keandalan Bump Ditantang Oleh Cacat Laten

Solusi otomatis sedang dikerjakan, tetapi akan membutuhkan waktu untuk berkembang.

Perubahan Besar Di Depan Dalam Penghantaran Daya, Material, Dan Interkoneksi

Bagaimana manufaktur dan pengemasan akan berubah dalam beberapa dekade mendatang.

- Konten Bertenaga SEO & Distribusi PR. Dapatkan Amplifikasi Hari Ini.

- PlatoAiStream. Kecerdasan Data Web3. Pengetahuan Diperkuat. Akses Di Sini.

- Mencetak Masa Depan bersama Adryenn Ashley. Akses Di Sini.

- Beli dan Jual Saham di Perusahaan PRE-IPO dengan PREIPO®. Akses Di Sini.

- Sumber: https://semiengineering.com/challenges-grow-for-creating-smaller-bumps-for-flip-chips/

- :memiliki

- :adalah

- :bukan

- :Di mana

- $NAIK

- 000

- 1

- 10

- 100

- 250

- 2D

- 3d

- 40

- 7

- 8

- a

- kemampuan

- Sanggup

- atas

- Mencapai

- perolehan

- Tindakan

- tindakan

- sebenarnya

- tambahan

- Tambahan

- Menambahkan

- memajukan

- maju

- Setelah

- di depan

- UDARA

- meluruskan

- Semua

- mengizinkan

- memungkinkan

- sepanjang

- juga

- an

- analisis

- dan

- Lain

- Apa pun

- aplikasi

- terapan

- ADALAH

- DAERAH

- daerah

- sekitar

- AS

- penampilan

- aspek

- Majelis

- At

- melampirkan

- Otomatisasi

- tersedia

- jauh

- kembali

- bola

- dasar

- dasar

- BE

- karena

- menjadi

- menjadi

- sebelum

- makhluk

- di bawah

- antara

- Luar

- Besar

- papan

- ikatan

- Bot

- kedua

- membangun

- dibangun di

- tapi

- by

- datang

- CAN

- topi

- kemampuan

- menangkap

- Menyebabkan

- menantang

- tertantang

- tantangan

- kesempatan

- perubahan

- Perubahan

- Bab

- karakteristik

- chen

- keping

- Keripik

- pilihan

- pilihan

- lebih dekat

- Lihat Lebih Sedikit

- runtuh

- bagaimana

- datang

- Umum

- umum

- dibandingkan

- kompleks

- kompleksitas

- komponen

- komputasi

- konseptual

- Perhatian

- Terhubung

- Menghubungkan

- koneksi

- Koneksi

- menghubungkan

- pertimbangan

- konsisten

- kontak

- kontaminan

- terus

- terus-menerus

- menyumbang

- kontrol

- dikendalikan

- mengendalikan

- kontrol

- Tembaga

- Core

- Sesuai

- bisa

- sepasang

- membuat

- dibuat

- membuat

- kritis

- terbaru

- Sekarang

- data

- berurusan

- dekade

- keputusan

- didefinisikan

- pastinya

- pengiriman

- Permintaan

- kepadatan

- Tergantung

- disimpan

- Mendesain

- dirancang

- Deteksi

- Menentukan

- ditentukan

- mengembangkan

- dikembangkan

- Devices

- Mati

- berbeda

- sulit

- Kepala

- kotoran

- do

- dokumen

- tidak

- dilakukan

- turun

- mendorong

- pengemudi

- driver

- dua

- selama

- e

- E&T

- setiap

- antara

- tertanam

- aktif

- memungkinkan

- akhir

- insinyur

- Teknik

- cukup

- memastikan

- Lingkungan Hidup

- peralatan

- mapan

- dll

- Eter (ETH)

- berkembang

- contoh

- ada

- perluasan

- mengharapkan

- mahal

- menjelaskan

- eksponensial

- fasilitas

- faktor

- pabrik

- Kegagalan

- Ara

- terakhir

- Menemukan

- akhir

- Pertama

- datar

- keluwesan

- Penerjunan

- aliran

- Mengalir

- FLUX

- berfokus

- Untuk

- untuk hasil

- pembentukan

- ditemukan

- dari

- lebih lanjut

- Selanjutnya

- Mendapatkan

- celah

- kesenjangan

- Umum

- umumnya

- mendapatkan

- mendapatkan

- kaca

- Go

- Pergi

- akan

- Gold

- baik

- penggilingan

- Tumbuh

- bimbingan

- menangani

- Sulit

- Memiliki

- memiliki

- tinggi

- ketinggian

- membantu

- High

- kinerja tinggi

- lebih tinggi

- secara historis

- Lubang

- PANAS

- Seterpercayaapakah Olymp Trade? Kesimpulan

- How To

- HTML

- HTTPS

- Hibrida

- i

- IBM

- IEEE

- gambar

- membayangkan

- Pencitraan

- dampak

- penting

- in

- Termasuk

- Meningkatkan

- Pada meningkat

- meningkatkan

- makin

- sendiri-sendiri

- informasi

- mulanya

- Innovation

- sebagai gantinya

- integrasi

- integritas

- interkoneksi

- ke

- Menginvestasikan

- melibatkan

- IT

- item

- NYA

- Diri

- pemandangan

- lebih besar

- laser

- lapisan

- memimpin

- Meninggalkan

- kurang

- Tingkat

- adalah ide yang bagus

- cahaya

- 'like'

- MEMBATASI

- pembatasan

- keterbatasan

- batas

- sedikit

- Panjang

- melihat

- terlihat seperti

- Lot

- Rendah

- Utama

- membuat

- MEMBUAT

- pengelolaan

- manajer

- pelaksana

- panduan

- manual

- pabrik

- banyak

- pemetaan

- tanda

- Pasar

- Marketing

- bahan

- bahan

- dewasa

- max-width

- cara

- mekanis

- mekanisme

- Pelajari

- pertemuan

- Memori

- tersebut

- logam

- metode

- metode

- Metrologi

- mikron

- mikropon

- minimum

- mobil

- dipantau

- lebih

- kebanyakan

- pindah

- bergerak

- banyak

- multi-

- Alam

- Perlu

- dibutuhkan

- kebutuhan

- New

- Teknologi baru

- berikutnya

- bagus

- Nikel

- tidak

- terkenal

- sekarang

- jumlah

- target

- of

- on

- sekali

- ONE

- Buka

- pembukaan

- operator

- operator

- Peluang

- menentang

- or

- organik

- semula

- Lainnya

- kami

- di luar

- lebih

- sendiri

- paket

- paket

- pengemasan

- bantalan

- halaman

- Paralel

- bagian

- partikel

- lulus

- Konsultan Ahli

- Pilar

- Nada

- pitches

- Tempat

- plato

- Kecerdasan Data Plato

- Data Plato

- Bermain

- Titik

- miskin

- Populer

- pilihan populer

- diposisikan

- mungkin

- Pos

- kekuasaan

- presiden

- primer

- Sebelumnya

- proses

- proses

- pengolahan

- Produk

- manajemen Produk

- Produksi

- Produk

- diproyeksikan

- properties

- memberikan

- terdorong

- menempatkan

- kualitas

- mulai

- perbandingan

- mencapai

- benar-benar

- menerima

- menurunkan

- mengurangi

- mengurangi

- Bagaimanapun juga

- terkait

- keandalan

- kepercayaan

- Dihapus

- membutuhkan

- wajib

- membutuhkan

- Hasil

- Risiko

- peta jalan

- peta jalan

- Peran

- Kamar

- Rute

- rute

- aturan

- Tersebut

- sama

- sekunder

- melihat

- melihat

- terlihat

- semikonduktor

- senior

- penyiapan

- beberapa

- Bentuknya

- bergeser

- Pendek

- harus

- sisi

- Sinyal

- Silikon

- mirip

- Demikian pula

- sejak

- tunggal

- Ukuran

- ukuran

- Slides

- sedikit berbeda

- lebih kecil

- So

- Solusi

- beberapa

- sesuatu

- Segera

- sumber

- sumber

- Space

- tertentu

- Secara khusus

- standar

- awal

- Mulai

- Tangga

- pelekatan

- Masih

- cerita

- tekanan

- studi

- sukses

- seperti itu

- mendukung

- Permukaan

- SVG

- tabel

- Mengambil

- target

- Teknologi

- Teknologi

- istilah

- pengujian

- dari

- bahwa

- Grafik

- Pemandangan

- mereka

- Mereka

- tema

- kemudian

- Sana.

- karena itu

- panas

- Ini

- mereka

- hal

- Pikir

- ini

- itu

- meskipun?

- rapat

- waktu

- ujung

- untuk

- hari ini

- bersama

- alat

- alat

- puncak

- jejak

- daya tarik

- tradisional

- mencoba

- MENGHIDUPKAN

- dua

- mengetik

- jenis

- khas

- bawah

- atas

- menggunakan

- bekas

- menggunakan

- biasanya

- Penggunaan

- variasi

- sangat

- Wakil Presiden

- View

- berkemih

- adalah

- we

- BAIK

- ketika

- yang

- putih

- seluruh

- tersebar luas

- Wikipedia

- akan

- dengan

- tanpa

- Kerja

- kerja

- bekerja

- dunia

- X

- x-ray

- Menghasilkan

- hasil panen

- kamu

- Anda

- zephyrnet.dll