Resistivitas tembaga bergantung pada struktur kristal, volume rongga, batas butir, dan ketidaksesuaian antarmuka material, yang menjadi lebih signifikan pada skala yang lebih kecil. Pembentukan kabel tembaga (Cu) secara tradisional dilakukan dengan mengetsa pola parit dalam silikon dioksida berkadar rendah menggunakan proses etsa parit, dan selanjutnya mengisi parit dengan Cu melalui aliran damaskus. Sayangnya, metode ini menghasilkan struktur multi-kristal dengan batas butir dan rongga yang signifikan, sehingga meningkatkan resistansi kawat Cu. Bahan liner TaN yang sangat resistif juga digunakan dalam proses ini untuk mencegah difusi Cu selama proses anil damaskus.

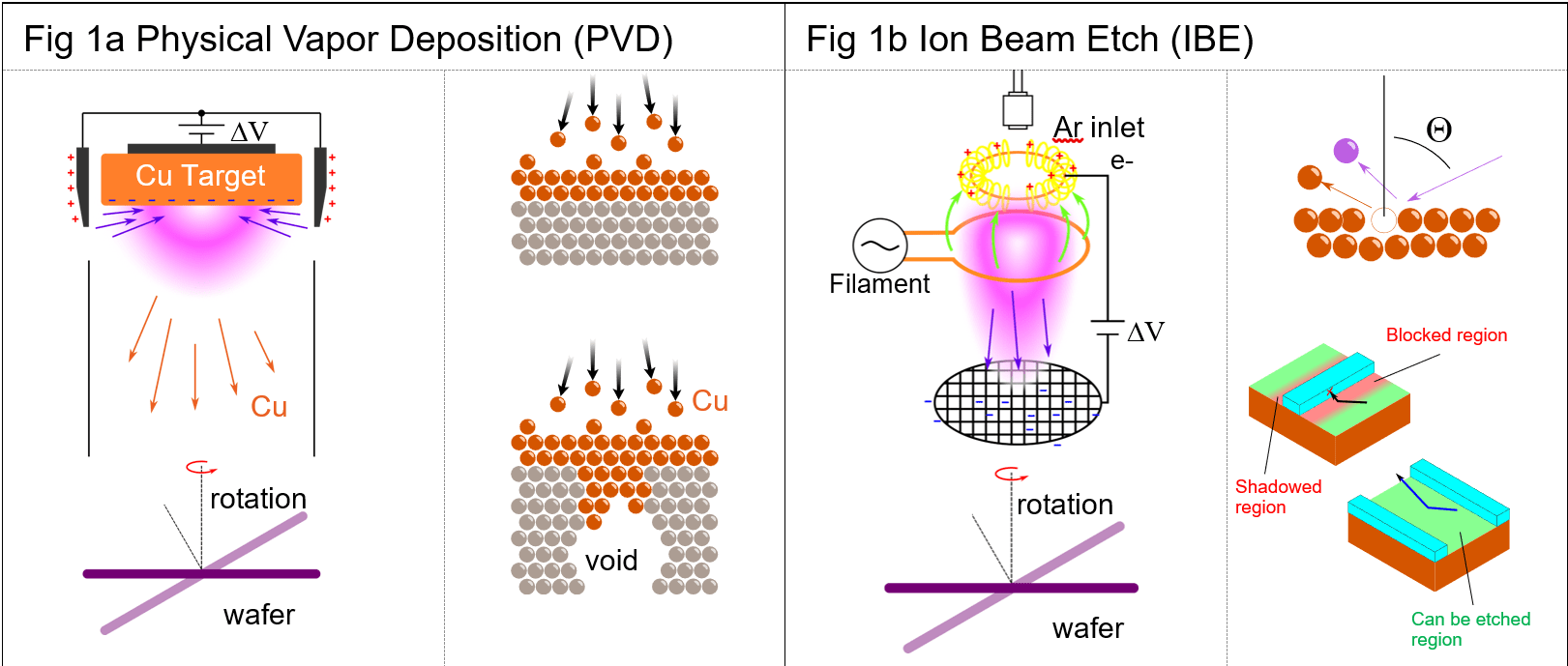

Deposisi uap fisik (PVD) dapat digunakan untuk menyimpan tembaga pada energi kinetik tinggi (antara 10 hingga 100 eV), membentuk struktur kristal tunggal padat dan resistansi rendah. Kelemahan PVD adalah pengendapan PVD memiliki garis pandang yang tersebar dan hanya dapat diendapkan secara seragam pada permukaan datar. Tidak dapat digunakan untuk mengisi lubang atau parit yang dalam (gambar 1a). Untuk membentuk bentuk kawat yang terisolasi, lapisan Cu yang seragam harus diendapkan pada permukaan datar dan kemudian digores secara fisik dengan berkas ion. Cu tidak membentuk senyawa yang mudah menguap dengan gas reaktif, sehingga proses etsa ion reaktif tidak dapat digunakan. Ion Ar yang dipercepat yang dihasilkan selama etsa berkas ion (IBE) dapat menghilangkan Cu jika sudut datangnya sangat tinggi. Sayangnya, area yang dapat digores akan terbatas karena efek bayangan topeng. Gambar 1b menunjukkan daerah (berwarna merah) di mana material tidak dapat tergores ketika masker tegak lurus terhadap berkas ion yang masuk. Kegagalan etsa ini terjadi karena bayangan atau penyumbatan jalur atom yang dikeluarkan. Ketika topeng sejajar dengan jalur ion, semua wilayah yang terbuka kedoknya dapat tergores. Dengan demikian, etsa berkas ion terbatas pada etsa topeng berbentuk garis dengan panjang yang sewenang-wenang.

![]()

Gambar 1: (1a) Deposisi Uap Fisik (PVD); (1b) Etch Berkas Ion (IBE).

Langkah-langkah proses dan proses fabrikasi virtual

Untuk memahami pengaruh deposisi dan etsa pada hambatan garis, kami sekarang memodelkan proses etsa PVD dan IBE menggunakan fungsi deposisi dan etsa visibilitas SEmulator3D. PVD direproduksi menggunakan proses deposisi visibilitas penyebaran sudut 30 derajat di SEmulator3D, yang secara akurat memodelkan sifat acak atom Cu yang dikeluarkan selama pemboman dengan ion AR. IBE direproduksi dalam model menggunakan etsa visibilitas dengan penyebaran sudut 2 derajat dan kemiringan sudut kutub 60 derajat, untuk mencerminkan perilaku ion yang dipercepat jaringan dengan divergensi sinar rendah. Kedua wafer diasumsikan mempunyai putaran bebas. Langkah-langkah proses lainnya telah disesuaikan dalam proses fabrikasi virtual untuk mengakomodasi kendala IBE dan PVD. Gambar 2 menampilkan struktur yang sama yang dibuat menggunakan pengisian Cu damaskus (gambar 2a) dan proses PVD/IBE (gambar 2b). Langkah-langkah proses tambahan disertakan untuk menggabungkan batasan tertentu dari PVD/IBE dan menciptakan bentuk setara untuk struktur akhir yang kami inginkan.

![]()

Gambar 2: (2a) Fabrikasi kawat Cu isi Damaskus; (2b) Fabrikasi kawat PVD/IBE Cu.

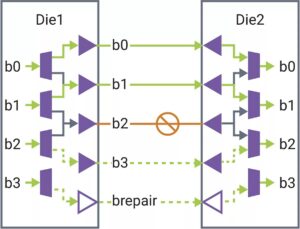

Kami kemudian menunjukkan bahwa sel sirkuit SRAM 16nm yang setara dapat dibuat dengan kabel PVD/IBE sambil tetap mematuhi batasan ini. Karena semua lapisan logam di atas ujung tengah garis dibuat dari permukaan datar, hal ini menjadikannya kandidat ide untuk kabel PVD/IBE, tidak seperti topologi interkoneksi kompleks yang terlihat pada perangkat finFET. Gambar 3 menampilkan struktur terisolasi dari setiap lapisan logam, dan langkah-langkah yang diperlukan untuk membuat struktur finFET tiga lapisan logam menggunakan PVD/IBE.

![]()

Gambar 3: (3a) FinFET MEOL 16nm dan 3 lapisan logam; (3b) Fabrikasi lapisan logam langkah demi langkah melalui PVD/IBE.

Hasil dan kesimpulan perlawanan

Kami kemudian mengukur hambatan listrik kabel dari lapisan logam paling atas hingga via saluran finFET P dan N, baik untuk aliran damaskus maupun deposisi uap fisik. Gambar 4 menunjukkan titik awal dan titik akhir pengukuran resistansi pada saluran P dan N (semua bahan isolasi lainnya transparan). Untuk mengkompensasi resistansi antarmuka antara lapisan TaN dan kawat tembaga, resistivitas tembaga ditingkatkan dengan menggunakan konstanta peluruhan eksponensial 1 nm sebagai fungsi jarak terdekat ke antarmuka TaN. Karena endapan Cu pada isian Damaskus diperkirakan tidak sepenuhnya berbentuk kristal, resistivitas Cu ditingkatkan sebesar 50%. Proses tembaga PVD/IBE tidak menggunakan lapisan TaN, sehingga fungsi peluruhan eksponensial tidak diterapkan, dan resistivitas sebagian besar tembaga digunakan dalam model ini. Tabel resistivitas yang membandingkan aliran Damaskus vs. PVD disertakan pada gambar 4.

![]()

Gambar 4: Titik awal dan titik akhir pengukuran resistansi pada saluran P dan N.

Nilai resistansi yang dihitung dari model kami menyatakan bahwa kami dapat mencapai penurunan resistansi sebesar 67% menggunakan metode fabrikasi IBE/PVD dibandingkan dengan pengetsaan parit konvensional yang diikuti dengan pengendapan damaskin. Hal ini terjadi karena tidak diperlukan lapisan TaN di IBE/PVD dan terdapat resistivitas CU yang lebih rendah selama proses ini. Hasil kami menunjukkan bahwa peningkatan resistivitas dapat dicapai dengan menggunakan IBE/PVD dibandingkan dengan pengisian damaskin selama pembentukan garis logam, dengan biaya proses fabrikasi yang lebih kompleks.

Timotius Yang

(semua posting)

Timothy Yang adalah insinyur aplikasi perangkat lunak di Coventor, sebuah Perusahaan Riset Lam. Dia bekerja dalam pengembangan proses, integrasi dan peningkatan hasil aplikasi, dengan keahlian dalam teknologi memori. Sebelum bekerja di Coventor, Yang bekerja di Tokyo Electron mengembangkan skema etsa, teknik peningkatan pola pasca litografi, kontrol aliran proses untuk aplikasi pola SADP dan SAQP, serta teknologi fotoresist litografi perendaman dan EUV. Yang menerima gelar B.S. gelar dalam bidang fisika dari UCLA, M.S. gelar dalam Ilmu Material dari Institut Teknologi Chiba, dan gelar Ph.D. gelar dalam Ilmu Material dari Universitas Tohoku.

- Konten Bertenaga SEO & Distribusi PR. Dapatkan Amplifikasi Hari Ini.

- Platoblockchain. Intelijen Metaverse Web3. Pengetahuan Diperkuat. Akses Di Sini.

- Mencetak Masa Depan bersama Adryenn Ashley. Akses Di Sini.

- Sumber: https://semiengineering.com/a-deposition-and-etch-technique-to-lower-resistance-of-semiconductor-metal-lines/

- :memiliki

- :adalah

- ][P

- 1

- 10

- 100

- a

- atas

- dipercepat

- menampung

- akurat

- Mencapai

- dicapai

- Tambahan

- Disesuaikan

- Semua

- Semua Tulisan

- dan

- Kaku

- aplikasi

- terapan

- AR

- ADALAH

- AS

- diasumsikan

- At

- atom

- BE

- Balok

- menjadi

- menjadi

- antara

- batas-batas

- by

- dihitung

- CAN

- calon

- tidak bisa

- tertentu

- saluran

- perusahaan

- dibandingkan

- pembandingan

- kompleks

- konstan

- kendala

- kontrol

- konvensional

- Tembaga

- Biaya

- membuat

- dibuat

- Kristal

- data

- mengurangi

- mendalam

- Derajat

- mendemonstrasikan

- tergantung

- deposit

- disimpan

- diinginkan

- berkembang

- Pengembangan

- alat

- Difusi

- menampilkan

- jarak

- Perbedaan

- turun

- selama

- setiap

- efek

- efek

- antara

- insinyur

- Setara

- EV

- diharapkan

- keahlian

- eksponensial

- Kegagalan

- Angka

- mengisi

- datar

- aliran

- diikuti

- Untuk

- bentuk

- pembentukan

- bentuk

- Gratis

- dari

- sepenuhnya

- fungsi

- fungsi

- kisi

- Memiliki

- he

- High

- sangat

- Lubang

- HTTPS

- ide

- pencelupan

- perbaikan

- perbaikan

- in

- insiden

- termasuk

- masuk

- menggabungkan

- Pada meningkat

- Meningkatkan

- menunjukkan

- Lembaga

- integrasi

- Antarmuka

- terpencil

- IT

- NYA

- jpg

- Melarikan diri

- lapisan

- lapisan

- keterbatasan

- Terbatas

- baris

- baris

- Panjang

- Rendah

- MEMBUAT

- masker

- masker

- bahan

- bahan

- max-width

- mengukur

- Memori

- logam

- metode

- Tengah

- model

- model

- lebih

- Alam

- perlu

- dibutuhkan

- of

- on

- urutan

- Lainnya

- kami

- Paralel

- path

- pola

- fisik

- Secara fisik

- Fisika

- plato

- Kecerdasan Data Plato

- Data Plato

- Titik

- kutub

- Pos

- Posts

- mencegah

- Sebelumnya

- proses

- proses

- acak

- diterima

- Merah

- mencerminkan

- daerah

- menghapus

- penelitian

- Perlawanan

- Hasil

- s

- sama

- sisik

- skema

- Ilmu

- semikonduktor

- Bentuknya

- berbentuk

- bentuk

- Pertunjukkan

- Melihat

- penting

- Silikon

- sejak

- tunggal

- lebih kecil

- So

- Perangkat lunak

- penyebaran

- Mulai

- Negara

- Langkah

- Tangga

- struktur

- Kemudian

- Permukaan

- tabel

- teknik

- Teknologi

- Teknologi

- bahwa

- Grafik

- Ini

- tiga

- kuku ibu jari

- untuk

- Tokyo

- paling atas

- secara tradisional

- jelas

- ucla

- memahami

- universitas

- menggunakan

- bekas

- dimanfaatkan

- Nilai - Nilai

- melalui

- maya

- jarak penglihatan

- volatil

- volume

- vs

- yang

- sementara

- akan

- Kawat

- dengan

- Kerja

- bekerja

- bekerja

- Menghasilkan

- zephyrnet.dll