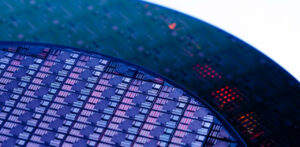

Banias Labs adalah perusahaan semikonduktor yang mengembangkan solusi infrastruktur untuk komunikasi generasi mendatang. Target pasarnya adalah pasar infrastruktur komputasi berkinerja tinggi termasuk pusat data skala besar, jaringan, AI, modul optik, dan SoC switch Ethernet untuk desain komputasi berkinerja tinggi yang sedang berkembang. SoC ini memerlukan desain Ethernet berkecepatan tinggi dan solusi latensi rendah untuk memberikan peningkatan kinerja sistem dan mempercepat waktu pemasaran. Perusahaan telah mengembangkan SoC DSP optik pada teknologi proses 5nm untuk memenuhi kebutuhan pasar ini.

![]()

SoC DSP optik adalah jenis system-on-chip (SoC) khusus yang dirancang untuk digunakan dalam sistem komunikasi optik berkecepatan tinggi. Selain DSP, SoC DSP optik biasanya mencakup blok IP antarmuka berkecepatan tinggi, seperti Ethernet PHY IP, PCIe IP, dan pengontrol memori DDR. Jenis SoC ini memungkinkan transfer data berkecepatan tinggi dengan latensi rendah untuk pemrosesan sinyal waktu nyata. Mereka juga dirancang untuk meminimalkan konsumsi daya, menjadikannya ideal untuk aplikasi yang memerlukan pengoperasian efisien dengan pengurangan masalah termal. Seiring dengan keuntungan, ada juga tantangan. Persyaratan khusus sistem komunikasi optik membuat perancangan SoC DSP optik lebih menantang daripada merancang SoC biasa.

Tantangan Implementasi

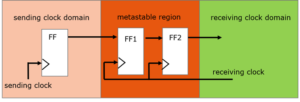

Tantangannya berkisar pada kompleksitas desain, persyaratan daya dan kinerja yang ketat, serta kebutuhan untuk memenuhi berbagai standar industri. Integrasi beberapa blok IP termasuk prosesor DSP, Ethernet PHY IP, dan blok khusus lainnya memerlukan desain dan validasi yang cermat. Antarmuka berkecepatan tinggi tambahan seperti PCIe dan DDR semakin menambah kompleksitas desain. Antarmuka berkecepatan tinggi dan beberapa blok IP dalam sistem dapat menimbulkan distorsi sinyal, crosstalk, dan interferensi elektromagnetik, yang dapat memengaruhi kinerja dan keandalan sistem. Analisis dan optimalisasi integritas sinyal dan daya harus dilakukan pada awal siklus desain untuk memastikan bahwa sistem dapat memenuhi persyaratan kinerja dan keandalannya. Yang terakhir, memenuhi persyaratan time-to-market dapat menjadi sebuah tantangan. Pasar infrastruktur komputasi berkinerja tinggi berkembang pesat, dan tim pengembangan SoC harus menyelesaikan desain mereka dengan cepat agar tetap menjadi yang terdepan dalam persaingan.

Mencapai Kesuksesan Silikon Tingkat Pertama

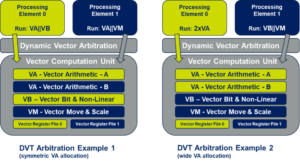

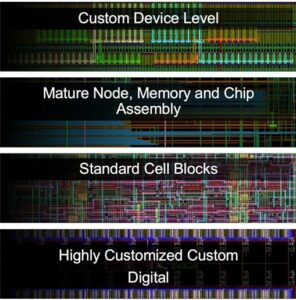

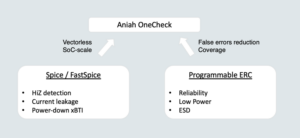

Mengatasi tantangan-tantangan tersebut di atas memerlukan pendekatan yang komprehensif. Salah satu komponen penting dari solusi kinerja tinggi dan latensi rendah adalah Ethernet PHY IP. Ethernet PHY IP bertanggung jawab atas antarmuka lapisan fisik antara SoC dan jaringan Ethernet. IP harus mendukung antarmuka Ethernet berkecepatan tinggi, termasuk 10G, 25G, 40G, 50G, 100G, 200G, 400G, dan 800G, serta memberikan latensi rendah dan konsumsi daya rendah. Selain itu, IP harus mendukung berbagai standar, termasuk IEEE 802.3 dan Ethernet Alliance. Komponen penting lainnya adalah rangkaian desain EDA. Rangkaian desain EDA harus memberikan solusi komprehensif untuk merancang dan memverifikasi SoC, termasuk optimalisasi daya, analisis kinerja, optimalisasi area, dan analisis hasil. Sejauh ini, rangkaian desain EDA mencakup fitur-fitur canggih, seperti kecerdasan buatan (AI) dan pembelajaran mesin (ML), yang lebih baik untuk meningkatkan produktivitas dan mengurangi waktu pemasaran.

Synopsys Mempercepat Kesuksesan First Pass Silicon

Synopsys menawarkan solusi yang mengatasi tantangan unik dalam mengembangkan SoC untuk pasar infrastruktur komputasi berkinerja tinggi. Perusahaan ini menyediakan solusi IP komprehensif yang mencakup studi kelayakan perutean, pedoman substrat pengemasan, model integritas sinyal dan daya, dan analisis crosstalk menyeluruh. Hal ini penting untuk mengatasi tantangan integritas sinyal dan daya yang dihadapi saat mengembangkan SoC DSP optik. 112G Ethernet PHY IP dari Synopsys menawarkan latensi rendah, panjang jangkauan yang fleksibel, dan kematangan pada teknologi proses 5nm, menjadikannya solusi ideal untuk pusat data skala besar, jaringan, AI, modul optik, dan SoC switch Ethernet. Selain itu, Synopsys menawarkan EDA Design Suite yang memberikan hasil berkualitas tinggi dengan daya, kinerja, area, dan hasil yang dioptimalkan. EDA Design Suite yang digerakkan oleh AI dari Synopsys memberikan solusi untuk meningkatkan kinerja sistem dan mempercepat waktu pemasaran, menjadikannya komponen penting dari solusi sukses untuk pasar infrastruktur komputasi berkinerja tinggi.

Kesimpulan

Synopsys memberikan solusi kinerja tinggi dan latensi rendah yang mempercepat pengembangan switch Ethernet canggih dan SoC jaringan. Untuk mempelajari lebih lanjut tentang solusi IP komprehensif Synopsys, EDA Design Suite yang komprehensif, dan EDA Suite yang Ditingkatkan AI, kunjungi halaman berikut.

Solusi IP komprehensif Synopsys

EDA Suite Synopsys yang komprehensif

Rangkaian Desain EDA berbasis AI dari Synopsys

Baca Juga:

Sistem Multi-Mati: Gangguan Terbesar dalam Komputasi Selama Bertahun-tahun

Memenuhi Kebutuhan Bandwidth yang Semakin Meningkat dengan Ethernet Berkecepatan Tinggi

Bagikan postingan ini melalui:

- Konten Bertenaga SEO & Distribusi PR. Dapatkan Amplifikasi Hari Ini.

- Platoblockchain. Intelijen Metaverse Web3. Pengetahuan Diperkuat. Akses Di Sini.

- Mencetak Masa Depan bersama Adryenn Ashley. Akses Di Sini.

- Sumber: https://semiwiki.com/ip/327703-synopsys-accelerates-first-pass-silicon-success-for-banias-labs-networking-soc/

- :memiliki

- :adalah

- a

- Tentang Kami

- atas

- mempercepat

- mempercepat

- tambahan

- Tambahan

- Selain itu

- alamat

- maju

- keuntungan

- di depan

- AI

- Persekutuan

- juga

- an

- analisis

- dan

- Lain

- aplikasi

- pendekatan

- ADALAH

- DAERAH

- sekitar

- buatan

- kecerdasan buatan

- Kecerdasan buatan (AI)

- AS

- At

- Bandwidth

- BE

- Lebih baik

- antara

- Terbesar

- Blok

- mendorong

- CAN

- hati-hati

- pusat

- tantangan

- menantang

- bagaimana

- Komunikasi

- komunikasi

- perusahaan

- kompetisi

- kompleksitas

- komponen

- komponen

- luas

- komputasi

- konsumsi

- membuat

- kritis

- adat

- siklus

- data

- Data Center

- menyampaikan

- memberikan

- Mendesain

- dirancang

- merancang

- desain

- dikembangkan

- berkembang

- Pengembangan

- mengembangkan

- Gangguan

- Awal

- efisien

- muncul

- aktif

- ditingkatkan

- memastikan

- penting

- berkembang

- dihadapi

- FAST

- Fitur

- Akhirnya

- Pertama

- fleksibel

- berikut

- Untuk

- dari

- lebih lanjut

- Pertumbuhan

- pedoman

- kinerja tinggi

- berkualitas tinggi

- HTML

- HTTPS

- kelaparan

- ideal

- IEEE

- gambar

- Dampak

- imperatif

- penting

- in

- termasuk

- Termasuk

- Pada meningkat

- industri

- standar industri

- Infrastruktur

- integrasi

- integritas

- Intelijen

- Antarmuka

- interface

- IP

- masalah

- IT

- NYA

- Labs

- Latensi

- lapisan

- BELAJAR

- pengetahuan

- Rendah

- mesin

- Mesin belajar

- membuat

- Membuat

- Pasar

- kematangan

- max-width

- Pelajari

- pertemuan

- Memori

- tersebut

- ML

- model

- modul

- lebih

- beberapa

- Perlu

- jaringan

- jaringan

- generasi selanjutnya

- of

- Penawaran

- on

- ONE

- operasi

- optimasi

- dioptimalkan

- Lainnya

- sendiri

- pengemasan

- lulus

- prestasi

- fisik

- plato

- Kecerdasan Data Plato

- Data Plato

- Pos

- kekuasaan

- proses

- pengolahan

- Prosesor

- produktifitas

- memberikan

- menyediakan

- segera

- cepat

- mencapai

- Baca

- real-time

- mengurangi

- reguler

- keandalan

- membutuhkan

- Persyaratan

- membutuhkan

- tanggung jawab

- Hasil

- Risiko

- semikonduktor

- Sinyal

- Silikon

- larutan

- Solusi

- khusus

- standar

- tinggal

- Belajar

- sukses

- sukses

- seperti itu

- rangkaian

- mendukung

- Beralih

- sistem

- sistem

- target

- tim

- Teknologi

- dari

- bahwa

- Grafik

- mereka

- Mereka

- panas

- Ini

- mereka

- ini

- untuk

- terlalu

- transfer

- jenis

- khas

- unik

- menggunakan

- pengesahan

- berbagai

- memverifikasi

- melalui

- Mengunjungi

- yang

- dengan

- Menghasilkan

- Anda

- zephyrnet.dll