Sejak debutnya pada tahun 1980-an dengan LAN bersama 10Mbps melalui kabel koaksial, Ethernet telah mengalami kemajuan yang konsisten, kini dengan potensi untuk mendukung kecepatan hingga 1.6Tbps. Kemajuan ini memungkinkan Ethernet untuk melayani aplikasi yang lebih luas, seperti streaming langsung, Jaringan Akses Radio, dan kontrol industri, menekankan pentingnya transfer paket yang andal dan kualitas layanan. Dengan bandwidth Internet saat ini yang mencapai ~500 Tbps, terdapat peningkatan permintaan untuk penanganan lalu lintas intra pusat data back-end yang lebih baik. Meskipun masing-masing server belum beroperasi pada tingkat Terabit per detik, lalu lintas pusat data secara keseluruhan mendekati skala ini, sehingga mendorong grup 802.3dj IEEE untuk melakukan upaya standardisasi dan memerlukan pengontrol Ethernet dan SerDe yang kuat untuk mengelola aliran data yang meluas. Di tengah meningkatnya permintaan, komunikasi antarprosesor sudah mencapai kecepatan tersebut.

Komunikasi antarprosesor menjadi ujung tombak kebutuhan akan kecepatan 1.6T dengan latensi minimal. Meskipun masing-masing perangkat dibatasi oleh kapasitas pemrosesan dan ukuran chip bawaannya, penggabungan chip dapat meningkatkan kapasitas ini secara signifikan. Aplikasi generasi pertama diharapkan akan diikuti oleh koneksi switch-to-switch intra pusat data, yang memungkinkan penggabungan prosesor dan memori berkinerja tinggi, meningkatkan skalabilitas dan efisiensi dalam komputasi awan.

Inisiatif 802.3dj IEEE: Memajukan standar Ethernet untuk interoperabilitas 1.6 Tbps

Kepatuhan terhadap upaya standardisasi yang terus berkembang sangat penting untuk kelancaran interoperabilitas ekosistem. Grup 802.3dj IEEE sedang dalam proses merumuskan standar Ethernet yang akan datang, yang mencakup lapisan fisik dan parameter manajemen untuk kecepatan dari 200G hingga 1.6 Terabit per detik. Sasaran grup ini adalah kecepatan data MAC Ethernet 1.6 Tbps, yang bertujuan untuk tingkat kesalahan bit maksimum tidak lebih dari 10-13 pada lapisan MAC. Ketentuan lebih lanjut mencakup Antarmuka Unit Lampiran (AUI) jalur 16 & 8 opsional yang cocok untuk aplikasi chip berbeda, memanfaatkan SerDes 112G dan 224G. Secara fisik, spesifikasi 1.6Tbps memerlukan transmisi melalui 8 pasang kabel tembaga twinax hingga satu meter dan 8 pasang fiber untuk jarak antara 500 meter hingga 2 km. Meskipun ratifikasi lengkap standar ini diperkirakan akan dilakukan pada musim semi tahun 2026, serangkaian fitur inti diperkirakan akan selesai pada tahun 2024.

Overhead bandwidth dan koreksi kesalahan dalam subsistem Ethernet 1.6T

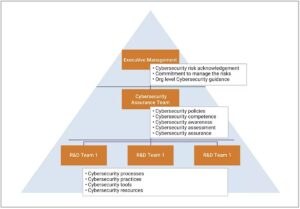

Gambar 1: Diagram yang menggambarkan komponen Subsistem Ethernet 1.6T.

Pada iterasi Ethernet sebelumnya, PCS terutama berfokus pada pengkodean data untuk deteksi paket yang andal. Namun, dengan peningkatan kecepatan Ethernet ke 1.6T, kebutuhan akan Forward Error Correction (FEC) menjadi jelas, terutama untuk mengatasi degradasi sinyal bahkan pada sambungan pendek. Untuk tujuan ini, Ethernet 1.6T terus memanfaatkan Reed-Solomon FEC. Pendekatan ini membangun sebuah codeword yang terdiri dari 514 simbol 10-bit yang dikodekan ke dalam blok simbol 544, sehingga menghasilkan overhead bandwidth sebesar 6%. Kata kode FEC ini didistribusikan ke seluruh tautan fisik AUI sehingga setiap tautan fisik (8 untuk 1.6T Ethernet) tidak membawa seluruh kata kode. Metode ini tidak hanya memberikan perlindungan tambahan terhadap ledakan kesalahan tetapi juga memungkinkan paralelisasi pada dekoder ujung jauh, sehingga mengurangi latensi.

Physical Medium Attachment (PMA), yang dilengkapi gearbox dan SerDes, membawa sinyal Ethernet ke saluran yang ditransmisikan. Untuk Ethernet 1.6T, ini melibatkan 8 saluran yang masing-masing berjalan pada 212Gbps, yang menyebabkan overhead FEC sebesar 6%. Teknik modulasi yang digunakan adalah 4-Level Pulse Amplitude Modulation (PAM-4), yang mengkodekan dua bit data untuk setiap simbol transmisi, sehingga secara efektif menggandakan bandwidth bila disandingkan dengan pendekatan tradisional Non-Return Zero (NRZ). Mekanisme transmisi bergantung pada konversi digital ke analog, sedangkan di sisi penerima, konversi analog ke digital dikombinasikan dengan DSP memastikan ekstraksi sinyal akurat.

Selain itu, penting untuk dicatat bahwa Ethernet PCS memperkenalkan “FEC luar” yang menjangkau ujung ke ujung pada tautan Ethernet. Untuk memperkuat saluran jangkauan yang lebih panjang, lapisan tambahan koreksi kesalahan untuk masing-masing jalur fisik sedang direncanakan, kemungkinan besar akan mengadopsi kode hamming FEC. Koreksi ini diperkirakan akan menemukan penerapan utamanya pada modul transceiver optik di mana koreksi tersebut sangat penting.

Gambar 2: Diagram yang menampilkan overhead tambahan yang ditambahkan saat menggunakan FEC gabungan untuk jangkauan yang lebih luas.

Dalam contoh sistem yang digambarkan pada gambar 2, MAC dan PCS dihubungkan melalui modul optik dan bentangan serat. PCS memiliki tingkat kesalahan bit 10-5 pada link modul optik, ditambah kesalahan dari link optik itu sendiri. Menggunakan satu-satunya RS-FEC end-to-end tidak akan cukup untuk mencapai angka 10-13 Standar Ethernet, menjadikan tautan tidak dapat diandalkan. Pilihannya adalah penerapan tiga kali lipat RS FEC terpisah di setiap hop, sehingga meningkatkan biaya dan latensi secara signifikan. Solusi yang lebih efektif adalah integrasi FEC Kode Hamming gabungan khusus untuk tautan optik, yang melayani kesalahan acak khas koneksi optik. Lapisan FEC bagian dalam ini menciptakan perluasan tambahan pada laju saluran dari 212 Gbps menjadi 226 Gbps, oleh karena itu SerDes harus dapat mendukung laju saluran ini.

Tantangan latensi dalam sistem Ethernet 1.6T

Gambar 3: Jalur latensi untuk Subsistem Ethernet 1.6T.

Berbagai komponen berkontribusi terhadap latensi Ethernet: antrian transmisi, durasi transmisi, waktu traversal menengah, dan beberapa waktu pemrosesan dan penerimaan. Untuk memvisualisasikannya, perhatikan gambar 3, yang menampilkan subsistem Ethernet 1.6T yang komprehensif. Meskipun latensi dapat dipengaruhi oleh waktu reaksi aplikasi ujung jauh, faktor ini berada di luar Ethernet dan oleh karena itu sering kali dikecualikan selama analisis latensi. Meminimalkan latensi pada antarmuka Ethernet memerlukan pemahaman tentang keadaan spesifik. Misalnya, latensi mungkin tidak menjadi perhatian utama untuk koneksi trunk antar switch karena penundaan yang melekat pada link klien yang lebih lambat. Jarak juga berperan; panjang yang lebih besar menyebabkan lebih banyak latensi. Tentu saja, ini tidak berarti bahwa kita harus mengabaikan latensi dalam skenario lain, mengurangi latensi selalu menjadi tujuan.

Latensi transmisi secara inheren terkait dengan kecepatan Ethernet dan ukuran frame. Khususnya, untuk sistem Ethernet 1.6T, transmisi paket berukuran minimum memerlukan 0.4ns – pada dasarnya, satu frame Ethernet per tick pada clock 2.5 GHz. Di sisi lain, transmisi frame berukuran maksimum standar memerlukan 8ns, diperpanjang hingga 48ns untuk Jumbo Frames. Media yang dipilih selanjutnya menentukan latensi. Misalnya, serat optik biasanya mempunyai latensi 5ns per meter, sedangkan kabel tembaga sedikit lebih cepat yaitu 4ns per meter.

Sebagian besar latensi keseluruhan berakar pada pengontrol penerima. Dekoder RS FEC secara inheren menimbulkan latensi. Untuk memulai koreksi kesalahan, sistem harus menerima 4 codeword, yang pada 1.6Tbps, berjumlah 12.8ns. Aktivitas selanjutnya, termasuk koreksi kesalahan dan buffering, memperkuat latensi ini. Meskipun durasi penyimpanan codeword FEC tetap konsisten, latensi selama penerimaan pesan bergantung pada implementasi spesifik. Namun demikian, latensi dapat dioptimalkan dengan menggunakan strategi desain digital yang cermat.

Intinya, terdapat latensi bawaan yang tidak dapat dihindari karena mekanisme FEC dan jarak fisik atau panjang kabel. Di luar faktor-faktor ini, keahlian desain memainkan peran penting untuk meminimalkan latensi pengontrol Ethernet. Memanfaatkan solusi lengkap yang mengintegrasikan dan mengoptimalkan MAC, PCS, dan PHY, membuka jalan bagi implementasi latensi rendah dan paling efisien.

Kesimpulan

Gambar 4: Keberhasilan silikon tingkat pertama untuk Synopsys 224G Ethernet PHY IP dalam proses 3nm yang menampilkan mata PAM-4 yang sangat linier.

Ethernet 1.6 Tbps dirancang untuk aplikasi yang paling membutuhkan bandwidth dan sensitif terhadap latensi. Dengan munculnya teknologi 224G SerDes, bersamaan dengan kemajuan dalam MAC dan PCS IP, solusi komprehensif kini dapat diakses dan terus menyesuaikan diri dengan standar Ethernet 1.6T yang terus berkembang. Selain itu, karena latensi yang melekat pada protokol dan metode koreksi kesalahan, desain IP digital dan analog harus dibuat dengan cermat oleh desainer ahli untuk menghindari memasukkan latensi yang tidak perlu ke dalam jalur data.

Untuk mencapai performa terbaik untuk desain SoC 1.6T memerlukan arsitektur yang dioptimalkan secara efisien dan praktik desain yang cermat untuk setiap komponen chip. Hal ini menekankan penghematan daya dan meminimalkan jejak silikon, sehingga mewujudkan kecepatan data 1.6T. Synopsys 224G Ethernet PHY IP yang terbukti silikon telah menyiapkan panggung untuk 1.6T MAC dan PCS Controller. Menggunakan teknik desain, analisis, simulasi, dan pengukuran terdepan, Synopsys terus memberikan integritas sinyal dan kinerja jitter yang luar biasa, dengan a solusi Ethernet lengkap termasuk MAC+PCS+PHY.

- Konten Bertenaga SEO & Distribusi PR. Dapatkan Amplifikasi Hari Ini.

- PlatoData.Jaringan Vertikal Generatif Ai. Berdayakan Diri Anda. Akses Di Sini.

- PlatoAiStream. Intelijen Web3. Pengetahuan Diperkuat. Akses Di Sini.

- PlatoESG. Karbon, teknologi bersih, energi, Lingkungan Hidup, Tenaga surya, Penanganan limbah. Akses Di Sini.

- PlatoHealth. Kecerdasan Uji Coba Biotek dan Klinis. Akses Di Sini.

- Sumber: https://semiengineering.com/latency-considerations-for-1-6t-ethernet-designs/

- :memiliki

- :adalah

- :bukan

- :Di mana

- $NAIK

- 1

- 12

- 16

- 2024

- 2026

- 212

- 220

- 362

- 500

- 8

- a

- mengakses

- dapat diakses

- akuntansi

- tepat

- Mencapai

- di seluruh

- kegiatan

- menambahkan

- Tambahan

- Selain itu

- Mengadopsi

- kemajuan

- maju

- terhadap

- Bertujuan

- diizinkan

- sudah

- juga

- Meskipun

- selalu

- di tengah-tengah

- jumlah

- memperkuat

- an

- analisis

- dan

- Diantisipasi

- Aplikasi

- aplikasi

- pendekatan

- arsitektur

- ADALAH

- AS

- At

- menghindari

- Back-end

- latar belakang

- Bandwidth

- BE

- menjadi

- antara

- Luar

- Bit

- Memblokir

- mendukung

- meningkatkan

- Membawa

- membangun

- tapi

- by

- kabel

- kabel

- CAN

- kapasitas

- membawa

- tantangan

- saluran

- keping

- Keripik

- terpilih

- keadaan

- klien

- Clock

- awan

- komputasi awan

- kode

- bergabung

- menggabungkan

- Komunikasi

- lengkap

- penyelesaian

- komponen

- komponen

- luas

- terdiri

- komputasi

- Perhatian

- hubungan

- terhubung

- Koneksi

- KONSERVASI

- Mempertimbangkan

- pertimbangan

- konsisten

- terus

- terus menerus

- menyumbang

- kontrol

- pengawas

- Konversi

- Tembaga

- Core

- Biaya

- menetralkan

- Tentu saja

- dibuat

- menciptakan

- terbaru

- data

- Datacenter

- debut

- keterlambatan

- menyampaikan

- Permintaan

- menuntut

- tuntutan

- menggambarkan

- Mendesain

- desainer

- desain

- Deteksi

- Devices

- mendikte

- berbeda

- digital

- rajin

- menampilkan

- jarak

- didistribusikan

- Tidak

- dua kali lipat

- dua

- lamanya

- selama

- setiap

- Terdahulu

- ekosistem

- Efektif

- efektif

- efisiensi

- efisien

- efisien

- upaya

- munculnya

- menekankan

- menekankan

- dipekerjakan

- mempekerjakan

- memungkinkan

- memungkinkan

- meliputi

- akhir

- ujung ke ujung

- Memastikan

- Seluruh

- kesalahan

- kesalahan

- eskalasi

- esensi

- penting

- dasarnya

- Eter (ETH)

- Bahkan

- Setiap

- jelas

- berkembang

- contoh

- luar biasa

- dikecualikan

- memperluas

- perluasan

- diharapkan

- ahli

- keahlian

- memperpanjang

- memperpanjang

- luar

- ekstraksi

- mata

- faktor

- faktor

- jauh

- lebih cepat

- Fitur

- Menampilkan

- Angka

- Menemukan

- Pertama

- Generasi pertama

- aliran

- terfokus

- diikuti

- Tapak

- Untuk

- merumuskan

- Depan

- FRAME

- dari

- lebih lanjut

- generasi

- memberikan

- lebih besar

- Kelompok

- Grup

- Pertumbuhan

- tangan

- Penanganan

- High

- kinerja tinggi

- sangat

- Namun

- HTML

- HTTPS

- imperatif

- implementasi

- pentingnya

- penting

- ditingkatkan

- in

- Di lain

- memasukkan

- Termasuk

- meningkatkan

- sendiri-sendiri

- industri

- terpengaruh

- inheren

- secara inheren

- memulai

- Prakarsa

- contoh

- Terintegrasi

- integrasi

- integritas

- Antarmuka

- interface

- Internet

- Interoperabilitas

- ke

- hakiki

- memperkenalkan

- Memperkenalkan

- memperkenalkan

- melibatkan

- IP

- IT

- iterasi

- NYA

- Diri

- jpg

- Jalur

- Latensi

- lapisan

- lapisan

- Panjang

- adalah ide yang bagus

- leveraging

- Mungkin

- baris

- baris

- LINK

- link

- hidup

- lagi

- Rendah

- mac

- Membuat

- mengelola

- pengelolaan

- max-width

- maksimum

- Mungkin..

- berarti

- pengukuran

- mekanisme

- medium

- Memori

- pesan

- metode

- metode

- teliti

- minimal

- memperkecil

- meminimalkan

- meminimalkan

- modul

- Modul

- lebih

- paling

- harus

- mendekati

- Perlu

- jaringan

- Namun

- tidak

- mencatat

- sekarang

- tujuan

- of

- sering

- on

- ONE

- hanya

- operasi

- dioptimalkan

- Mengoptimalkan

- pilihan

- or

- Lainnya

- lebih

- secara keseluruhan

- pasang

- parameter

- khususnya

- path

- PC

- untuk

- prestasi

- pertunjukan

- fisik

- Secara fisik

- pipa saluran

- sangat penting

- plato

- Kecerdasan Data Plato

- Data Plato

- memainkan

- plus

- potensi

- kekuasaan

- praktek

- terutama

- primer

- proses

- pengolahan

- prosesor

- deret

- diproyeksikan

- perlindungan

- protokol

- nadi

- tujuan

- Mendorong

- kualitas

- radio

- acak

- jarak

- Penilaian

- Tarif

- mencapai

- mencapai

- reaksi

- Kenyataan

- menerima

- menerima

- penerimaan

- mengurangi

- dapat diandalkan

- sisa

- render

- membutuhkan

- terbatas

- dihasilkan

- kuat

- Peran

- berakar

- berjalan

- Skalabilitas

- Skala

- skenario

- mulus

- Kedua

- terlihat

- ruas

- peka

- terpisah

- melayani

- layanan

- set

- beberapa

- berbagi

- Pendek

- harus

- menampilkan

- Sinyal

- signifikan

- Silikon

- simulasi

- Ukuran

- So

- larutan

- Solusi

- rentang

- ujung tombak

- tertentu

- Secara khusus

- spesifikasi

- kecepatan

- musim semi

- Tahap

- standar

- standardisasi

- standar

- penyimpanan

- strategi

- Streaming

- selanjutnya

- besar

- sukses

- seperti itu

- cocok

- mendukung

- simbol

- sistem

- disesuaikan

- Dibutuhkan

- teknik

- teknik

- Teknologi

- dari

- bahwa

- Grafik

- mereka

- Sana.

- dengan demikian

- karena itu

- Ini

- ini

- Melalui

- Demikian

- tick

- Terjalin

- waktu

- kali

- untuk

- puncak

- tradisional

- lalu lintas

- transfer

- mengirimkan

- Rangkap tiga

- dua

- khas

- khas

- tidak bisa dihindari

- pemahaman

- melakukan

- satuan

- mendatang

- atas

- menggunakan

- Penggunaan

- melalui

- membayangkan

- Cara..

- we

- ketika

- yang

- sementara

- lebih luas

- dengan

- dalam

- akan

- namun

- zephyrnet.dll

- nol