Integrasi beberapa cetakan heterogen dalam satu paket sangat penting untuk memperluas Hukum Moore dan meningkatkan kinerja, efisiensi daya, dan fungsionalitas, namun juga menimbulkan masalah signifikan mengenai cara mengelola beban termal.

Kemasan canggih menyediakan cara untuk mengemas lebih banyak fitur dan fungsi ke dalam perangkat, dengan menumpuk berbagai komponen secara vertikal, bukan hanya mengecilkan sirkuit digital untuk menjejalkan lebih banyak fungsi ke dalam SoC berukuran reticle. Hal ini menimbulkan permasalahan tentang cara mengoptimalkan kinerja dan daya. Pada satu cetakan, jalur sinyal dapat dibuat sesingkat yang diperlukan, dan media efektif dalam menghilangkan panas. Namun dengan banyaknya cetakan dalam satu paket, substrat dan dielektrik harus lebih tipis untuk mengurangi jarak tempuh sinyal, dan membatasi pembuangan panas.

Hal ini dapat menyebabkan hotspot, yang sulit diprediksi, terutama pada beban kerja dan kasus penggunaan yang berbeda-beda. Dan hal ini dapat menjadi lebih buruk ketika mengintegrasikan beberapa chip atau chiplet dengan sifat termal yang berbeda-beda ke dalam satu paket.

“Setiap kali Anda meletakkan banyak cetakan pada substrat atau interposer, itu merupakan tantangan,” kata Vik Chaudhry, direktur senior, pemasaran produk dan pengembangan bisnis di Teknologi Amkor. “Kami melihat vendor tidak hanya memasukkan 3 atau 4, tapi 8 atau 10 atau 12 die. Bagaimana Anda mendistribusikan panas itu ke sekeliling?”

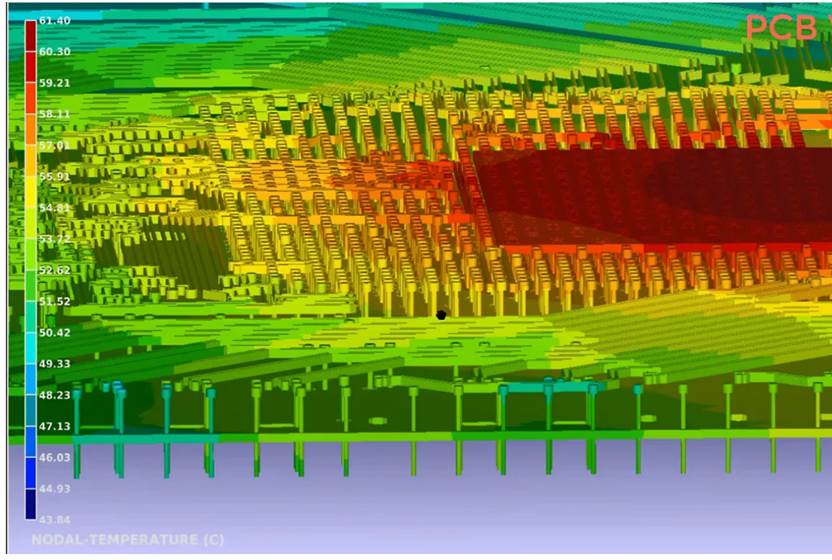

Gambar 1: Simulasi pembuangan panas pada pasangan termal. Sumber: Ansys

Integrasi heterogen bergantung pada kemampuan untuk menghilangkan panas secara efektif, memastikan bahwa cetakan padat di dalam modul mempertahankan suhu yang dapat diterima untuk pengoperasian yang andal. Peta Jalan Integrasi Heterogen IEEE mengidentifikasi beberapa bidang kebutuhan pengembangan, termasuk teknik pemodelan canggih untuk memprediksi dan mengelola aliran panas, material baru dengan konduktivitas termal tinggi dan konduktivitas listrik rendah, serta solusi pendinginan baru yang dapat diintegrasikan dengan mulus ke dalam paket kompleks.

Ketidakcocokan termal

Pilihan material sangat penting untuk manajemen termal dalam integrasi heterogen. Saat komponen dengan koefisien muai panas (CTE) berbeda memanas dan mendingin, material ini memuai dan menyusut dengan laju berbeda. Hal ini dapat menyebabkan tekanan mekanis yang membahayakan integritas chip, melemahkan ikatan yang menghubungkan chip ke interposer atau substrat lain, dan memengaruhi fungsionalitas perangkat secara keseluruhan.

Menggunakan material dengan CTE serupa membantu mengurangi tekanan ini, mengurangi beberapa risiko kegagalan dini, serta efek termal lainnya, seperti percepatan penuaan, berkurangnya mobilitas elektron, atau penyimpangan sinyal analog atau optik.

“CTE mungkin merupakan tantangan nomor satu dalam pengemasan yang canggih, dan menurut saya belum ada yang benar-benar memahaminya,” kata David Fromm, COO dan wakil presiden bidang teknik di Industri Promex. “Kami menangani CTE dalam skala tiga dimensi dengan cara yang belum pernah kami lihat sebelumnya, dan masalah bagian yang bengkok atau pecah ini merupakan tantangan yang sangat besar. Beberapa perusahaan mungkin memikirkan proses tertentu, lalu materialnya berubah, ukuran perangkatnya berubah, dan persamaannya pun berubah. Dan kemudian Anda harus memikirkannya lagi.”

Sederhananya, integrasi heterogen memerlukan pemahaman mendasar tentang sifat ekspansi termal setiap material yang pada akhirnya dapat membentuk keandalan dan hasil perangkat yang dikemas. Dan itu hanya sebagian dari masalahnya. Pengemasan tingkat lanjut memerlukan pemahaman tentang apa lagi yang ada di sekitar sebuah chip atau chiplet, bagaimana elemen-elemen lain tersebut digunakan, dan semua itu perlu dimodelkan dan disimulasikan bersama-sama menggunakan beban kerja yang diharapkan menjadi realistis. Masalah ini menjadi lebih sulit ketika kebutuhan komputasi berubah, seperti di pusat data di mana AI generatif telah meningkatkan jumlah data yang perlu diproses secara signifikan, sehingga menghasilkan pemanfaatan prosesor dan memori yang lebih tinggi.

“Analisis termal pada tingkat tertentu selalu dilakukan, namun hal ini dilakukan di akhir hanya untuk memastikan bahwa tidak ada hal yang berlebihan,” kata Marc Swinnen, direktur pemasaran produk di ansys. “Anda dapat menargetkan suhu persimpangan tertentu, dan jika sesuai, maka sesederhana itu. Namun sekarang dengan sistem multi-die, Anda harus melakukannya pada tahap perencanaan lantai RTL. Anda harus mempunyai gambaran tentang keluaran daya masing-masing chip ini sehingga dua chip yang menjadi panas pada mode operasi yang sama tidak ditempatkan tepat di samping satu sama lain atau tepat di atas satu sama lain. . Itu akan merusak desain Anda.”

Kembali ke papan gambar

Ketika industri bergulat dengan berbagai tantangan terhadap peta jalan integrasi heterogen, pengelolaan termal tidak lagi menjadi sebuah hal yang hanya sekedar renungan. Hal ini telah bergeser ke kiri dalam aliran desain-melalui-manufaktur, dan keluar ke bidang di mana monitor dalam sirkuit dapat menilai dan menyesuaikan segala sesuatu mulai dari partisi hingga penentuan prioritas chip dan chiplet yang berbeda.

“Iblis ada dalam detailnya,” kata Fromm. “Keputusan desain dan integrasi yang tampaknya kecil ini dapat berdampak besar pada apakah Anda dapat membangun apa yang Anda inginkan, apalagi membangunnya dengan hasil dan keandalan produk di hilir. Memilih bahan yang tepat, memikirkan tumpukannya, dan memikirkan alur prosesnya, semuanya sangatlah penting.”

Hal ini mewakili perubahan mendasar dalam semakin banyak desain, dari pusat data ke elektronik konsumen dan semakin banyak kendaraan otonom. Ketika unsur-unsur heterogen dikemas bersama dalam fan-out dengan pilar, 2.5D, dan terutama di 3D-IC desain, jalur termal perlu dipetakan secara lebih rinci. Jika dilakukan secara salah, hal ini dapat menyebabkan kerusakan pada seluruh paket yang berisi banyak chip/chiplet, sehingga bahkan menemukan sumber masalahnya bisa memakan biaya yang besar.

“Ada kebutuhan untuk merancang kendala mekanis termal serta substrat dan teknologi perakitan,” kata George Orji, ilmuwan peneliti untuk CHIPS National Advanced Packaging Manufacturing Program (NAPMP). “Kemasan tingkat lanjut tidak memungkinkan adanya pengerjaan ulang, jadi metodologi desain chip monolitik untuk pengemasan tingkat lanjut adalah sesuatu yang perlu kami lakukan.”

Kompleksitas yang melekat dalam sistem yang terintegrasi secara heterogen menuntut pendekatan desain multi-disiplin. Ini adalah hal yang rumit, dan upaya untuk membuat pendekatan ini berhasil bukanlah hal baru, dan gagal dalam menghadapi penskalaan planar. David Fried, wakil presiden perusahaan di Penelitian Lam, mengatakan dalam diskusi panel baru-baru ini bahwa IBM mencoba integrasi heterogen 3D 25 tahun yang lalu ketika dia berada di sana. “Kami pikir kami bisa menyatukan banyak komponen proses di dalamnya,” katanya. “Tetapi beberapa tantangan terbesar ada pada sisi desain dan EDA, memilah teknologi apa yang akan digunakan, bagaimana melakukan segmentasi berbagai komponen sistem pada chip yang berbeda, dan kemudian kembali dan mengintegrasikannya kembali. Desain dan optimalisasi desain harus ada agar hal ini dapat berfungsi.”

Yang berubah sejak saat itu adalah industri chip sudah kehabisan pilihan. Mengembangkan chip pada node paling canggih menjadi terlalu mahal, dan terlalu dibatasi oleh ukuran reticle. Namun ini masih merupakan pekerjaan yang sulit.

Untuk meringankan beban para desainer, teknik sinergis yang melibatkan ilmu material tingkat lanjut dan alat desain berbantuan komputer menjadi semakin penting, terutama ketika konfigurasi chip menjadi lebih rumit dan fungsionalitas terintegrasi meningkat. “Di sinilah kami masih memiliki pekerjaan yang harus dilakukan,” tambah Swinnen dari Ansys. “Bagaimana kita mengatasi hal ini dengan cara yang tidak mengharuskan setiap desainer menjadi ahli dalam bidang termal, ahli dalam interferensi elektromagnetik, dan ahli dalam bidang mekanik? Tidak realistis mengharapkan hal seperti itu dari komunitas desain kami.”

Dengan adanya kendala-kendala ini muncullah perlunya inovasi dalam beberapa aspek utama proses desain. Menyadari sifat multi-aspek pembangkitan panas dalam chip yang terintegrasi secara padat, penting untuk mengatasi tidak hanya peristiwa termal dalam kondisi stabil, namun juga peristiwa termal sementara, yang sebagian besar didasarkan pada kasus penggunaan atau beban kerja. Peta jalan untuk integrasi heterogen mencakup strategi seperti material antarmuka termal 3D dan penyebar panas yang cocok dengan CTE untuk memastikan distribusi panas yang merata.

“Dengan banyak cetakan, Anda memiliki banyak sumber efek termal, berbagai gradien mekanis, dan gradien suhu,” kata Manuel Mota, manajer pemasaran produk senior di Synopsys. “Semua ini harus diatasi dalam tahap desain.”

Mengintegrasikan pertimbangan termal ke dalam proses desain merupakan persyaratan untuk realisasi praktis perangkat semikonduktor kompleks. Ini bukan hanya tentang mengidentifikasi bahan atau komponen yang tepat. Mereka juga membayangkan bagaimana mereka semua akan berfungsi secara kolektif di lapangan.

Ketika para insinyur mengurangi faktor bentuk perangkat elektronik sambil meningkatkan kinerjanya, selubung termal menjadi semakin ketat. Pengelolaan profil termal yang komprehensif di berbagai kondisi operasional, memanfaatkan penyebar panas terbaru dan material antarmuka termal, menjadi penting untuk menjaga integritas dan kinerja perangkat selama siklus hidup yang diinginkan.

“Termal adalah batasan nomor satu untuk kepadatan integrasi,” kata Swinnen. “Sangat mudah untuk menumpuk chipnya. Anda dapat memproduksinya dan mendesainnya, tetapi itu tidak akan berhasil karena akan menjadi terlalu panas. Jadi termal telah menjadi bagian utama dari perhatian setiap perancang chip 3D-IC.”

Menyelesaikan tantangan termal dalam integrasi heterogen memerlukan penggabungan material yang berbeda, seperti semikonduktor dengan CTE lebih rendah, seperti silikon, dengan logam seperti tembaga atau aluminium, untuk menghilangkan panas secara efektif. Sayangnya, campuran bahan ini sering kali menyebabkan lengkungan, retak, tonjolan solder terangkat, dan perangkat rusak lebih awal dari yang diperkirakan. Dibutuhkan material baru yang memiliki sifat kompatibel untuk mengatasi masalah ini.

“Bahan substrat ini mungkin akan berkembang lebih lambat dibandingkan bahan antarmuka, perekat, epoksi, dan sebagainya,” kata Fromm. “Ini tergantung pada kondisi proses dan cara Anda mengelolanya. Hal yang bisa menjadi lebih baik dalam sisi pemrosesan adalah dengan bekerja sama dengan produsen perekat untuk memahami perubahan suhu, dan kemudian pada tingkat desain untuk memahami bagaimana semua tumpukan ini dapat berkembang, dengan mempertimbangkan perubahan suhu tersebut.”

Inovasi material

Kekhawatiran termal lebih dari sekedar pengoperasian chip. Panas juga merupakan masalah di sisi manufaktur. Chip di dalam paket canggih harus bertahan dalam perakitan dan produksi, sehingga beberapa masalah CTE yang sama dapat menjadi masalah.

Pertimbangkan contoh die-to-wafer kolektif (CoD2W), yang menggunakan ikatan termo-kompresi untuk menempelkan cetakan ke wafer. “Dalam proses CoD2W, terdapat situasi di mana cetakan yang berbeda berasal dari sumber yang berbeda, dan dapat memiliki ketinggian atau ketebalan yang berbeda,” kata Rama Puligadda, direktur eksekutif Penelitian dan Pengembangan Teknologi Lanjutan di Ilmu Pembuatan Bir. “Saat Anda mempopulasikan hewan pembawa dengan kematian ini, sangat sulit untuk mengetahui apakah semua kematian tersebut akan melakukan kontak dengan target selama ikatan. Sifat mekanik dari perekat die-attach dirancang untuk memungkinkan cetakan yang lebih tinggi sedikit tertanam selama pengikatan, sehingga memungkinkan kontak yang baik antara semua cetakan dengan wafer target.”

Hal ini menimbulkan permasalahan yang berbeda. “Tantangan pada material kami mencakup batasan suhu pada cetakan yang berbeda,” kata Puligadda. “Kami harus memastikan bahwa suhu yang digunakan untuk mengikat material tidak melebihi batasan termal dari chip mana pun yang diintegrasikan ke dalam paket. Selain itu, mungkin ada beberapa proses selanjutnya seperti pembentukan atau pencetakan lapisan redistribusi. Materi kami harus bertahan dalam proses tersebut. Mereka harus bertahan dari bahan kimia yang bersentuhan dengan mereka selama skema proses pengemasan. Tekanan mekanis dalam kemasan menambah tantangan tambahan untuk merekatkan material.”

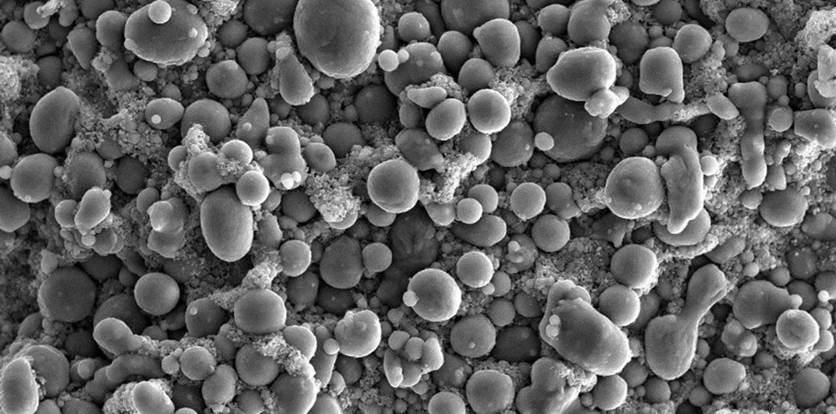

Berbagai bahan sedang dalam pengembangan yang menawarkan konduktivitas termal yang unggul serta isolasi listrik. Bahan antarmuka termal (TIM) yang baru direkayasa ini menyediakan jalur konduksi panas yang efisien antara chip dan pendinginnya tanpa mengganggu kinerja chip. TIM tidak hanya meningkatkan konduktivitas termal tetapi juga memenuhi perbedaan kecil yang disebabkan oleh pembangkitan panas yang tidak merata di seluruh permukaan chip.

“Manajemen termal akan memerlukan material termal baru, serta topologi sirkuit baru yang menggunakan substrat canggih dan integrasi heterogen,” kata Orji. “Karena chip dikemas sangat berdekatan satu sama lain, kemampuan menyebarkan panas berlebih sangat terbatas.”

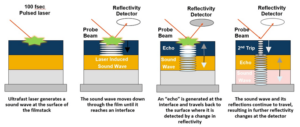

Gambar 2: Tampilan detail bahan antarmuka termal polimer yang sarat partikel. Sumber: Amkor

Idealnya, material baru ini akan menunjukkan ikatan kovalen yang kuat dan massa anion-kation yang seimbang, serupa dengan struktur atom sederhana yang ditemukan pada berlian. Bahan yang dikenal dalam kategori ini termasuk intan, bersama dengan senyawa seperti berilium oksida, aluminium nitrida, boron nitrida, dan, sampai batas tertentu, silikon nitrida. Terlepas dari kemampuan konduksi termalnya, bahan-bahan ini menimbulkan tantangan manufaktur karena ikatan yang memberikan kekuatannya, sehingga memerlukan proses sintering suhu tinggi, misalnya, untuk mencapai kepadatan yang diinginkan. Pengecualian adalah berlian, yang tidak dapat disintering.

Salah satu pendekatan untuk memanfaatkan manfaat bahan-bahan ini, meskipun terdapat tantangan dalam pengolahannya, adalah dengan memanfaatkan komposit. Misalnya, memasukkan aluminium nitrida ke dalam komposit epoksi sebagian memberikan keuntungan dalam penanganan termal, meskipun tingkat konduktivitasnya tidak sebanding dengan bahan keramik padat. Perpaduan sifat material ini sangat penting dalam kemasan elektronik, karena diperlukan konduktor listrik yang sangat baik yang mampu menarik cukup panas dari inti chip untuk mencegah gangguan pada kinerja sinyal.

Berlian, terkenal karena kekerasannya yang ekstrem, menonjol sebagai konduktor dan isolator termal yang patut dicontoh. Bahan polimer seperti Teflon (Polytetrafluoroethylene, atau PTFE), meskipun kurang konduktif dibandingkan keramik atau berlian, masih mengungguli banyak plastik dalam kemampuannya menghantarkan panas dan menawarkan insulasi listrik yang andal. PTFE cukup efektif untuk digunakan sebagai bahan pelapis dalam aplikasi intensif panas seperti peralatan masak.

Kaca, porselen, dan keramik padat lainnya memiliki sifat isolasi dan konduksi panas yang sama. Mereka memberikan solusi praktis, terutama dalam kasus di mana isolator listrik yang baik juga diperlukan untuk mengelola panas. Aluminium nitrida (AlN) digunakan sebagai isolator pada perangkat semikonduktor, menjembatani kesenjangan antara cetakan dan komponen perpindahan panas. Meskipun tidak konduktif secara termal seperti berilium oksida, AlN menawarkan alternatif yang lebih aman dan hemat biaya. Selain itu, AlN melampaui isolator standar seperti mika, polimida, dan alumina dalam hal manajemen termal.

Safir sintetis juga patut mendapat perhatian karena harganya yang terjangkau dan mudah dibentuk dalam berbagai bentuk, menjadikannya pemain berharga lainnya dalam bidang pengemasan semikonduktor. Masing-masing material ini menghadirkan keunggulan unik dalam desain kemasan yang mengutamakan pengendalian panas tanpa mengganggu kinerja elektronik.

Meskipun material canggih seperti berlian dan aluminium nitrida berada di garis depan dalam mengatasi tantangan termal pada perangkat semikonduktor, tidak semua solusi memerlukan komponen yang eksotik atau kaku. Gemuk dan perekat termal berfungsi sebagai jaringan ikat dalam kemasan elektronik, mengisi celah kecil atau ketidakteraturan permukaan dan memfasilitasi perpindahan panas antar komponen dengan topografi yang bervariasi. Kemampuannya untuk menyesuaikan diri dengan permukaan memberikan pelengkap penting bagi solusi manajemen termal yang lebih solid, sehingga membentuk pendekatan komprehensif terhadap pembuangan panas. Dengan fokus pada peningkatan bahan-bahan ini, para peneliti bertujuan untuk meningkatkan sifat konduktivitas termalnya, menjadikannya mitra yang lebih efektif dalam paradigma pengelolaan panas.

“Gemuk termal dan perekat termal bersifat konduktif terhadap panas,” tambah Fromm, “Tetapi jika dibandingkan dengan material seperti keramik pada umumnya yang bersifat konduktif terhadap panas, bahan-bahan ini merupakan konduktor yang buruk sepuluh kali lipat. Bahan-bahan ini tidak begitu bagus, dan ada alasan fisik dan kimia yang menyebabkannya. Ada banyak keuntungan yang bisa dicapai di sana, dan ada banyak pekerjaan yang dilakukan di bidang itu.”

Melihat ke depan

Seiring dengan material baru yang membuka jalan bagi pelepasan panas, teknik pendinginan baru yang inovatif juga sedang dikembangkan. Saluran mikro silikon, yang merupakan jalur skala mikro yang terukir pada substrat, dapat mengarahkan cairan pendingin langsung ke jantung titik panas. Metode pendinginan langsung ini lebih unggul dibandingkan heatsink tradisional namun menawarkan tantangan dalam desain, perakitan, dan keandalan.

Demikian pula, pengembangan sistem pendingin cair loop tertutup dapat memungkinkan komponen tetap dingin tanpa kendala yang disebabkan oleh metode aliran udara. Sistem ini menjanjikan suhu operasional yang lebih dingin tanpa ancaman pelambatan termal, namun masih banyak penelitian yang harus dilakukan baik dalam desain maupun penanganan proses untuk sistem pendingin cair.

Pilihan lainnya adalah dengan membalikkan struktur tumpukan dadu, jadi alih-alih meletakkan memori di atas logika, logika diletakkan di atas memori dengan heat sink di atasnya. Winbond, misalnya, menyarankan hal ini dengan teknologi elemen ultra-bandwidth (CUBE) yang disesuaikan, sebuah pendekatan berkinerja tinggi yang menumpuk cetakan atas SoC langsung ke memori, yang kemudian dipasang ke media menggunakan vias silikon tembus. Pendekatannya, menurut CS Lin, eksekutif pemasaran di winbond, menggunakan lebih sedikit daya, sehingga mengurangi panas. Selain itu, hal ini memungkinkan panas untuk dihilangkan secara langsung, daripada menyalurkannya melalui labirin komponen heterogen.

Pilihan lainnya adalah menggunakan manajemen termal real-time yang didukung oleh AI. Algoritma kini dapat memantau suhu di berbagai lokasi on-chip, mengarahkan sumber daya pendinginan secara dinamis, memastikan kinerja optimal tanpa melewati garis merah termal. ProteanTecs, misalnya, baru saja meluncurkan solusi yang ditujukan untuk pusat data yang dikatakan dapat menurunkan daya di server dengan mengurangi jumlah pelindung yang diperlukan untuk melindungi chip dari panas berlebih. Pendekatan ini bergantung pada pemantauan perubahan dari dalam sebuah chip dan memberikan penyesuaian sesuai kebutuhan.

Synopsys dan Siemens EDA juga memiliki solusi untuk memantau berbagai aktivitas dan perubahan suhu menggunakan sensor internal. Mampu memperoleh pembacaan dari dalam paket menggunakan telemetri merupakan komponen yang semakin penting dalam mengelola panas.

“Anda memiliki konstruksi mekanis chip pada chip dan interposer dengan ribuan atau jutaan benjolan mikro, dan semuanya mengembang dan berkontraksi saat chip memanas,” tambah Swinnen. “Bergantung pada peta termal Anda, integritas daya Anda harus beradaptasi dengan profil suhu lokal secara real time. Anda dapat menghitung berapa banyak daya yang dihasilkan sebuah chip, tetapi suhu yang dihasilkannya bergantung pada apa yang dihasilkannya. Apakah diletakkan di atas piring yang dingin, atau diletakkan di bawah sinar matahari di Sahara? Chip yang sama dan aktivitas yang sama dapat menyebabkan suhu yang sangat berbeda tergantung pada lingkungannya.”

Selain itu, penelitian terhadap material pengubah fasa, yang menyerap panas dengan mengubah wujudnya, menjanjikan pengaturan suhu yang pasif namun kuat. Terlebih lagi, eksplorasi sistem pendingin biologis, yang mencoba meniru respons tubuh manusia terhadap panas, menandakan masa depan di mana perangkat kita dapat menghilangkan panas secara intuitif seperti yang kita lakukan.

Kesimpulan

Ketika industri semikonduktor terus mendorong batas-batas kinerja dan integrasi, manajemen termal dalam kemasan canggih masih menjadi tantangan. Di satu sisi spektrum, meningkatnya kompleksitas termal muncul ketika perusahaan beralih ke modul multi-chip yang lebih padat. Sebaliknya, kemajuan dalam ilmu material dan teknologi pendinginan inovatif berupaya mengurangi tekanan termal yang diakibatkannya. Keduanya diperlukan untuk mengatasi tantangan termal yang kompleks, namun masih banyak pekerjaan yang harus dilakukan untuk menyelesaikannya dengan cara yang konsisten dan dapat diprediksi.

- Ed Sperling berkontribusi untuk laporan ini.

Bacaan Terkait

Mengelola Stres yang Diinduksi Termal di Chips

Integrasi heterogen dan peningkatan kepadatan pada node tingkat lanjut menciptakan beberapa tantangan yang kompleks dan sulit untuk pembuatan dan pengemasan IC.

- Konten Bertenaga SEO & Distribusi PR. Dapatkan Amplifikasi Hari Ini.

- PlatoData.Jaringan Vertikal Generatif Ai. Berdayakan Diri Anda. Akses Di Sini.

- PlatoAiStream. Intelijen Web3. Pengetahuan Diperkuat. Akses Di Sini.

- PlatoESG. Karbon, teknologi bersih, energi, Lingkungan Hidup, Tenaga surya, Penanganan limbah. Akses Di Sini.

- PlatoHealth. Kecerdasan Uji Coba Biotek dan Klinis. Akses Di Sini.

- Sumber: https://semiengineering.com/navigating-heat-in-advanced-packaging/

- :memiliki

- :adalah

- :bukan

- :Di mana

- $NAIK

- 1

- 10

- 12

- 25

- 3d

- 8

- a

- kemampuan

- Sanggup

- Tentang Kami

- dipercepat

- diterima

- Menurut

- Mencapai

- dicapai

- di seluruh

- kegiatan

- menyesuaikan

- menambahkan

- tambahan

- Tambahan

- Selain itu

- alamat

- dialamatkan

- Menambahkan

- Perekat

- menyesuaikan

- penyesuaian

- maju

- Materi canggih

- kemajuan

- keuntungan

- mempengaruhi

- lagi

- Penuaan

- silam

- di depan

- AI

- tujuan

- ditujukan

- UDARA

- sama

- algoritma

- Semua

- meringankan

- mengizinkan

- memungkinkan

- ALN

- sepanjang

- juga

- alternatif

- Meskipun

- selalu

- jumlah

- an

- analisis

- dan

- Lain

- Apa pun

- aplikasi

- pendekatan

- ADALAH

- daerah

- sekitar

- AS

- aspek

- Majelis

- menilai

- At

- atom

- melampirkan

- Mencoba

- perhatian

- otonom

- kendaraan otonom

- jauh

- kembali

- seimbang

- berdasarkan

- BE

- karena

- menjadi

- menjadi

- menjadi

- menjadi

- sebelum

- makhluk

- Manfaat

- Lebih baik

- antara

- Luar

- Terbesar

- Campuran

- Obligasi

- kedua

- batas-batas

- Melanggar

- menjembatani

- Membawa

- membangun

- beban

- bisnis

- pengembangan bisnis

- tapi

- by

- menghitung

- CAN

- kemampuan

- menangkap

- kasus

- Kategori

- melayani

- Menyebabkan

- kenamaan

- pusat

- Pusat

- pusat

- tertentu

- menantang

- tantangan

- menantang

- perubahan

- berubah

- Perubahan

- mengubah

- memeriksa

- kimia

- bahan kimia

- keping

- Keripik

- pilihan

- memilih

- Penyelesaian

- dingin

- Kolektif

- kolektif

- bagaimana

- datang

- masyarakat

- Perusahaan

- dibandingkan

- cocok

- Melengkapi

- kompleks

- kompleksitas

- kompleksitas

- compliant

- rumit

- komponen

- komponen

- luas

- kompromi

- menghitung

- Perhatian

- Kekhawatiran

- Kondisi

- Mengadakan

- daya konduksi

- konduktor

- Terhubung

- pertimbangan

- mengingat

- konsisten

- kendala

- konstruksi

- konsumen

- elektronik konsumen

- kontak

- terus

- kontrak

- berkontribusi

- mengendalikan

- mendekut

- dingin

- Tembaga

- Timeline

- hemat biaya

- mahal

- bisa

- Mitra

- kovalen

- membuat

- kritis

- penyeberangan

- sangat penting

- disesuaikan

- kerusakan

- data

- Data Center

- Pusat Data

- David

- berurusan

- keputusan

- tuntutan

- padat

- kepadatan

- Tergantung

- tergantung

- Mendesain

- proses desain

- dirancang

- perancang

- desainer

- desain

- diinginkan

- Meskipun

- rinci

- terperinci

- rincian

- mengembangkan

- Pengembangan

- pembangunan

- alat

- Devices

- iblis

- Diamond

- Mati

- berbeda

- sulit

- digital

- langsung

- Mengarahkan

- langsung

- Kepala

- diskusi

- jarak

- mendistribusikan

- distribusi

- do

- tidak

- Tidak

- dilakukan

- Dont

- kiamat

- turun

- gambar

- menarik

- mendorong

- dua

- selama

- dinamis

- setiap

- Terdahulu

- Mudah

- ed

- Efektif

- efektif

- efek

- efisiensi

- efisien

- Elektronik

- Elektronik

- elemen

- lain

- tertanam

- muncul

- dipekerjakan

- memungkinkan

- akhir

- direkayasa

- Teknik

- Insinyur

- mempertinggi

- meningkatkan

- cukup

- memastikan

- memastikan

- Seluruh

- amplop

- terutama

- penting

- Bahkan

- peristiwa

- Setiap

- segala sesuatu

- berkembang

- contoh

- melebihi

- unggul

- pengecualian

- kelebihan

- eksekutif

- Direktur Eksekutif

- menunjukkan

- Eksotik

- Lihat lebih lanjut

- perluasan

- mengharapkan

- diharapkan

- mahal

- ahli

- eksplorasi

- memperpanjang

- memperpanjang

- tingkat

- ekstrim

- Menghadapi

- memfasilitasi

- faktor

- Gagal

- kegagalan

- Kegagalan

- jauh

- Fitur

- bidang

- Ara

- Angka

- pikir

- terisi

- pengisian

- temuan

- aliran

- Fokus

- Untuk

- garis terdepan

- bentuk

- pembentukan

- bentuk

- sebagainya

- ditemukan

- dari

- sepenuhnya

- fungsi

- fungsi

- fungsi

- mendasar

- masa depan

- celah

- kesenjangan

- generasi

- generatif

- AI generatif

- George

- mendapatkan

- diberikan

- Go

- akan

- baik

- mendapat

- gradien

- tangan

- Penanganan

- Kejadian

- Sulit

- Memanfaatkan

- Memiliki

- he

- Hati

- ketinggian

- membantu

- High

- kinerja tinggi

- lebih tinggi

- engsel

- PANAS

- Seterpercayaapakah Olymp Trade? Kesimpulan

- How To

- HTTPS

- manusia

- i

- IBM

- ide

- mengidentifikasi

- mengidentifikasi

- if

- Dampak

- imperatif

- penting

- Dikenakan

- ditingkatkan

- meningkatkan

- in

- memasukkan

- termasuk

- Termasuk

- menggabungkan

- Pada meningkat

- meningkatkan

- makin

- industri

- inheren

- Innovation

- inovatif

- dalam

- contoh

- sebagai gantinya

- terpadu

- Mengintegrasikan

- integrasi

- integritas

- dimaksudkan

- Antarmuka

- gangguan

- mengganggu

- intern

- ke

- rumit

- melibatkan

- isu

- masalah

- IT

- NYA

- Diri

- jpg

- hanya

- kunci

- Tahu

- labirin

- sebagian besar

- Terbaru

- Hukum

- lapisan

- memimpin

- Memimpin

- meninggalkan

- LEND

- kurang

- Tingkat

- adalah ide yang bagus

- leveraging

- siklus hidup

- pengangkatan

- 'like'

- pembatasan

- keterbatasan

- Terbatas

- batas

- lin

- baris

- Cair

- memuat

- lokal

- lokasi

- logika

- lagi

- Lot

- Rendah

- menurunkan

- terbuat

- memelihara

- membuat

- Membuat

- mengelola

- pengelolaan

- manajer

- pelaksana

- Produsen

- pabrik

- banyak

- peta

- Marketing

- massa

- Cocok

- bahan

- bahan

- max-width

- Mungkin..

- mekanis

- kenangan

- Memori

- Logam

- metode

- metodologi

- metode

- Mika

- mungkin

- jutaan

- minor

- menit

- meringankan

- mencampur

- mobilitas

- mode

- pemodelan

- modul

- Modul

- Memantau

- pemantauan

- monitor

- Monolitis

- lebih

- paling

- banyak

- multi-disiplin

- beberapa

- harus

- nasional

- Alam

- menavigasi

- kebutuhan

- Perlu

- dibutuhkan

- kebutuhan

- tak pernah

- New

- baru saja

- berikutnya

- tidak

- node

- tidak ada

- novel

- sekarang

- jumlah

- of

- menawarkan

- Penawaran

- sering

- on

- ONE

- hanya

- operasi

- operasional

- seberang

- optimasi

- Optimize

- optimal

- pilihan

- Opsi

- or

- Lainnya

- kami

- di luar

- keluaran

- lebih

- secara keseluruhan

- Mengatasi

- pak

- paket

- dikemas

- paket

- pengemasan

- penuh sesak

- panel

- diskusi panel

- pola pikir

- terpenting

- bagian

- khususnya

- rekan

- bagian

- pasif

- jalan

- jalur

- mengaspal

- prestasi

- tahap

- fisik

- bagian

- pilar

- sangat penting

- Tempat

- ditempatkan

- plastik

- plato

- Kecerdasan Data Plato

- Data Plato

- pemain

- polimer

- ampuh

- kekuasaan

- didukung

- Praktis

- meramalkan

- Bisa ditebak

- Prematur

- hadiah

- presiden

- mencegah

- penentuan prioritas

- mungkin

- Masalah

- proses

- diproses

- proses

- pengolahan

- prosesor

- Produk

- Profil

- profil

- program

- janji

- menjanjikan

- properties

- melindungi

- memberikan

- menyediakan

- menyediakan

- Dorong

- menempatkan

- Puting

- R & D

- meningkatkan

- pemeliharaan

- ramping

- jarak

- Tarif

- agak

- nyata

- real-time

- realistis

- realisasi

- benar-benar

- alasan

- baru

- diakui

- mengenali

- Merah

- menurunkan

- mengurangi

- mengurangi

- mengurangi

- mengenai

- Regulasi

- keandalan

- dapat diandalkan

- bantuan

- sisa

- menghapus

- Dihapus

- melaporkan

- merupakan

- membutuhkan

- wajib

- kebutuhan

- membutuhkan

- penelitian

- peneliti

- menyelesaikan

- Sumber

- tanggapan

- resultan

- dihasilkan

- membalikkan

- benar

- kaku

- Bangkit

- Risiko

- peta jalan

- Terguling

- Rute

- Run

- s

- lebih aman

- Tersebut

- sama

- mengatakan

- Skala

- skala

- skema

- ILMU PENGETAHUAN

- ilmuwan

- mulus

- melihat

- terlihat

- ruas

- semikonduktor

- Semikonduktor

- senior

- sensor

- melayani

- server

- beberapa

- Bentuknya

- Share

- bergeser

- bergeser

- Pendek

- sisi

- Siemens

- Sinyal

- sinyal

- penting

- signifikan

- Silikon

- mirip

- Sederhana

- hanya

- sejak

- tunggal

- Duduk

- situasi

- Ukuran

- ukuran

- Perlahan

- kecil

- So

- padat

- larutan

- Solusi

- MEMECAHKAN

- beberapa

- sesuatu

- sumber

- sumber

- Space

- Spektrum

- penyebaran

- tumpukan

- ditumpuk

- menumpuk

- Tumpukan

- Tahap

- standar

- berdiri

- Negara

- Negara

- tinggal

- Masih

- strategi

- kekuatan

- tekanan

- berjuang

- kuat

- struktur

- selanjutnya

- seperti itu

- matahari

- unggul

- Permukaan

- melampaui

- melampaui

- bertahan

- sinergis

- sistem

- sistem

- mengatasi

- target

- teknik

- Teknologi

- Teknologi

- sepuluh

- mengerikan

- dari

- bahwa

- Grafik

- Sumber

- mereka

- Mereka

- kemudian

- Sana.

- panas

- Ini

- mereka

- berpikir

- Pikir

- ini

- itu

- meskipun?

- pikir

- ribuan

- ancaman

- tiga dimensi

- Melalui

- di seluruh

- waktu

- tisu

- untuk

- bersama

- terlalu

- alat

- puncak

- terhadap

- tradisional

- transfer

- perjalanan

- dahsyat

- mencoba

- mencoba

- MENGHIDUPKAN

- dua

- khas

- Akhirnya

- bawah

- memahami

- pemahaman

- sayangnya

- unik

- UPS

- upside

- menggunakan

- kasus penggunaan

- bekas

- kegunaan

- menggunakan

- dimanfaatkan

- Memanfaatkan

- Berharga

- berbagai

- bervariasi

- Kendaraan

- vendor

- secara vertikal

- sangat

- wakil

- Wakil Presiden

- View

- ingin

- Hangat

- adalah

- Cara..

- cara

- we

- BAIK

- adalah

- Apa

- Apa itu

- ketika

- apakah

- yang

- sementara

- mengapa

- akan

- dengan

- dalam

- tanpa

- Kerja

- kerja

- lebih buruk

- Salah

- tahun

- namun

- Menghasilkan

- kamu

- Anda

- zephyrnet.dll